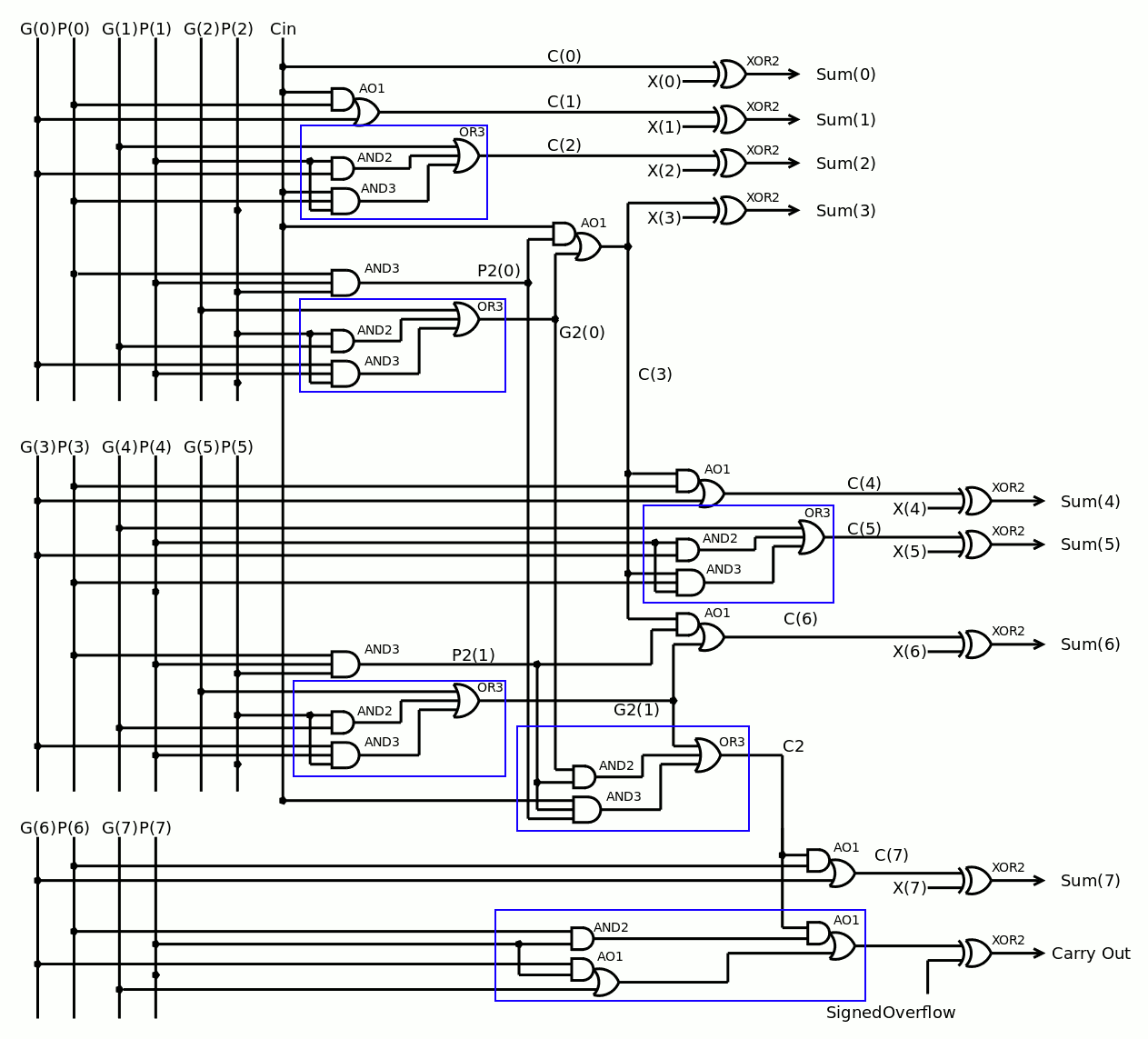

La porte XOR est essentielle à l'addition mais une autre se retrouve beaucoup dans un "carry lookahead adder" lorsqu'il n'est pas possible de fabriquer une carry chain optimisée. C'est une macro-cellule appelée CLA3 dans les projets #YGREC8 et #LibreGates.

Ce circuit a été optimisé pour travailler avec des portes logiques à 3 entrées et les signaux Propagate et Generate sont décrits autre séparément, intégrés dans l'unité logique/ROP2.

Il y a déjà 6 unités CLA3 dans un additionneur 8 bits donc c'est un bon candidat pour une optimisation. Nous pouvons partir du circuit présenté dans le log Expansion des portes logique en cmos en modifiant le circuit aoai_3_2_1.

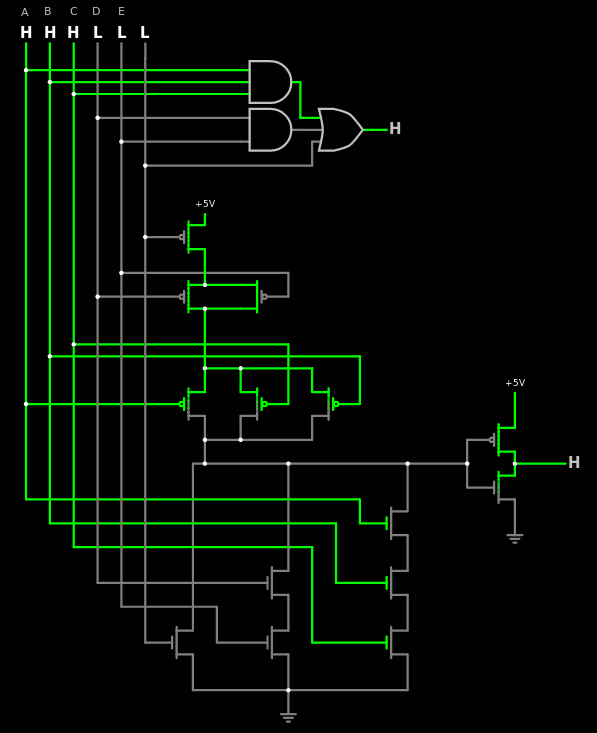

Cela donne le circuit suivant :

À partir de là il suffit de mettre une entrée en commun, ce qui se simplifie avec une petite modification de la topologie des transistors.

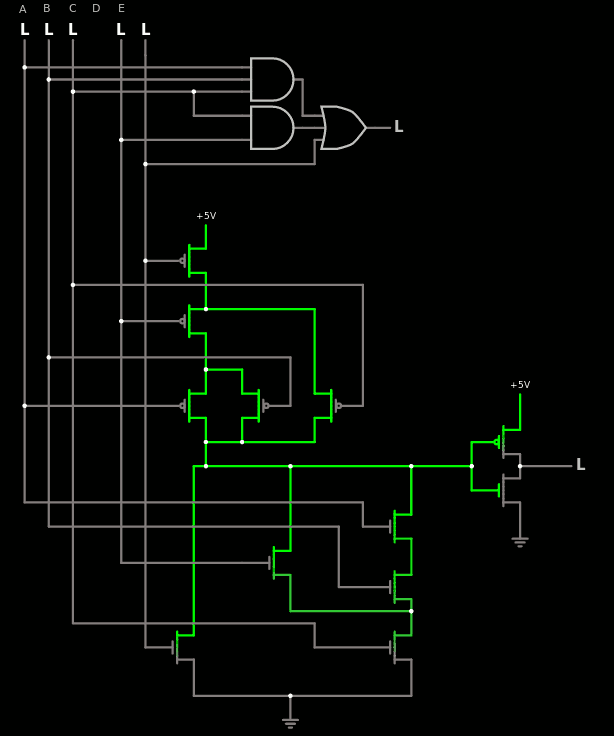

Cela donne ce circuit un peu plus petit :

Cette version contient 12 transistors, dont 2 pour l'inverseur en sortie, ce qui lui permet d'attaquer un fanout de 2 ou 3 sans difficulté. Cependant dans deux cas sur le schéma du début, la sortie attaque une seule entrée donc une autre version sans inverseur est possible (ce qui donne CLA3I). En aval, il faut alors faire du "bubble push".

Yann Guidon / YGDES

Yann Guidon / YGDES

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.