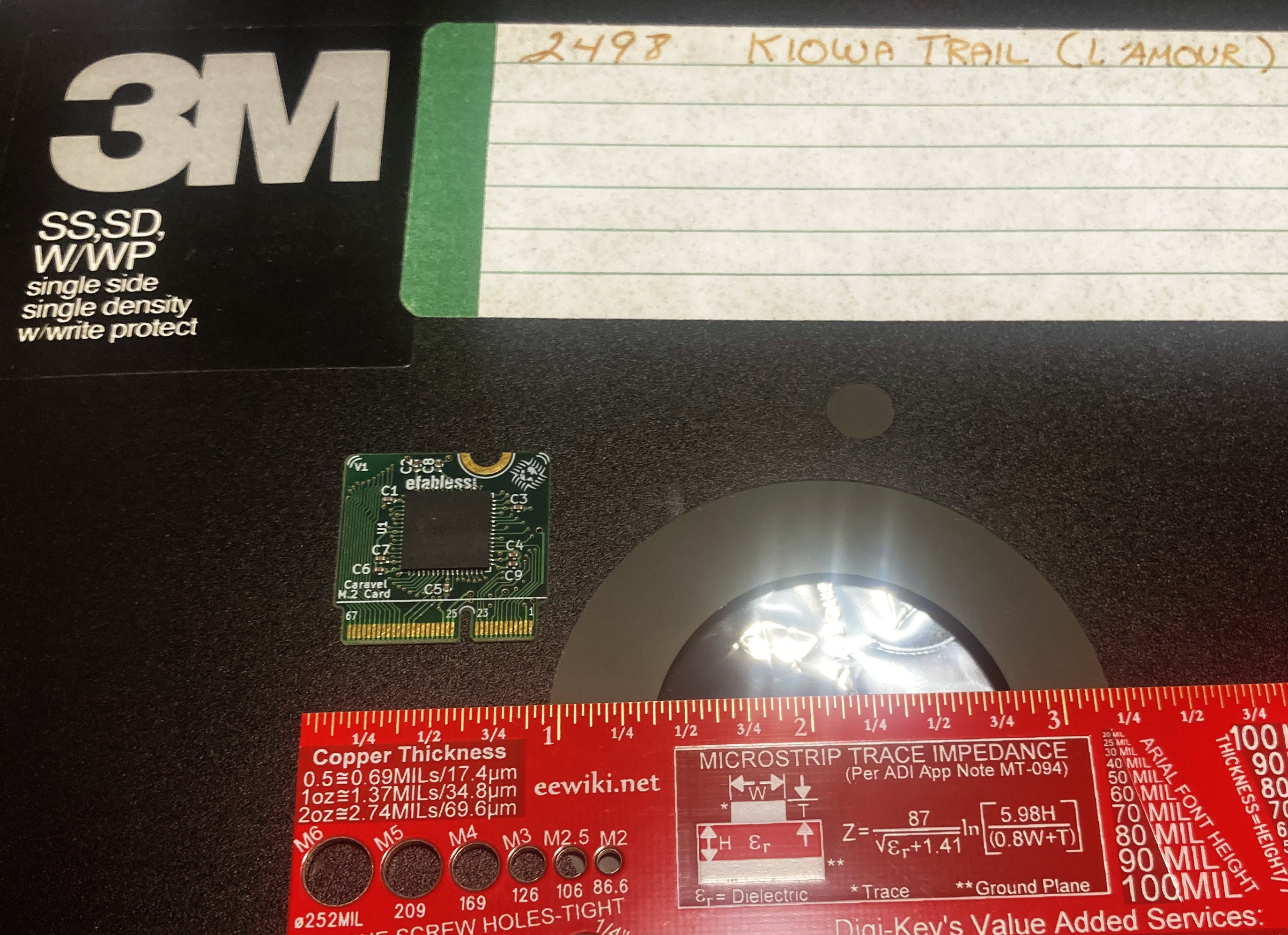

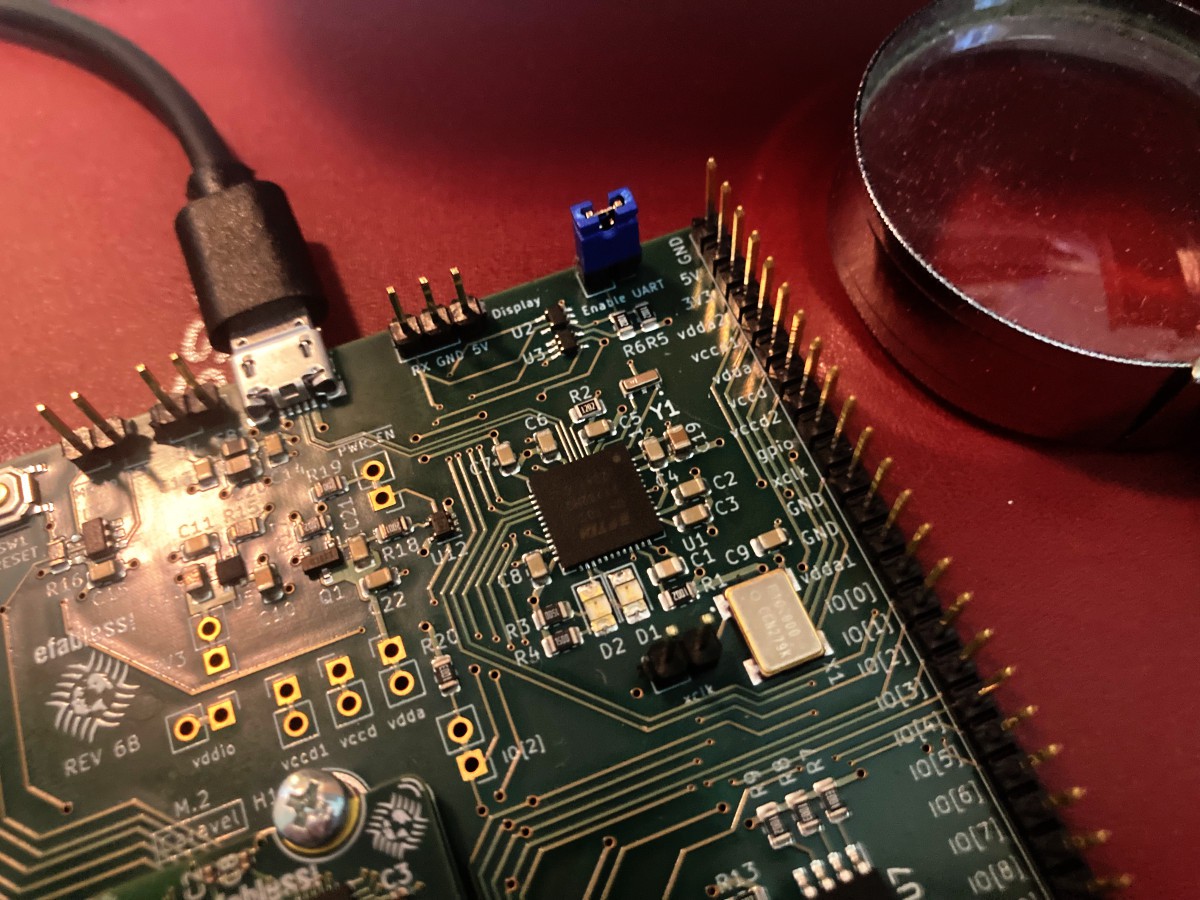

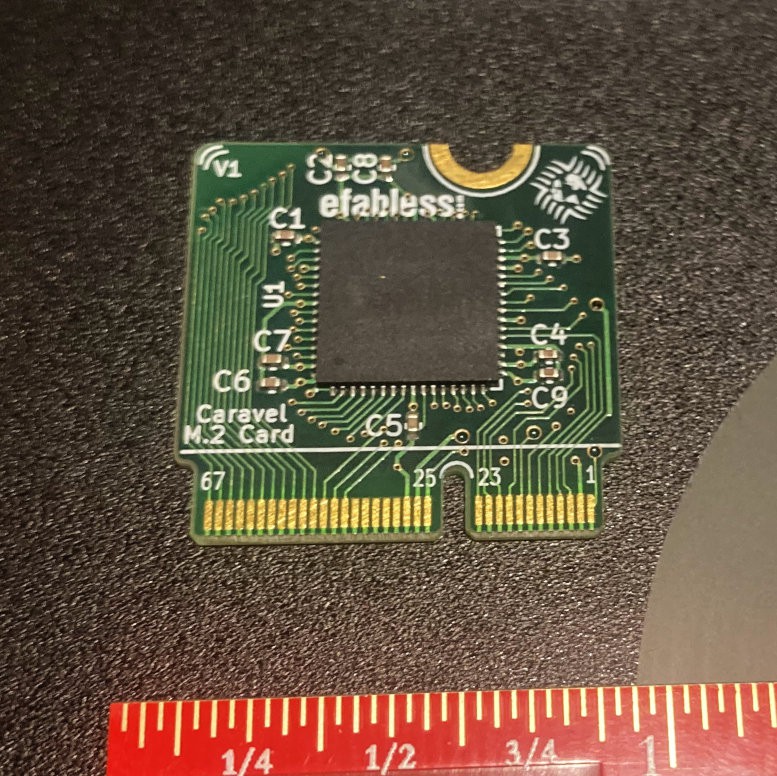

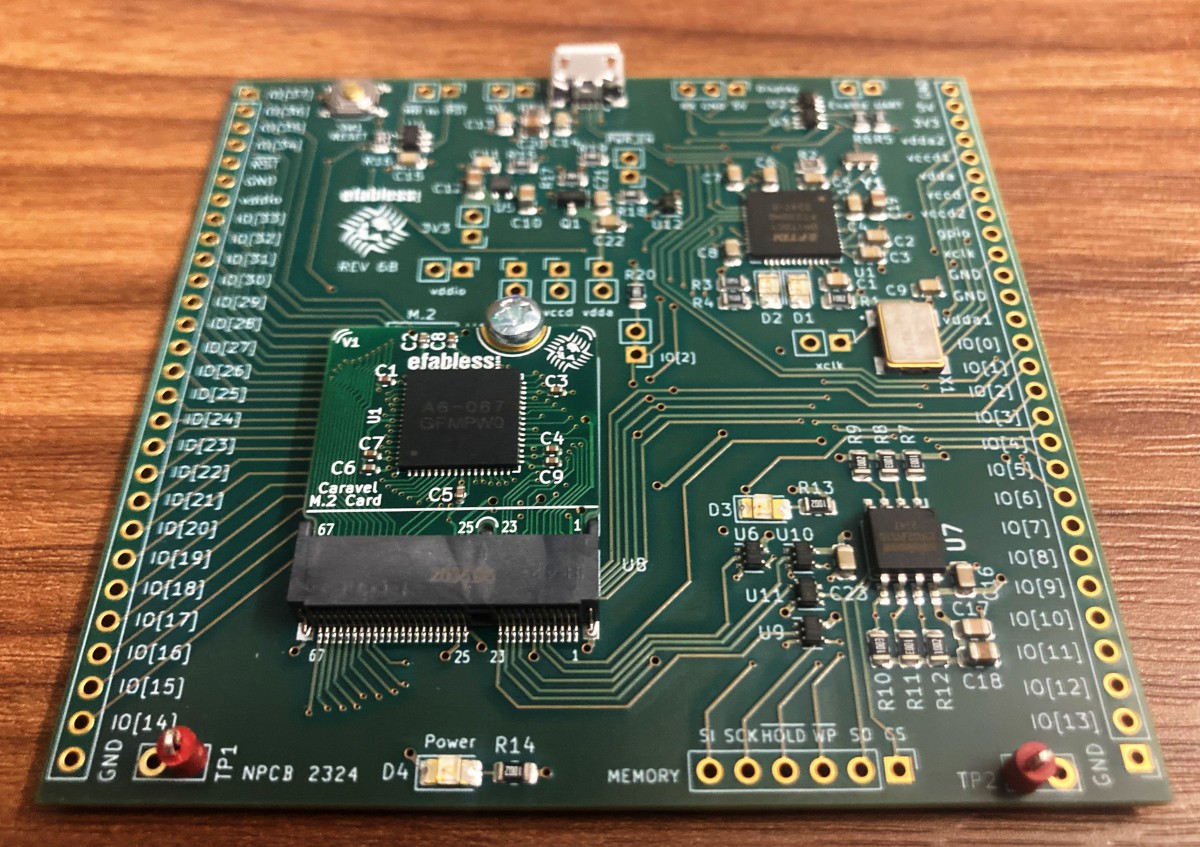

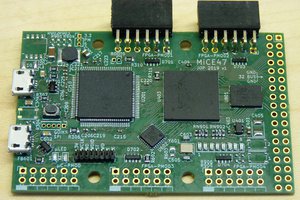

Efabless daughter-board with Caravel chip uses edge connector that is called "M.2 Keyed E" (it's SparkFun's MicroMod form-factor, but with totally different pinout):

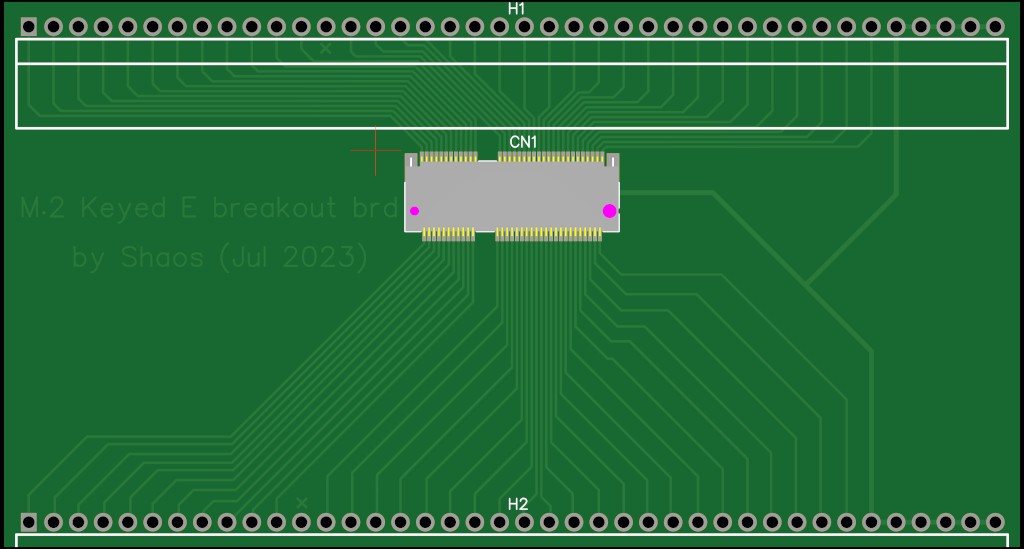

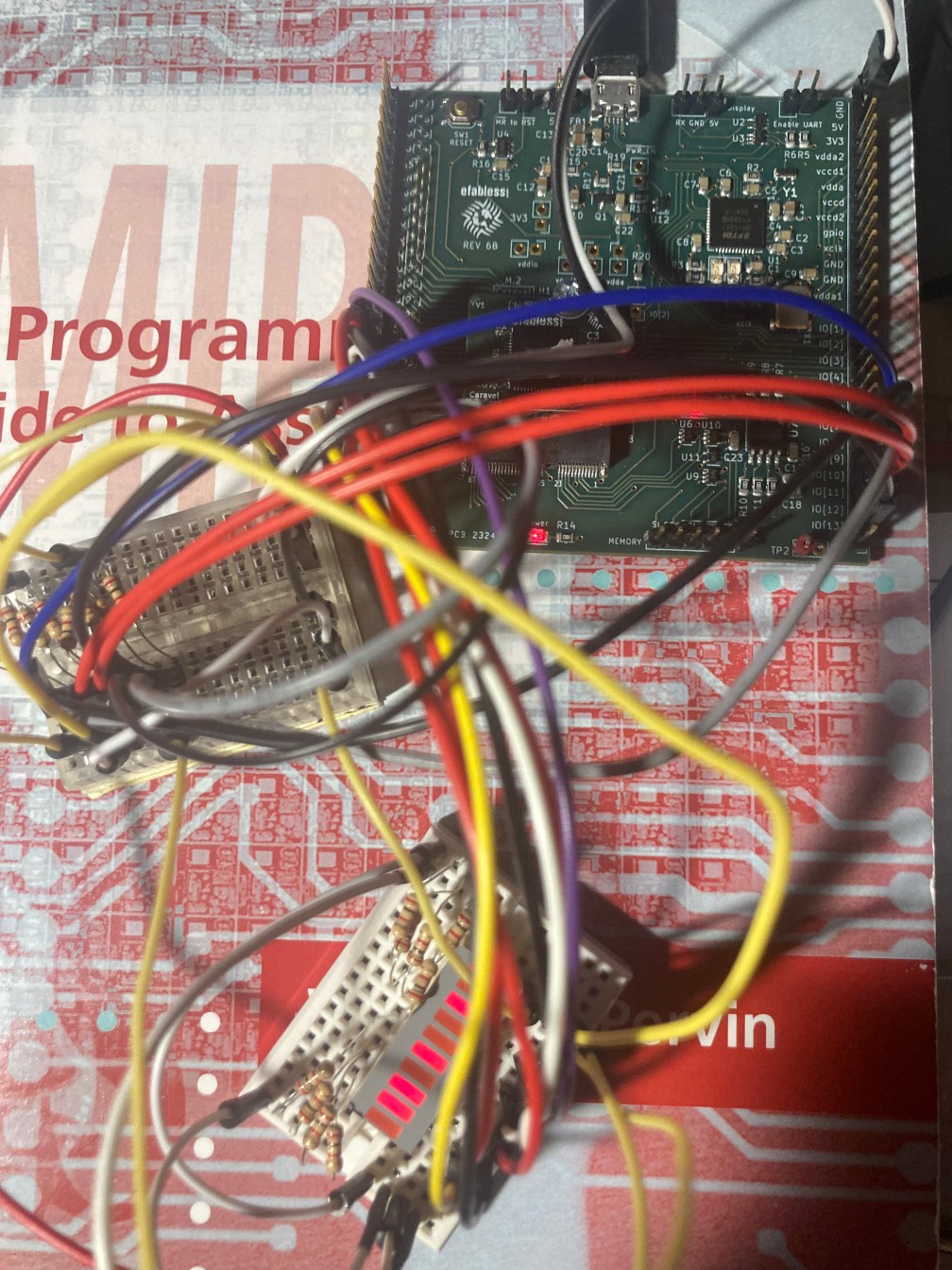

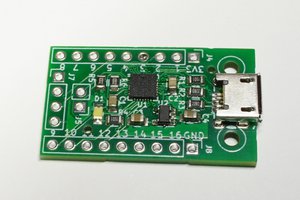

To play with it those chips (I have a few) I decided to make a breakout board with proper connector pre-soldered by PCB manufacturer:

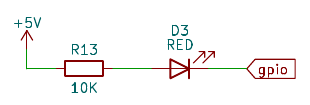

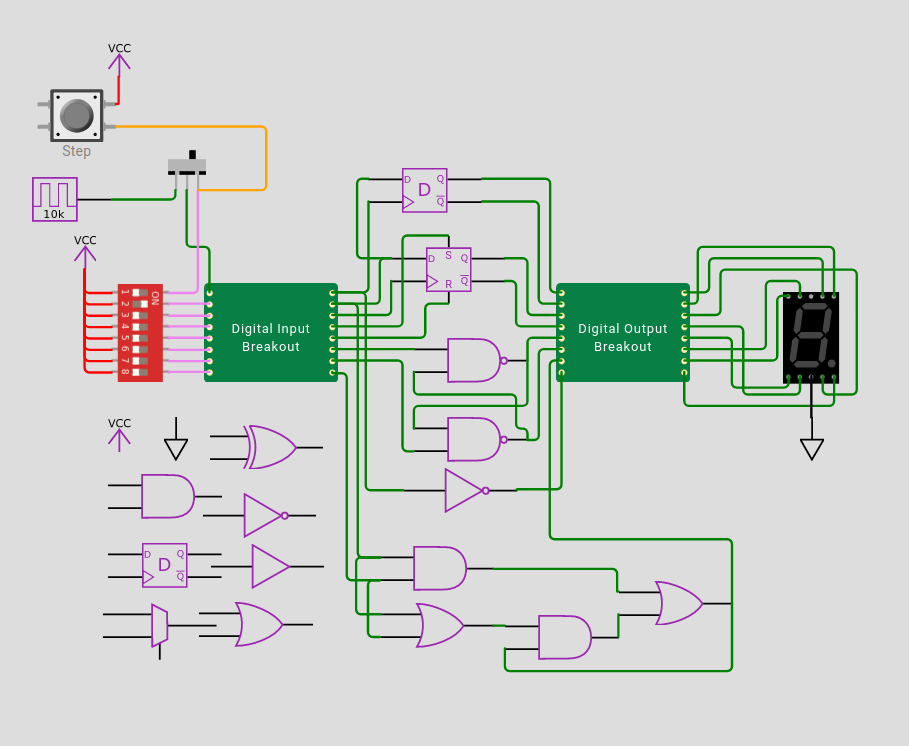

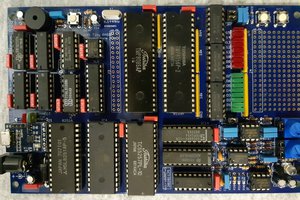

Plan is to use one or more Caravel chips to build a usable computer (codename "Marina") that may help to debug 5V digital electronics (including retrocomputers and old microprocessors). I expect a lot of fun here :)

SHAOS

SHAOS

Anders Hjelm

Anders Hjelm

Julien

Julien

/me grabs a truckload of popcorn