Hello, I'm back.

A Logic Analyzer is an indispensable tool for debugging electronic circuits, and Felini will have this feature. Most of the logic analyzers currently not made by Saleae use fx2lafw, running on the FX2 chip series with the GPIF peripheral. This peripheral allows direct data transmission from GPIO to USB, without involving the CPU. As a result, the FX2 with an 8051 core still delivers remarkable results. Due to the USB bandwidth limitations, logic analyzers running the fx2lafw firmware are capped at 24MHz. Unlike the FX2, the ESP32 lacks GPIF; however, in theory, the ESP32S3 can capture at up to 80MHz (maximum), which is the goal I am striving to achieve. Felini LA will work with the open-source software Sigrok PulseView, using the SUMP protocol to transmit data over USB CDC in the background. To be honest, I wish to implement a different protocol on the ESP32S3, allowing it to maximize the hardware USB speed and have liveview capture capabilities. However, time constraints do not permit me to do so.

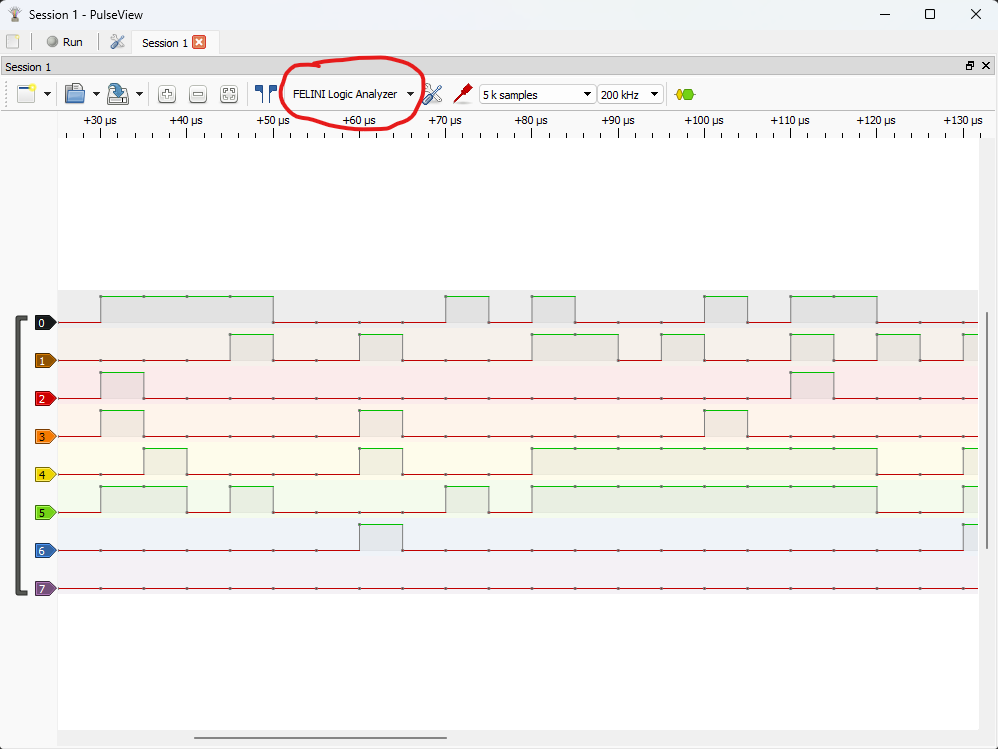

Additionally, the number of samples and channels also need to be considered. Based on my own experience, I will prioritize the number of samples over the sampling frequency. Below is an update on progress and achievements: Pulse has recognized Felini and is operating at a relatively low speed.

Chu Tien Thinh (obitvn)

Chu Tien Thinh (obitvn)

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.