The building of this machine is detailed in the YouTube playlist here:

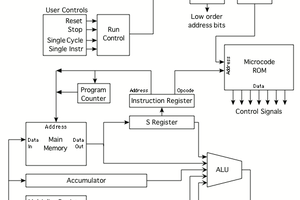

The architecture is centered around the W-Bus, which is simply 8 parallel wires, but it's the means by which all the functional units communicate with each other.

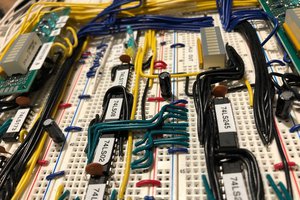

The SAP-1 had the output register which connected to the W-Bus, but we need additional storage for registers such as index X, index Y, the stack pointer, the status register, effective address registers and so forth. Thus a number of octal D-type flip-flops (74HC574) have both their input and output connected to the W-bus.

Next the sequencer is expanded from 16-bits wide to 40-bits wide. Many of these signals are required for the more complex ALU and status register compared to the SAP-1. I use both horizontal and vertical microcoding here. The lower 8-bits are fed into some 74HC138s which have their outputs latched and feed mostly the register bank clock and output enable signals.

It is still address by the instruction register and a resettable step-counter (5-bits wide) and a 1-bit status input.

ammarbhayat28

ammarbhayat28

Ced

Ced

zpekic

zpekic