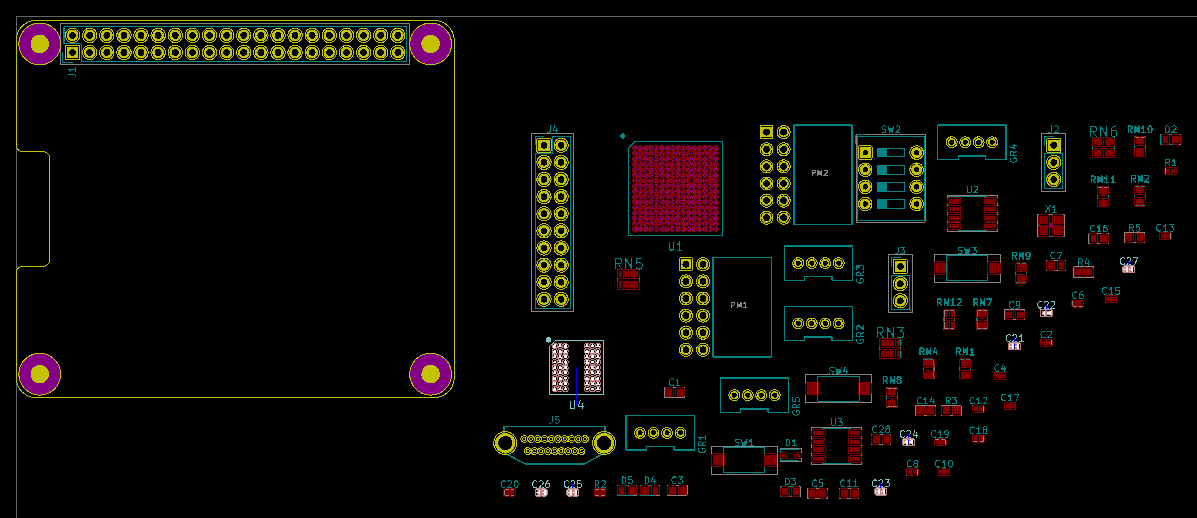

In my last log, I had the SKiDL-generated netlist imported into an RPi HAT template. The problem with that is PCBNEW initially places all the parts pretty much any way it wants. That means you have to pick through a pile of parts to find which ones go with which. As an example, I highlighted (in white) the SDRAM chip and its bypass caps:

My solution for this problem was two-fold:

- Since SKiDL descriptions are just programs with a natural hierarchy, I modified SKiDL to pass that hierarchy to PCBNEW by embedding it into the sheetpath fields of the netlists it generates.

- Then I wrote a plugin for PCBNEW that would group and arrange the parts to reflect their position within that hierarchy.

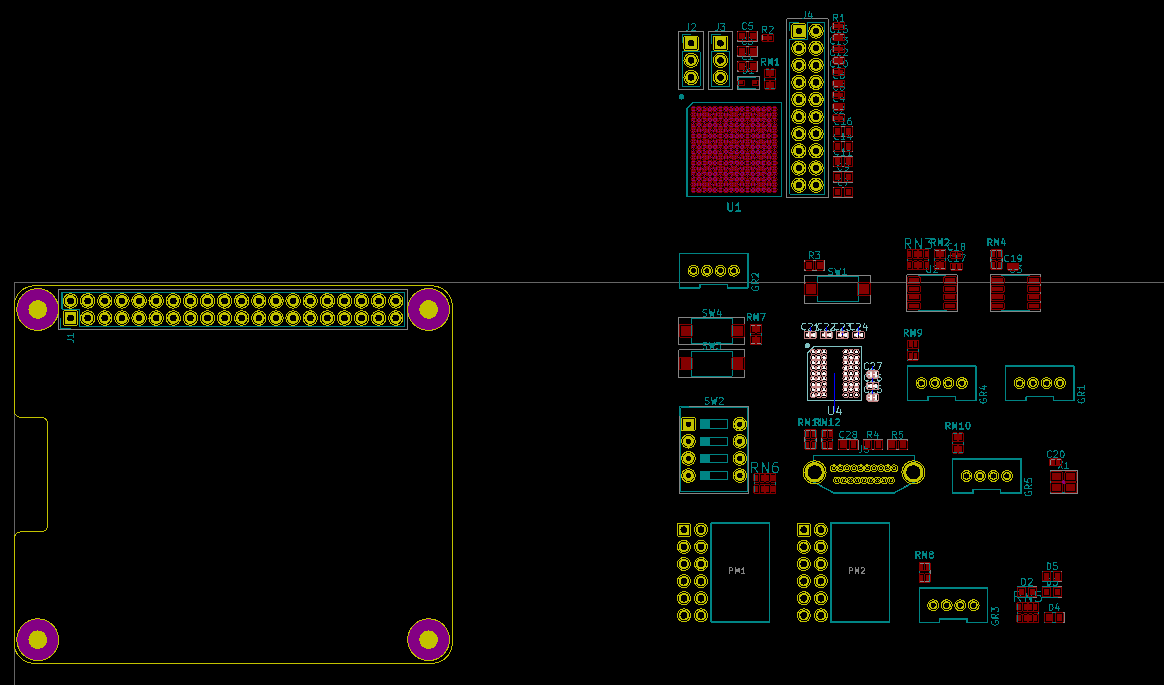

With those two items in place, the relationships between the parts becomes much clearer. Here's the placement of the SDRAM and its bypass caps now:

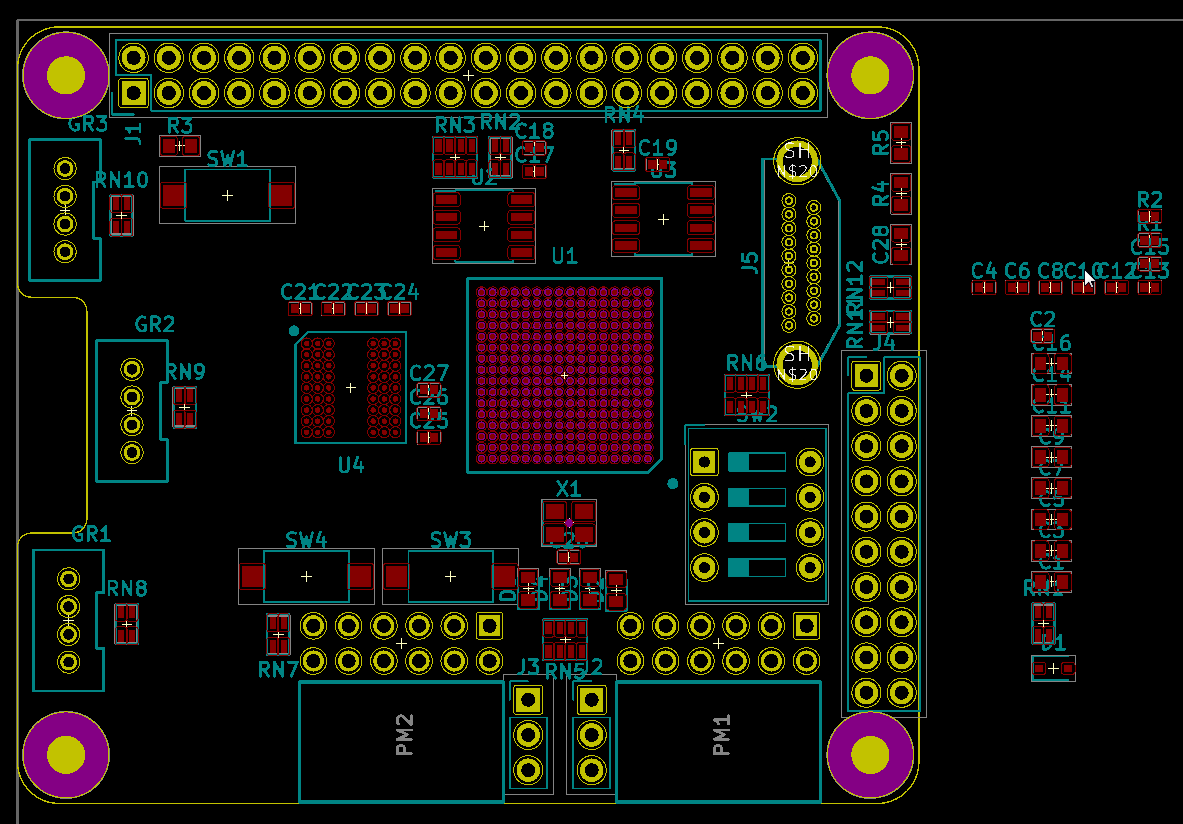

After that, I was able to create an initial, rough placement for the CAT Board:

I still have to design the +3.3V and +1.2V voltage regulator circuits. After those are done, I can begin the detailed placing and routing.

Dave Vandenbout

Dave Vandenbout

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.