-

Updates

01/29/2021 at 03:57 • 1 commentIt's been nearly 2 years since my last log, and things are quite different from where I left it. I've been poking around at this project in between other projects and university, so most of these details are not recent. I found out that there has since been some work-in-progress commits on the coreboot Gerrit (link) for another GM45 + DDR2 laptop. Some of the patches related to that included DDR2 ram initialization code, so I no longer have to worry about that task. I tried building and flashing coreboot with some of those patches, and to my surprise, the system actually booted!

However, my joy was short lived. About 30 seconds after powering on, the fan ramped up to full power, after which the system shut down. After some investigation and experimenting, I determined that the issue was likely not the code or my coreboot configuration. I suspected that the embedded controller (EC) was to blame, so I asked about it on the coreboot IRC server. Someone did seem to agree, suggesting that the EC was waiting for some sort of "system OK" signal.

So now I have to figure out if that is truly the case, and if so, how to fix it. The easiest way to do that is probably reverse engineering the original BIOS, but due to Dell's EULA and the laws that apply to me, I am fairly certain I would not be allowed to do that. Exploring other options, I figured the only thing I could safely do would be to sniff the Low Pin Count (LPC) bus that connects the EC to the rest of the system. I have a some ideas for doing that, but I'll probably save those details for a future log once I have an actual implementation of said ideas.

---------- more ----------I've also made it much easier for me to flash the BIOS. I soldered some enamelled wires from the SPI flash chip on the top side of the motherboard to a DIP-8 socket in the unused wireless modem bay. I also removed the Firewire port and cable and replaced it with a switch that allows me to select either the internal SPI chip or the socketed SPI chip too boot from. An LED provides visual feedback on which chip is selected. Instead of disassembling the entire system, I can now just pop off the bottom panel, which only takes a single screw, and easily remove the DIP flash chip for external programming.

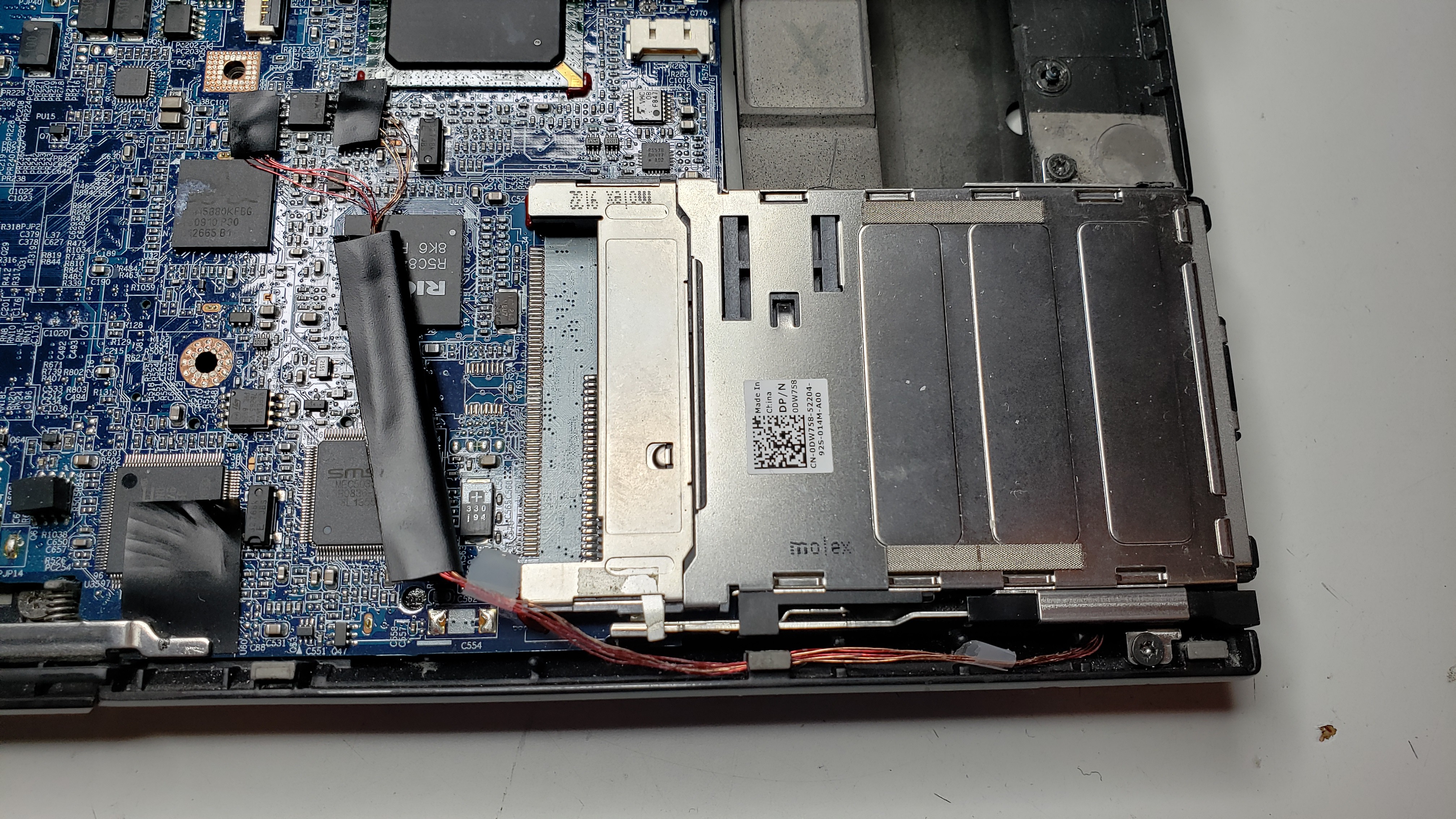

![Top side of motherboard Top side of motherboard]()

The top side of the motherboard, normally under the keyboard, showing the wires soldered to the SPI flash (the chip in between the two small strips of electrical tape at the ends of the wires) ![Right side of system Right side of system]()

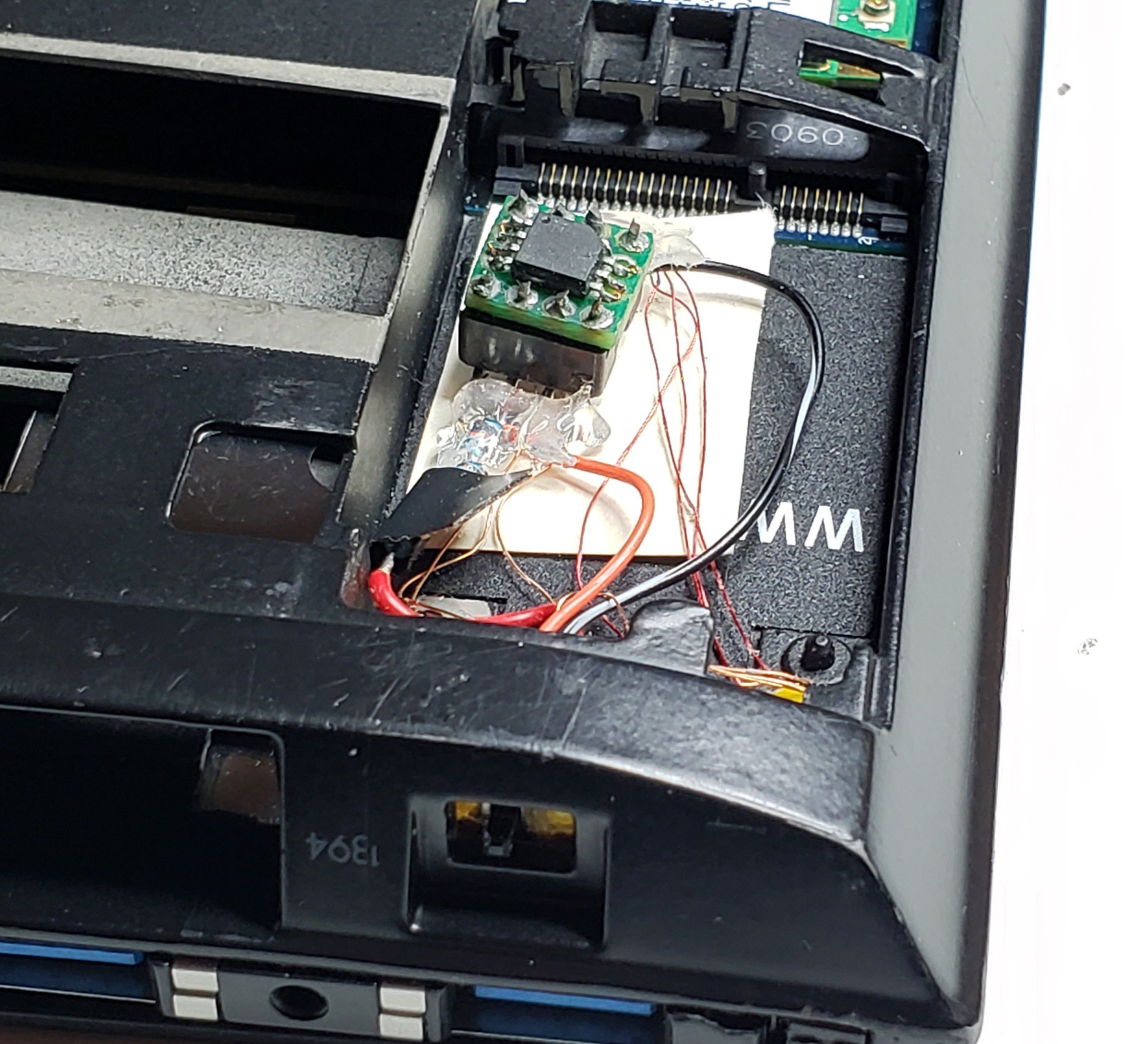

The right side of the system, showing the switch and LED in place of the Firewire (1394) port ![Bottom of system Bottom of system]()

The cellular modem card bay with the DIP-8 socket -

More work...

04/03/2019 at 05:37 • 0 commentsWell, I made a mistake. Coreboot does not (yet) support DDR2 on GM45. So I will have to implement DDR2 before I can continue the motherboard specific code for the E6400. This will be much more work, but I embrace the challenge and will go ahead in my attempt to port this machine. Hopefully I will learn a lot doing this, making it easier to port future boards. DDR2 is not completely absent from coreboot, so I should be able to turn to other chipsets to get a grasp of how to add support on this chipset.

-

GPIO done (probably)

02/26/2019 at 06:36 • 0 commentsAccording to the old wiki, the first bit of code you can change is the GPIO config using the output of a tool called inteltool. However, it states that the config is in mainboard.c, but in the case of the T400 code, it was moved to the gpio.c file.

Looking at the code initially, I could figure out how the configuration file was set up and what each line did, but I could not correlate the hexadecimal output of inteltool with the lines of code. Upon closer inspection, I realized that each binary bit in the hex numbers corresponded to a certain GPIO pin that could be configured. The value of each bit position indicated things such as whether it was used as a GPIO, signal direction, output state, and inverted inputs . Soon I had the file edited to match the GPIO config for the E6400.

I later found this information somewhere on the web, but by then I had already figured it out.

I did try flashing it after this, (and I had to desolder the chip, as it seems that using a SOIC-8 clip to to ISP may be activating other parts on the board and interfering with the SPI communications) and unsurprisingly, it did not boot. More work still needs to be done.

Latitude E6400 Coreboot port

Porting Coreboot (and hopefully Libreboot) to the Dell Latitude E6400

Nicholas Chin

Nicholas Chin