Many 8-bit processors and some 16-bit processors from 1970's and 1980's are packaged as 40 or 48-pin DIP which is easy to prototype, processors such as Z80, 6800, 6809, 8080, 8085, 1802, 6502 and some 16-bit processors with 8-bit bus such as 68008 and 32008. They are CPU-only devices without integrated peripherals and memory so external memory and I/O must be designed to work with the particular processor. The purpose of this project is to develop a generic prototype board that interfaces to these processors and provides memory, I/O, and mass storage.

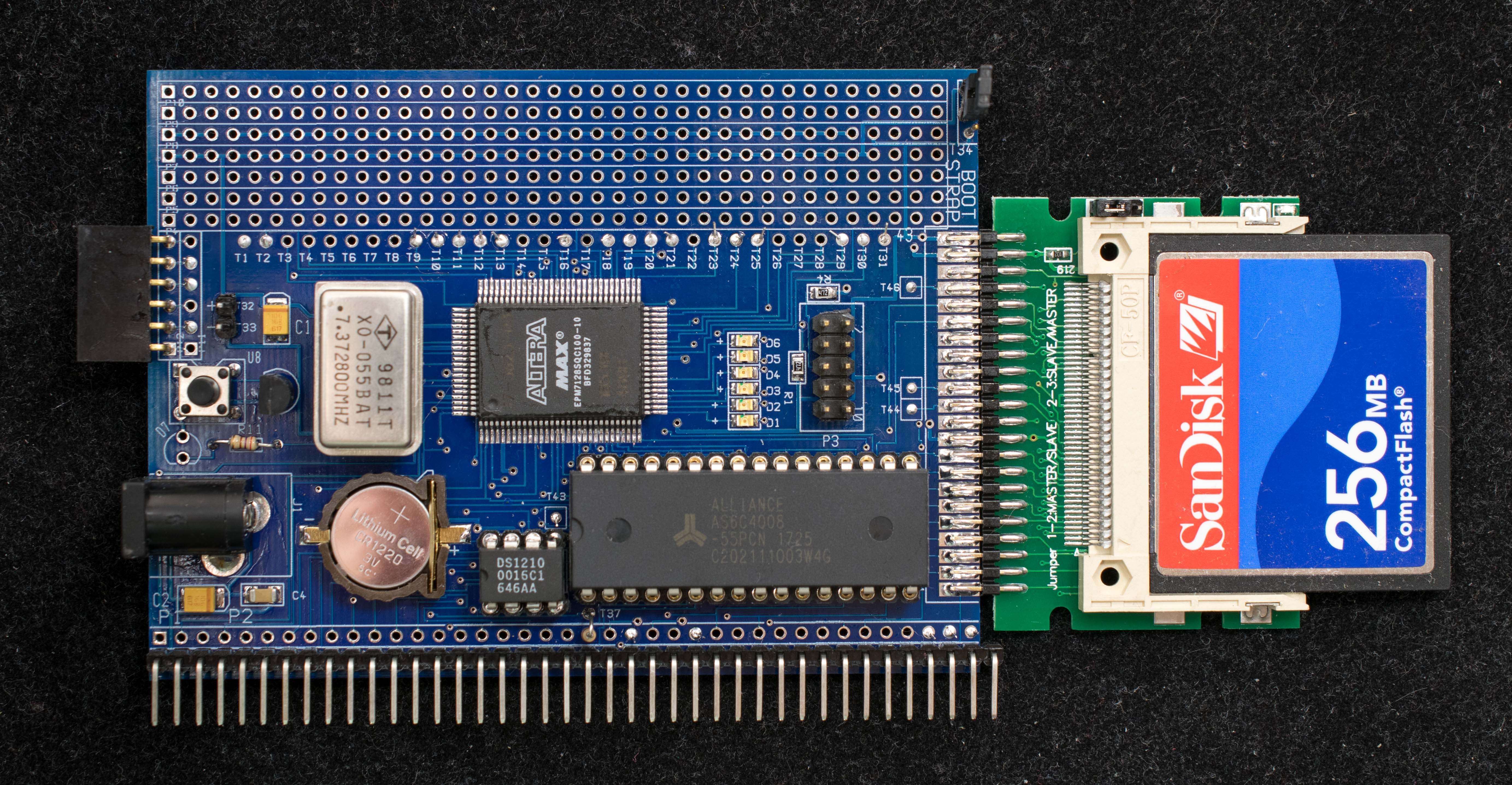

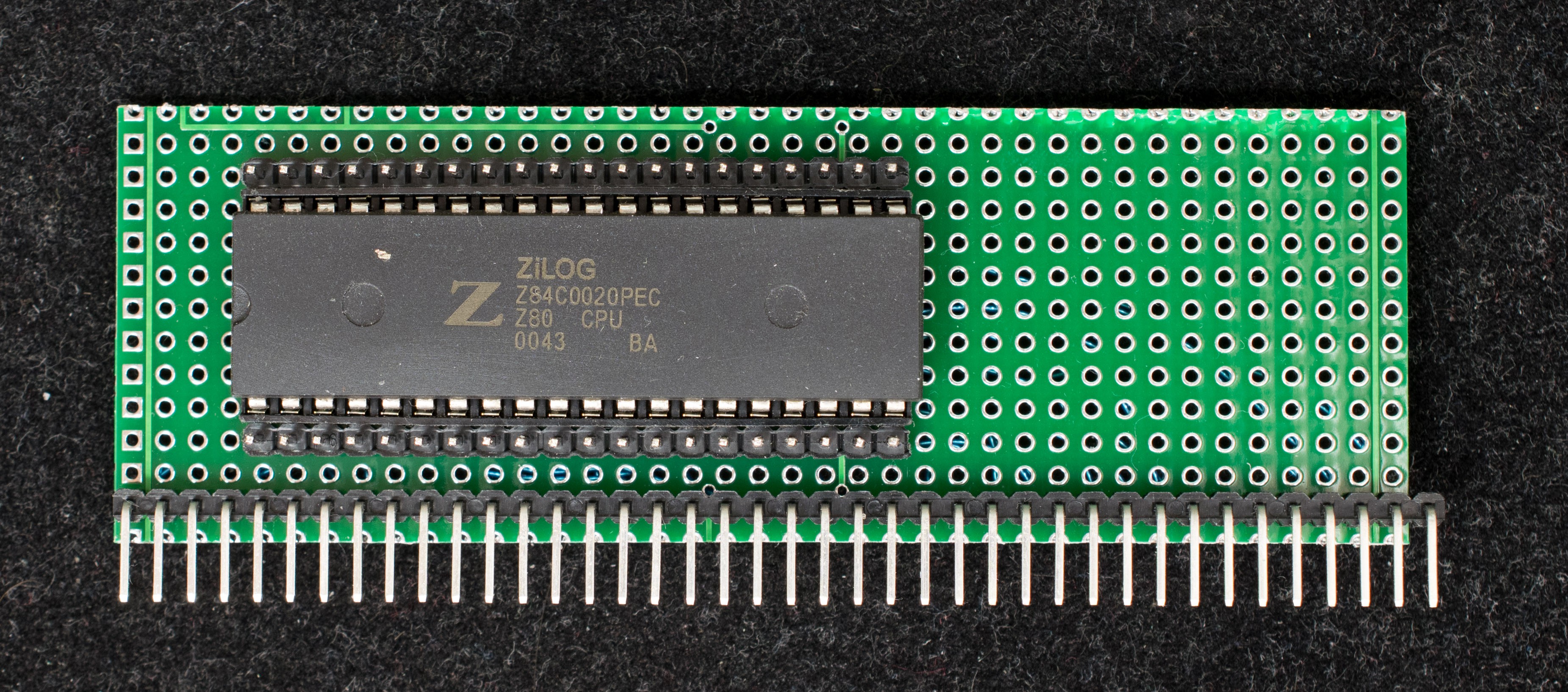

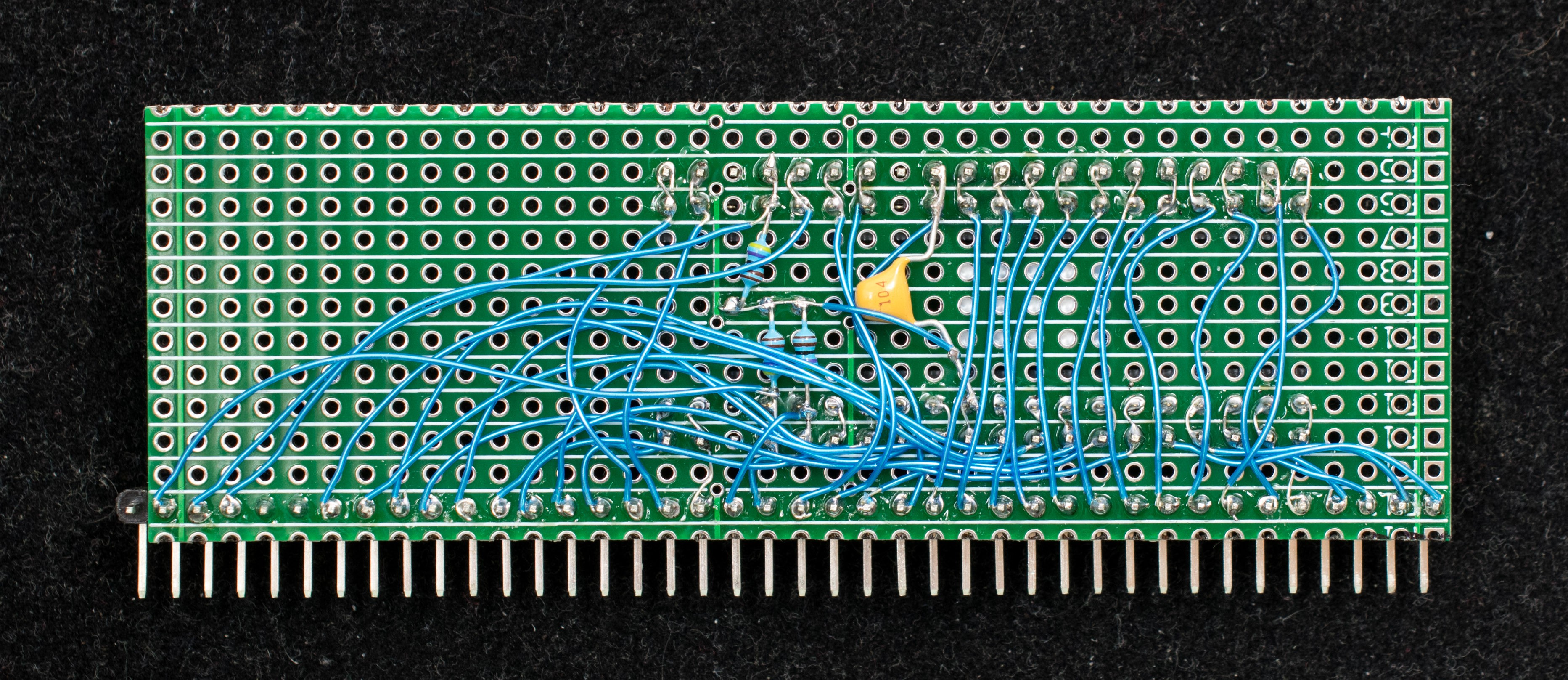

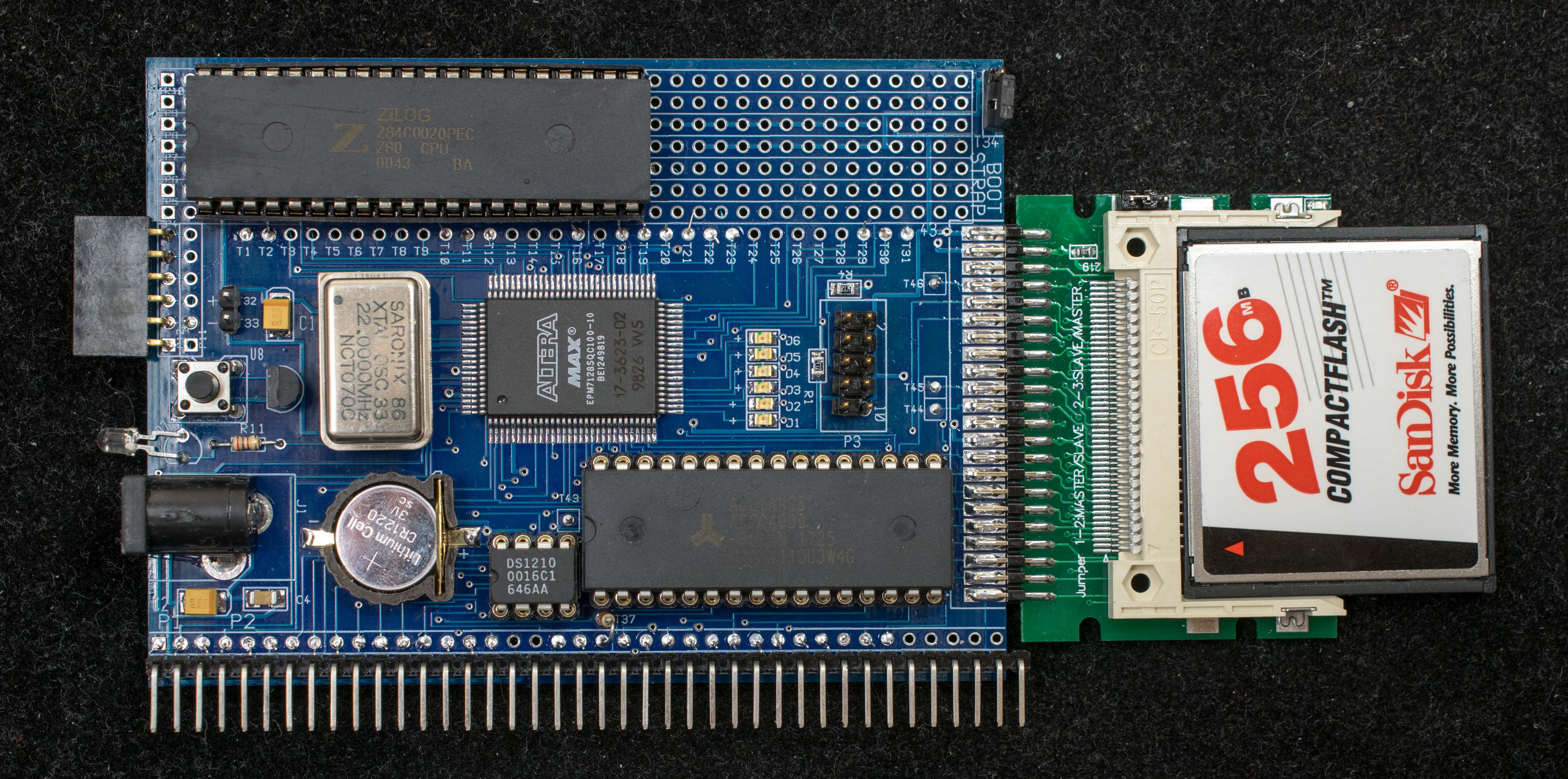

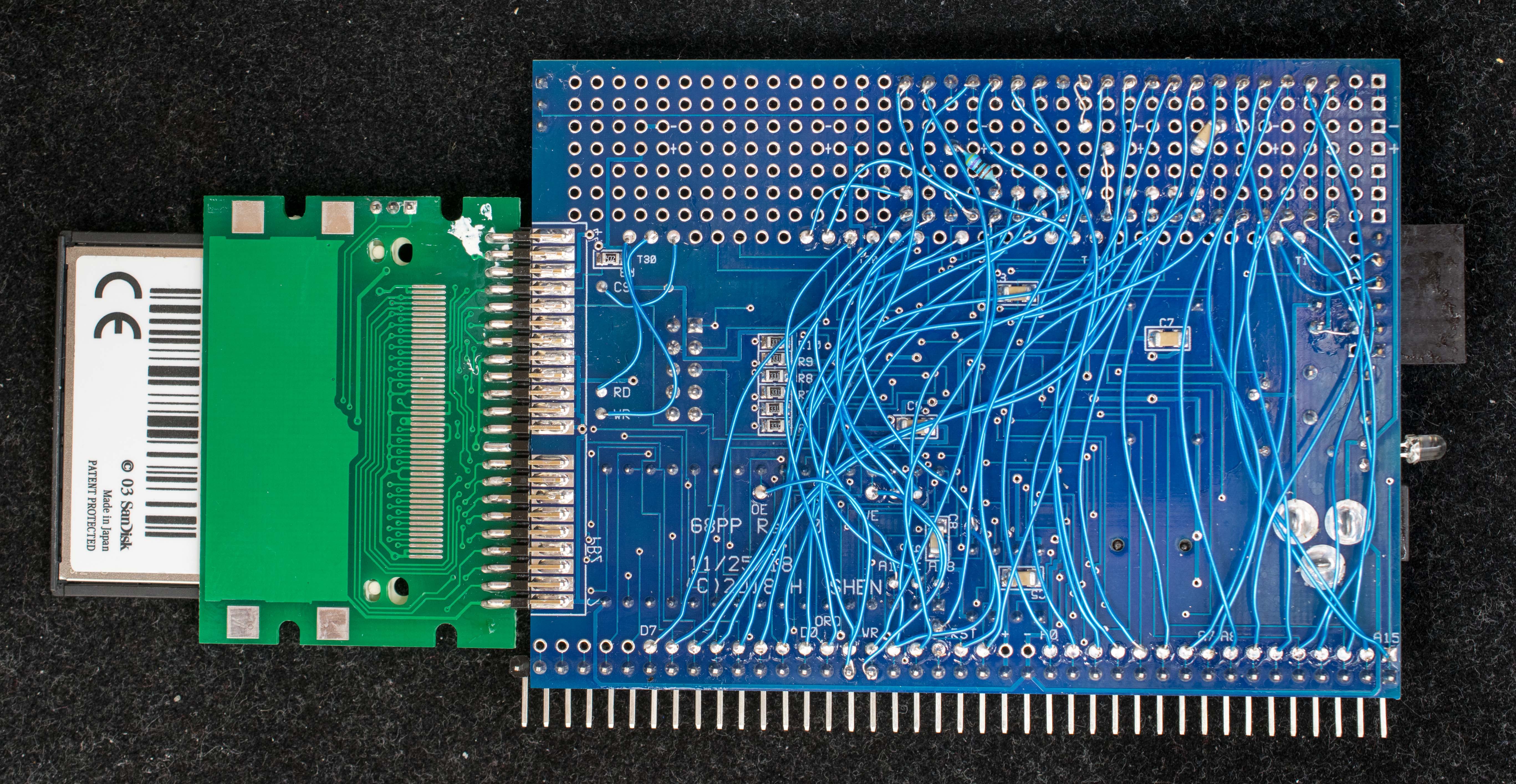

All these processors have 16 or more addresses, 8 data lines, 5V power, clock, and reset plus a number of processor-specific control signals. The RC2014 bus is a simple 40-pin connector defined for Z80, but it can be easily redefined for other processors. The data, address, clock, power, reset and interrupt of RC2014 remain the same, but the 5 Z80 control signals and 4 spares can be redefined for other processors. A in-situ programmable 5V CPLD can be reprogrammed to different processor's control signal characteristics. The same CPLD can also provide the glue logic for memory, I/O and mass storage. So a CPLD with RAM, compact flash interface, oscillator are the building blocks of a generic 8-bit processor prototype board or G8PP. An operational computer can be built with a simple CPU board and a G8PP board plug into a RC2014 backplane.

This project is a series of experiments demonstrating how G8PP can interface with many different processors resulting in capable operational computers.

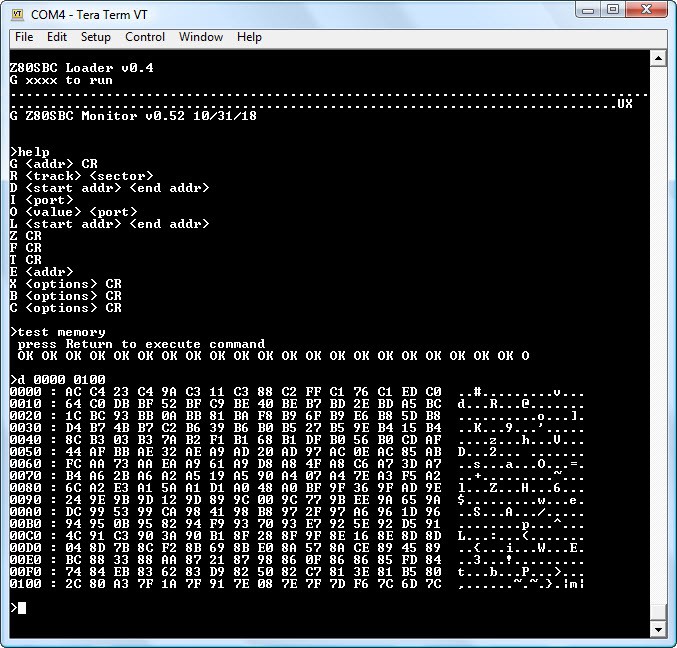

Introduction to G8PP, common functions and two modes of operation.

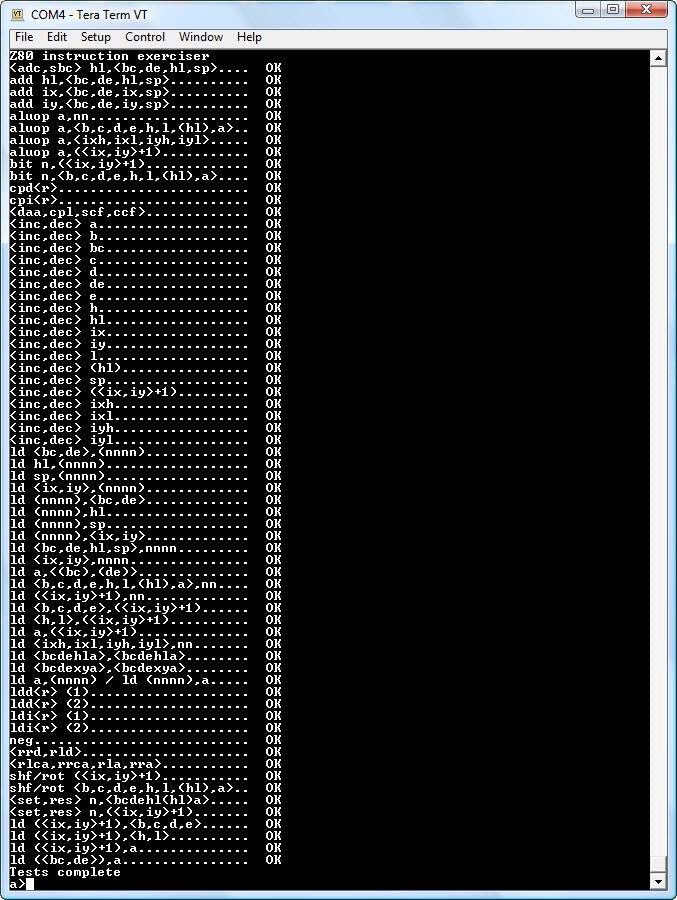

G8PP+Z80 Part 1, demonstrate the G8PP concept with a single-board Z80.

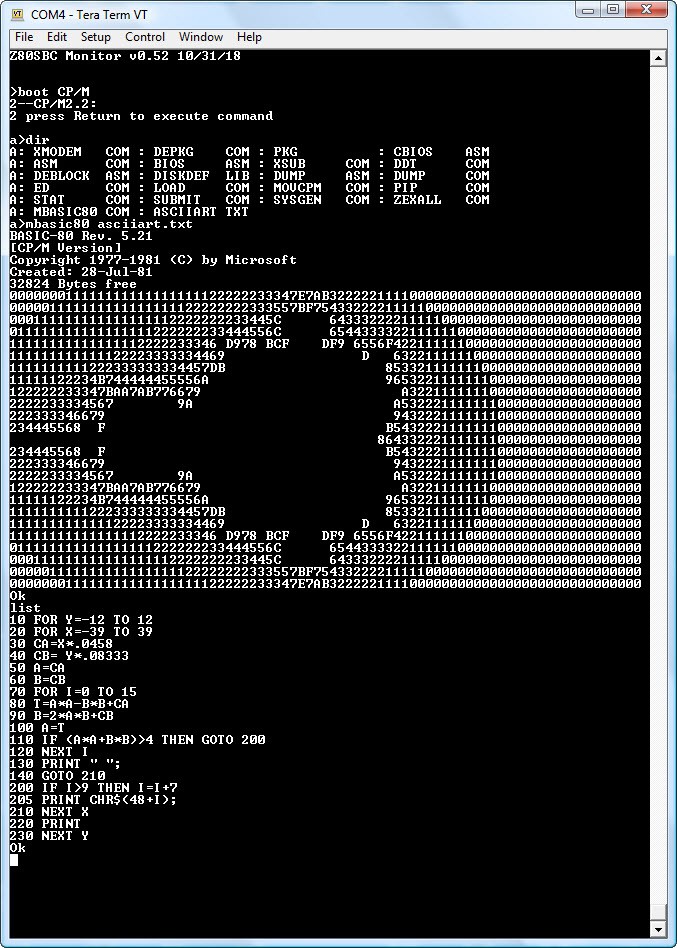

G8PP+Z80 Part 2, running CP/M on the single-board Z80

G8PP+Z80 Part3, separate G8PP board and Z80 CPU board on a RC2014 backplane.

G8PP+Z80 Part4, PC board CPU cards, G8PP+CPU without RC2014 backplane.

Plasmode

Plasmode

Trevor Johansen Aase

Trevor Johansen Aase

J.B. Langston

J.B. Langston

I really like the idea behind this project - it allows varying the processors (which is always fun to explore!) by keeping the rest of the hardware stable on universal RC2014 bus. But I was wondering if a next step could be taken in flexibility - truly control the bus using software. For example:

https://www.futurlec.com/Zarlink/MT8816AE.shtml

With 4 ICs like this the "Y" bus could be fixed connected to RC2014 signals (16 address + 8 data + 8 control) and the "X" bus would have 64 signals - connected to 48-pin DIL (or ZIF?). That way the CPU/RC2014 connection would be a matter of programming the MT8816 matrix. This could be done during the initial bootstrap phase.