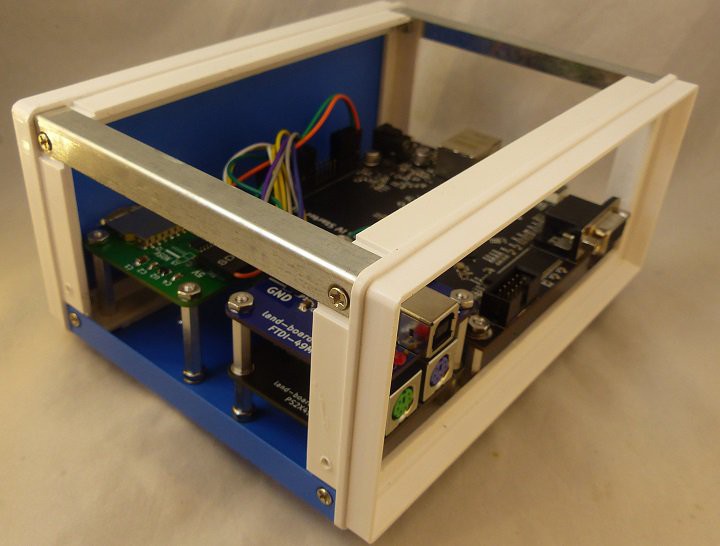

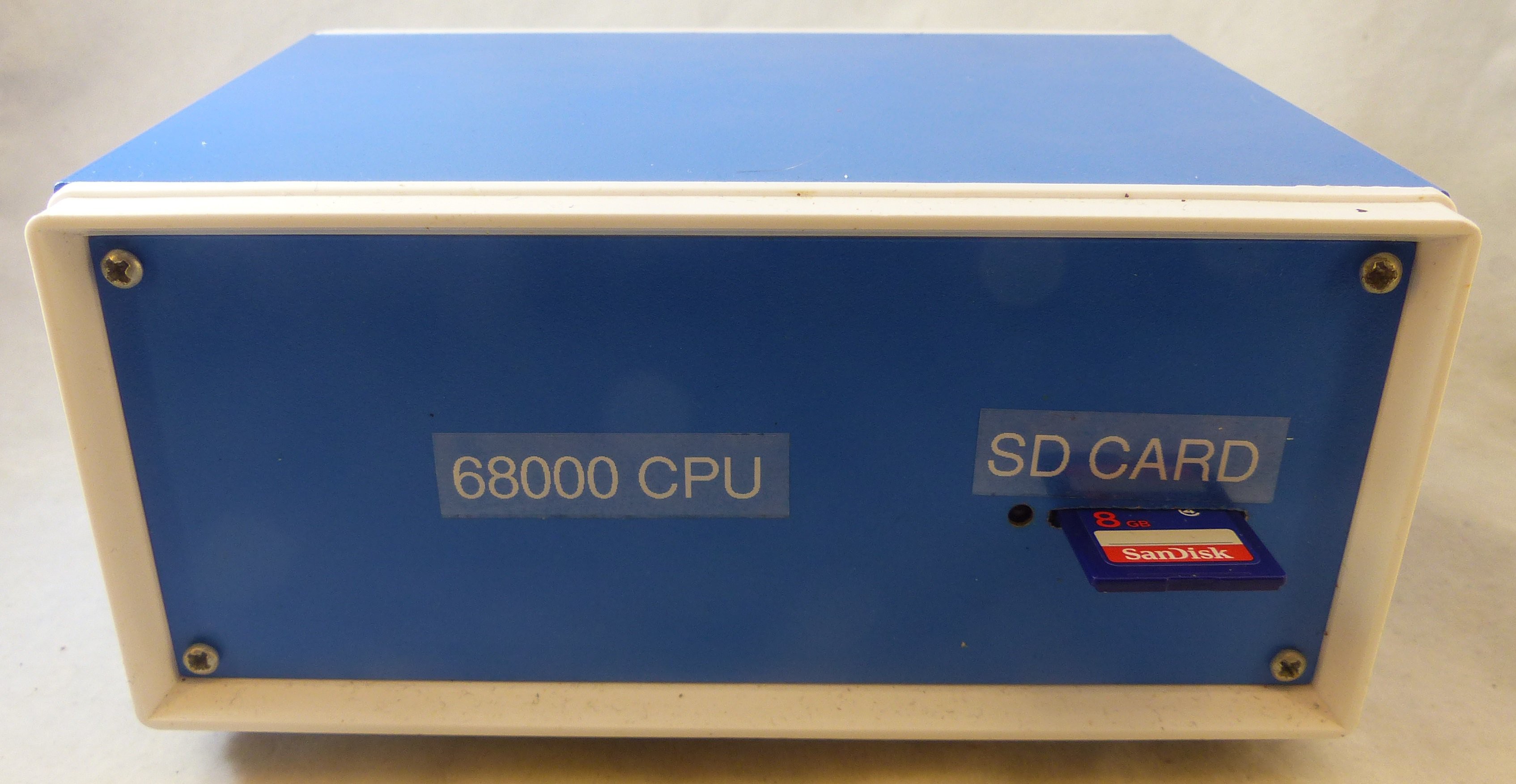

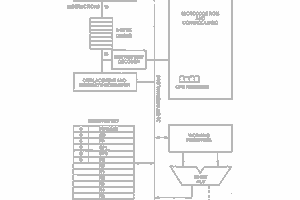

I recently completed a build of Jeff Tranter's build of the TS2 68000 CPU. It turned out pretty nice but has serious limitations due to the original memory map of the TS2 which only had 32KB of SRAM from 0x000000-0x007FFF. The PROM is located in the next 32KB space from 0x008000 to 0x00BFFF. Porting the assembly language Tutor ROM code to higher memory proved to be quite painful.

A Better Target Design

A helpful person in the MOTOROLA 68000 / 68K ASSEMBLY LANGUAGE PROGRAMMING Facebook group pointed me to AMR's TG68 Experiments pages.

One of the advantages is that this design uses the 32MB SDRAM on typical FPGA cards.

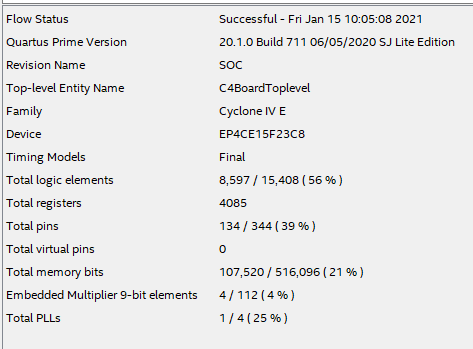

I made a build of AMR's design targeted to Cyclone IV and V FPGA cards and documented it in a log of the TS2 build (SDRAM Working in a Different Context). In particular, this leverages from Part 14 of the series. If you want to try AMR's project, start with the Master branch here.

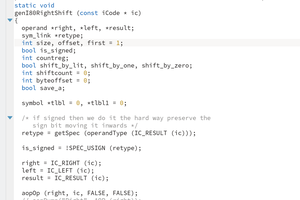

The project creates a very powerful 68000 FPGA project and has a good narrative of the progress AMR made in the work but is short on details. Many of these details require digging into AMR's source code. I should note that I opened an issue on his Github page and he was very helpful.

This project will try and fill in some of the gaps in AMRs documentation.

Features

- 68000 CPU in an FPGA - Tobias Gubener’s TG68 processor core

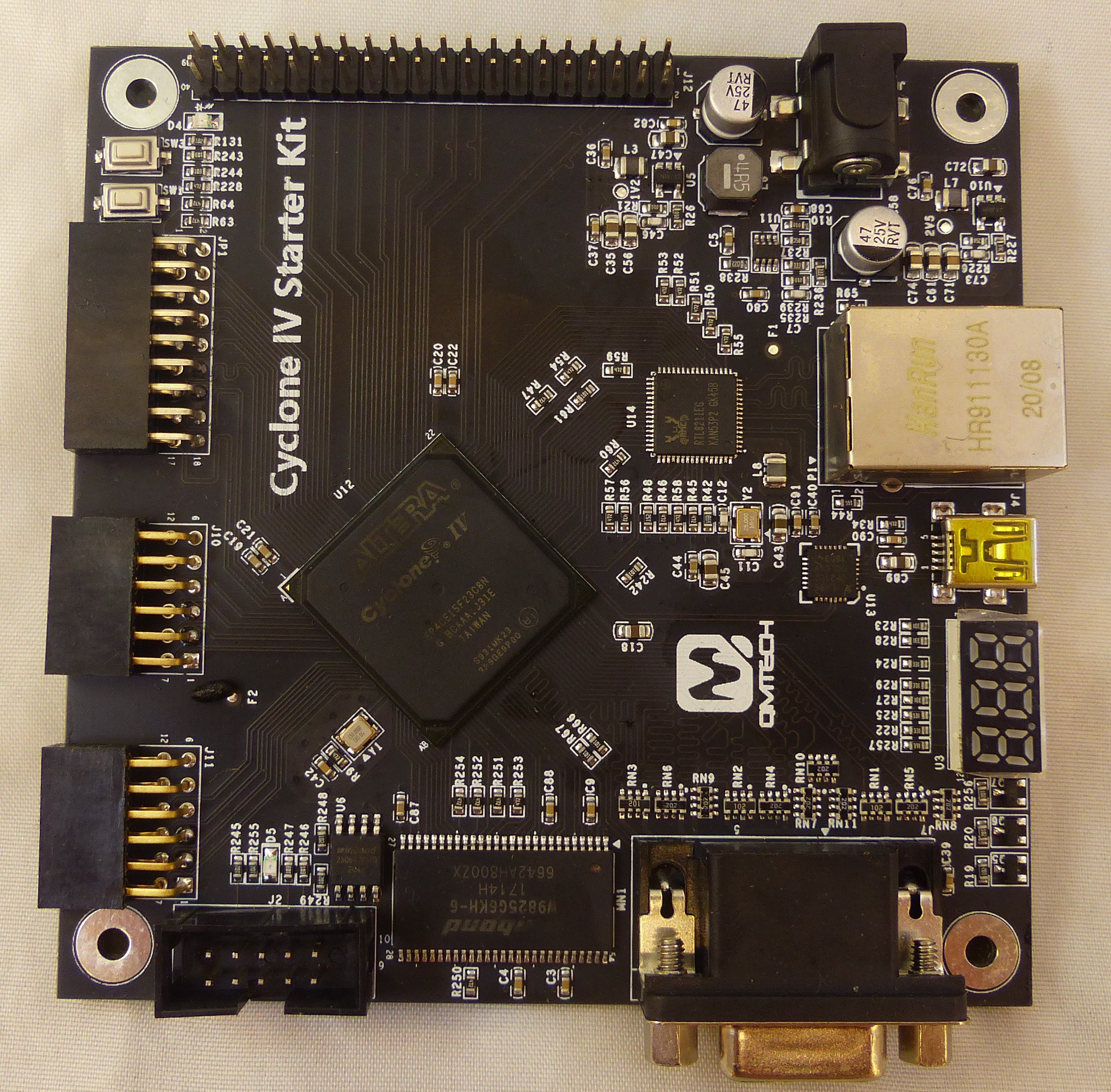

- Altera/Intel Cyclone IV or V FPGA

- 32 MB SDRAM

- Video Frame Buffer in SDRAM (2:2:2 or 5:6:5 bit video)

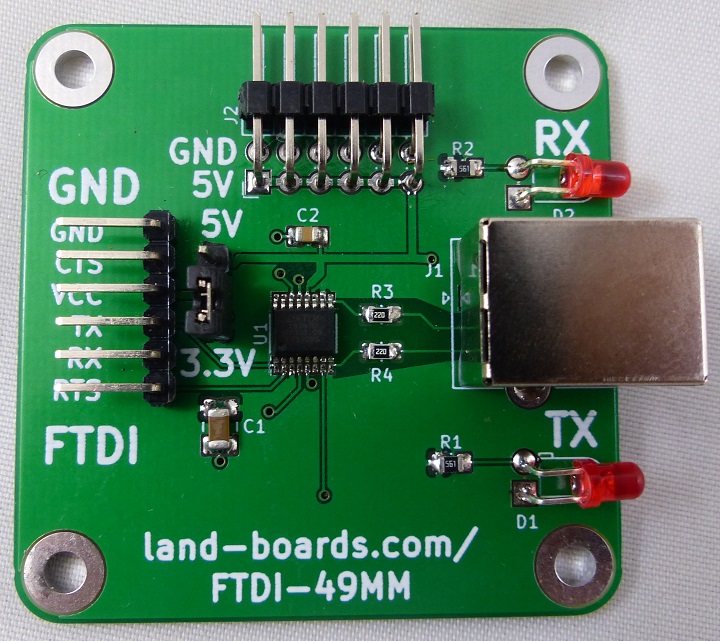

- USB to Serial

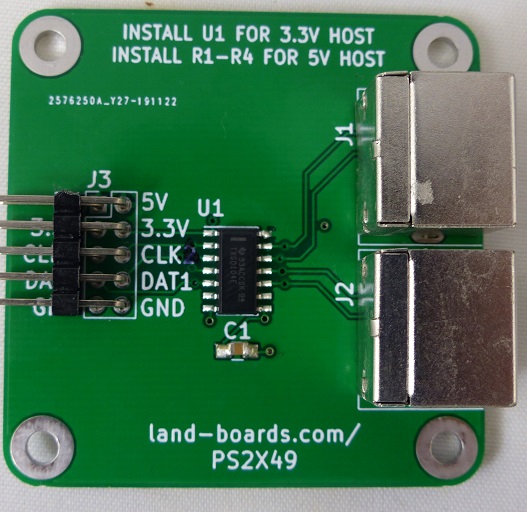

- PS/2 Keyboard and Mouse

- Based on OpenCORES TG68

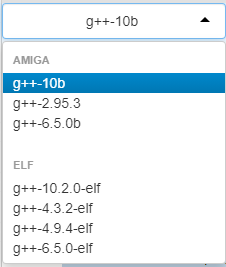

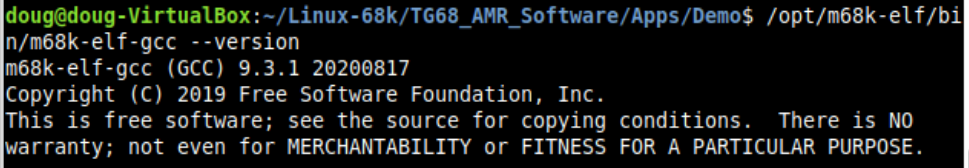

- Vasm and GNU GCC Toolchain (Linux)

- Bootloader in ROM loads program from SD Card

land-boards.com

land-boards.com

Front with White on Clear labels

Front with White on Clear labels

Keith

Keith

Ken Yap

Ken Yap

Matthew Pearce

Matthew Pearce

QMTECH EP4CE15 FPGA "Starter Kit" link webpage has been deleted from main article