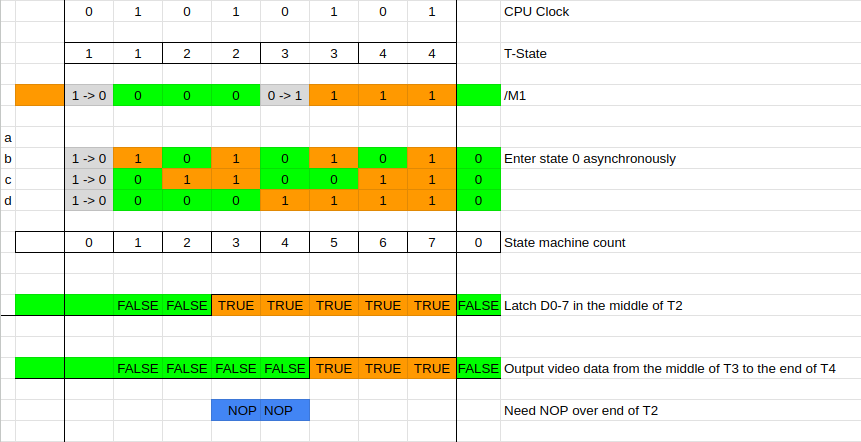

I was looking at the Ian Bradbury design and wondering how to port it to more commonplace chips.

Searching the net, I found the remarkable Andy Rea had already implemented the ZX81 logic this way, in 2011.

Much of the information is scattered about the web, and his own pages at http://homepage.ntlworld.com/deborah.clayton1/ULA/ula.html have gone 404.

So I've assembled a collection on hackaday.io for convenience.

I've cached the zipped files from here:

https://www.sinclairzxworld.com/viewtopic.php?f=6&t=445 (attachment ula2.zip)

No circuit diagram yet but you could probably start from my guess at Ian Bradbury's circuit and gradually rework it.

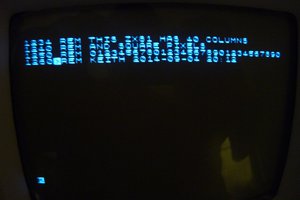

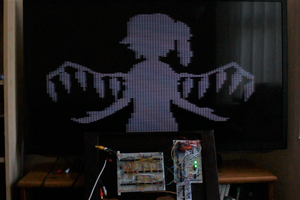

Andy Rea pointed me at Wilf Ritger's articles about ZX81 video text and high-res graphics.

I need to wrap a towel soaked in icy water round my head when I plough through that. :-)

Keith

Keith