News: Project is being migrated, mybinder links will no longer work.

The virtual machine contains:

- A jupyter notebook installation (obviously)

- A recent pyosys module build (including full yosys functionality)

- An icarus verilog installation to verify and simulate verilog code

- The MyHDL 'jupyosys' fork supporting synthesis

- Various utilities to display waveforms and dot graphics

What you basically can play with in this binder:

- Run code to describe and simulate a hardware element

- Dump a waveform trace

- Synthesize into yosys primitives and display

- Verify the synthesis and technology mapping working correctly by Co-Simulation

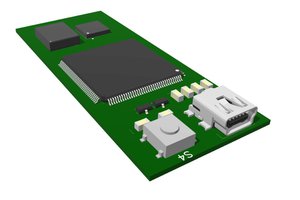

- Generate a bit file and download it to an Versa ECP5 Lattice development kit

There are examples/exercises being added every now and then in the 'dirty' hacker space which is checked out secondarely inside the running container. Some examples also contain german explanations that can be squelched using the [Language] menu dropdown (possibly not working in some browsers other than Firefox).

Martin

Martin

ziggurat29

ziggurat29

Adam Guilmet

Adam Guilmet