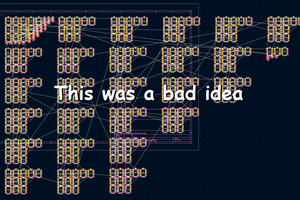

The project is currently in progress:

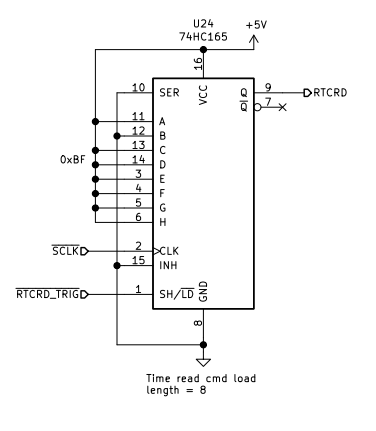

[DONE] Time register read circuit

[DONE] Parallel output stage

[DONE] 7-Segment output board

[DONE] HV boost converter circuit for nixies

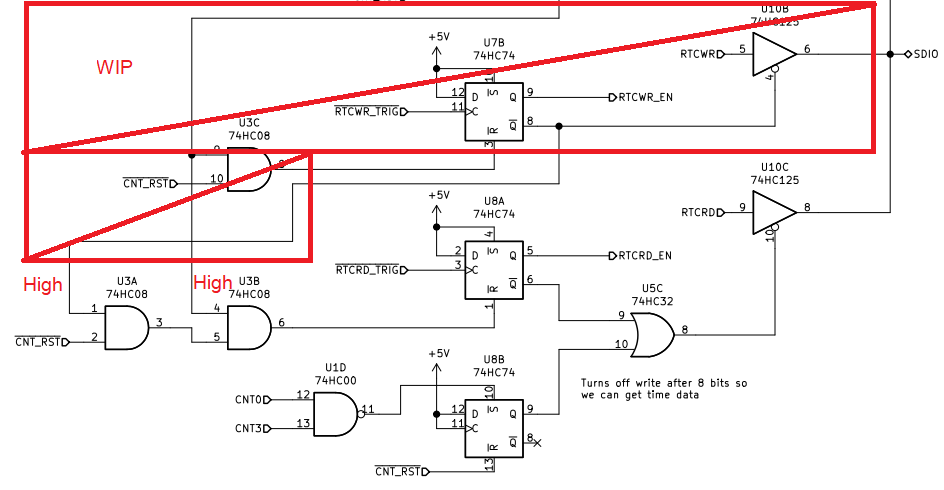

[Debugging] Time register write circuit

[Debugging] Write-Protect (WP) bit clear circuit

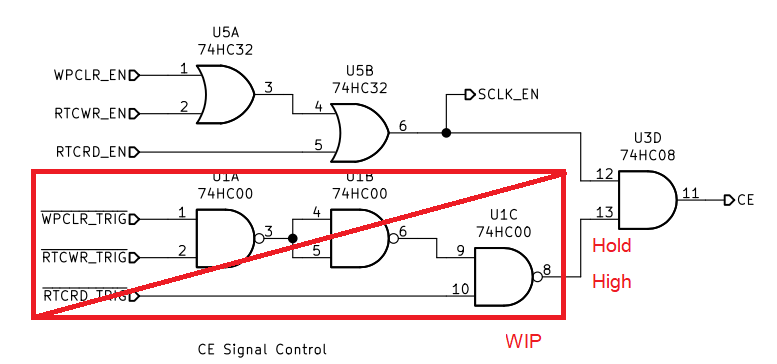

[Debugging] SPI bus arbitration circuit

[Planned] Display dimming circuit

[Planned] Nixie output board

Note: The component list on the project page only lists the chips I use. For the full parts list, please check out the attached KiCad files.

-------------------------------------

This clock is my third clock. The first two (TTL clock and Ammeter clock) are nice and work fine. However, there is one common problem:

I have to set the time again if I unplug it.

This starts to get very tedious. Especially during debugging that I have to unplug it often to fix stuff, or to change where I place my clock, or when there is a blackout, so I know that on this one the time must be battery-backed.

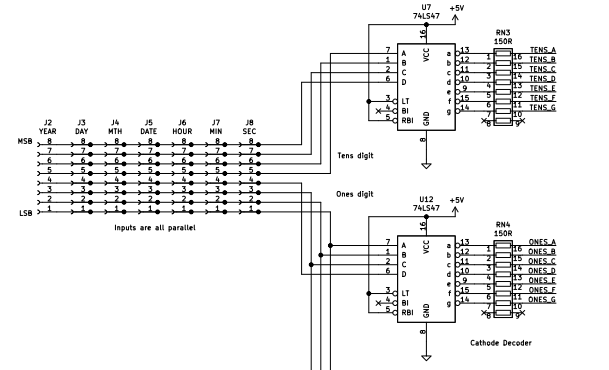

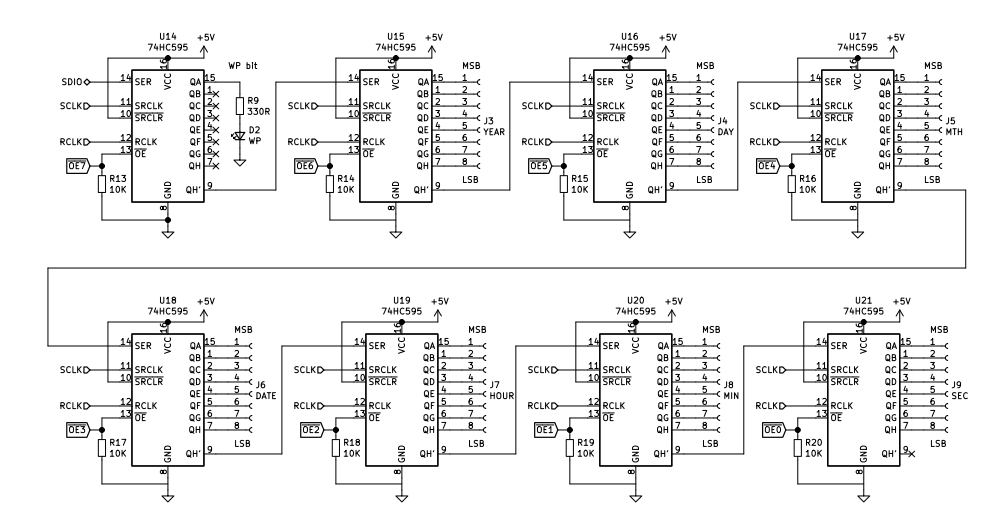

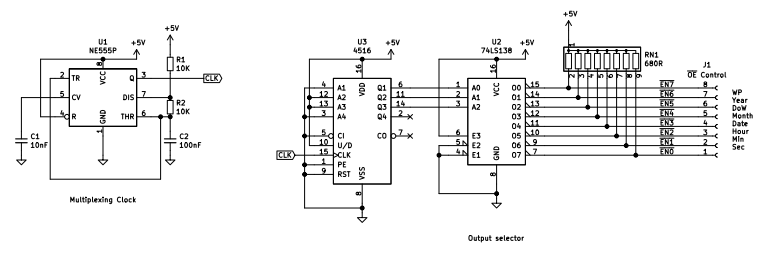

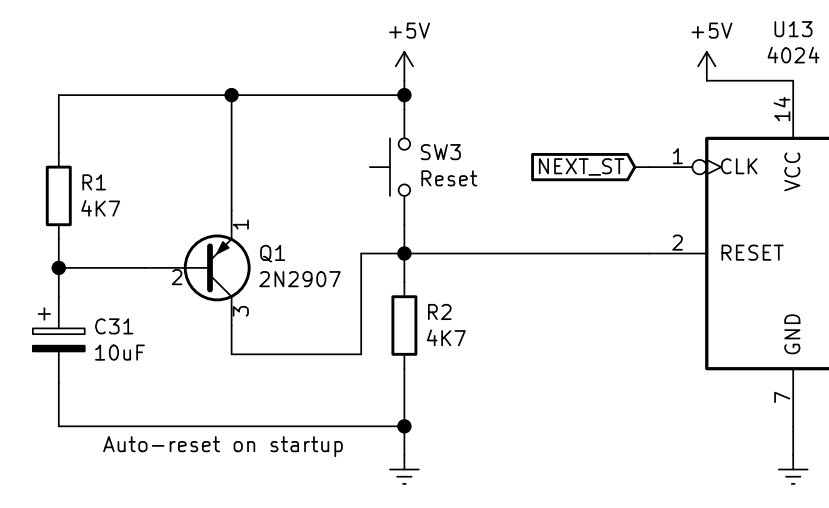

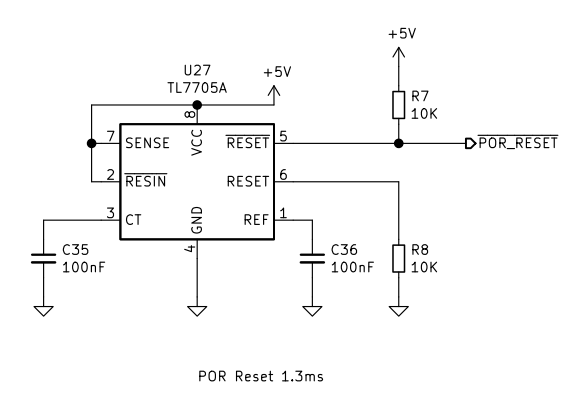

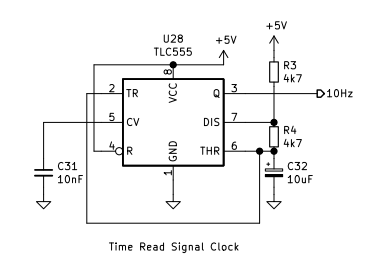

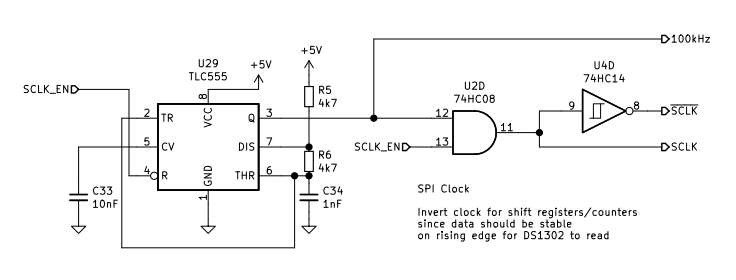

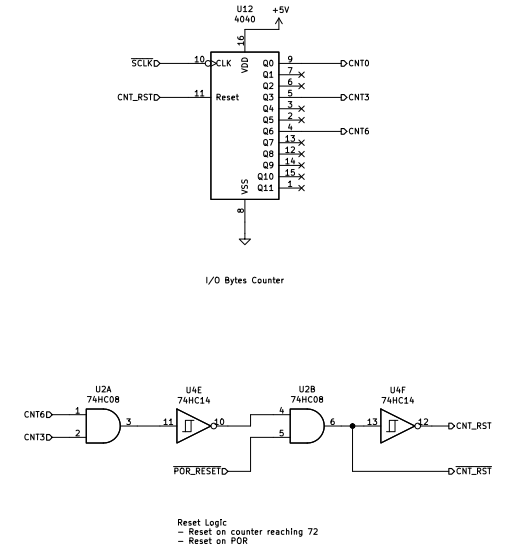

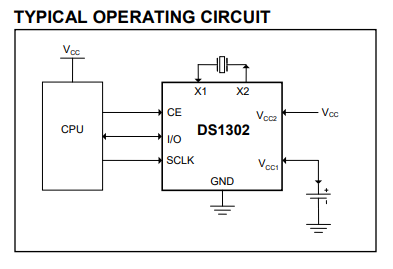

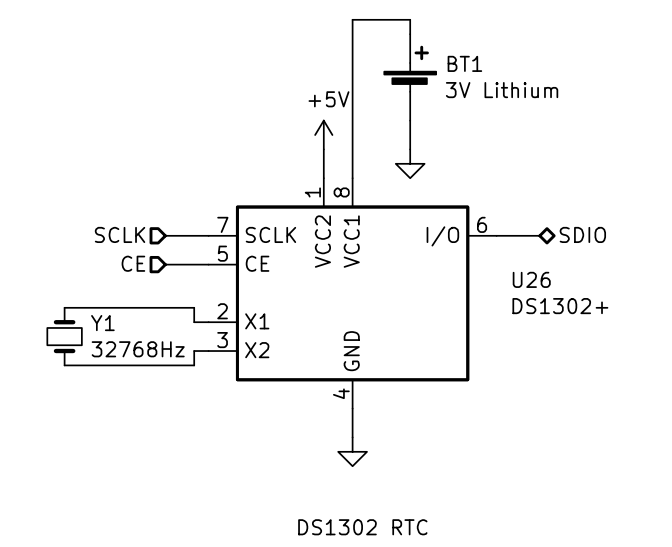

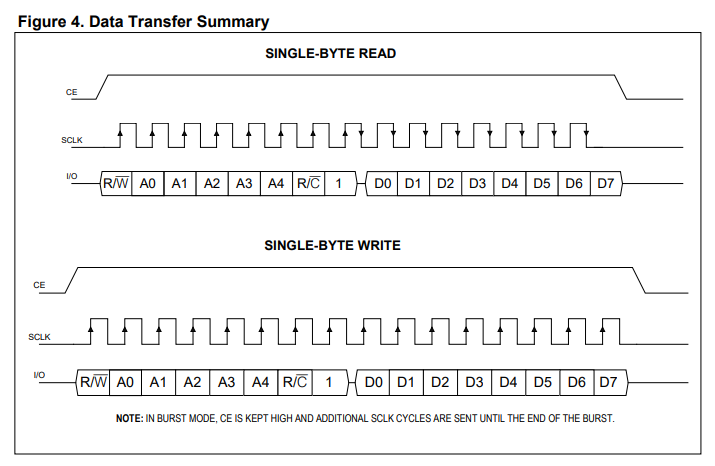

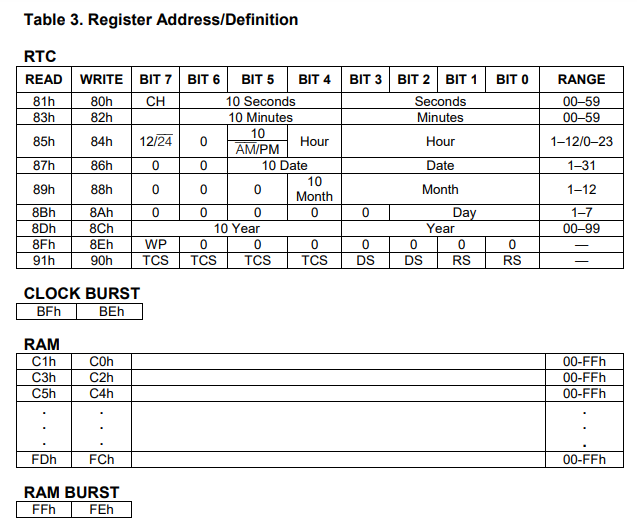

Therefore this clock was born. It uses a DS1302 battery-backed SPI RTC chip to store and count the time. A 555 timer controls the sampling of time from the RTC 10 times a second with an SPI transaction at the speed of around 150 kHz (from a second 555 timer). The time read will be dumped onto a set of shift registers, which could be used to drive all kinds of displays from 7-segment to nixie tubes.

The clock also includes a circuit to allow the user to clear the write-protect bit and set the RTC time via DIP switches. The priority-based bus arbitration circuit allows the SPI transaction to complete smoothly. (This part is still under development.)

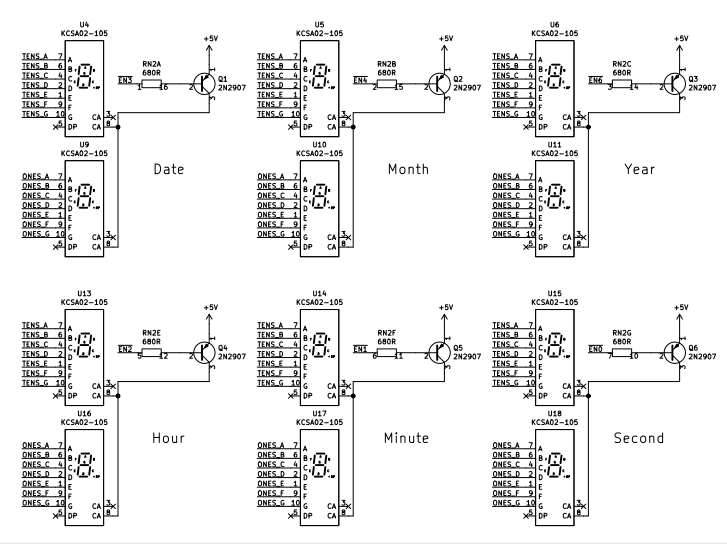

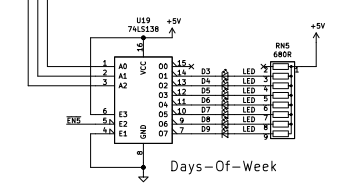

Currently, I built a 7-segment output board for the clock. The output board features 6 sets of 7-segment displays that are used to output year, month, date, hour, min, and sec, and a linear display to show day-of-week. A 555 timer and several logic chips are used to control display multiplexing.

The project is still under development. If you have any suggestions apart from the ones listed above. Please feel free to leave a comment. Thanks for reading!

Sleepy Pony

Sleepy Pony

Keith

Keith

Muth

Muth

Paul

Paul

Marten Electric

Marten Electric