Project status:

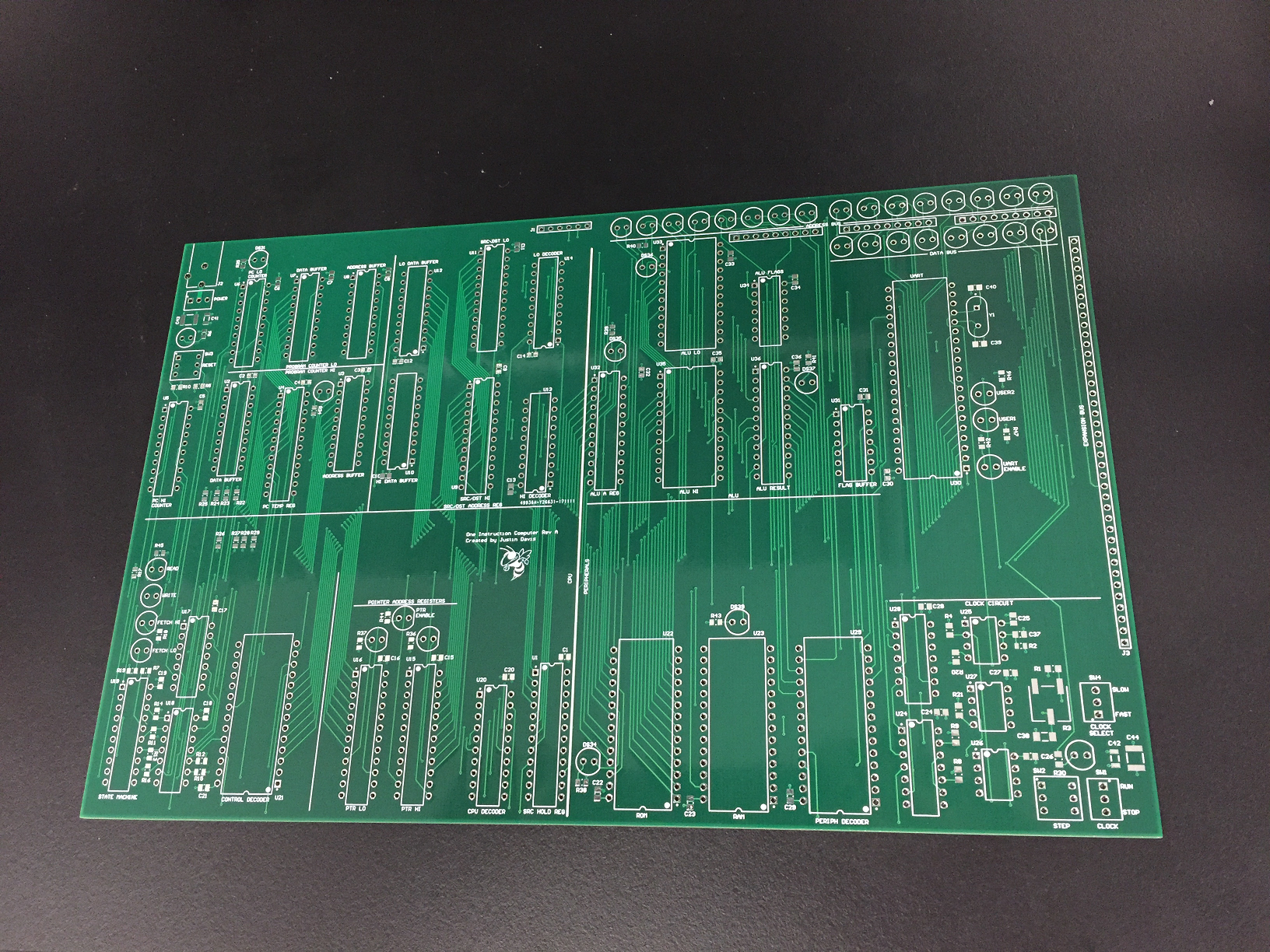

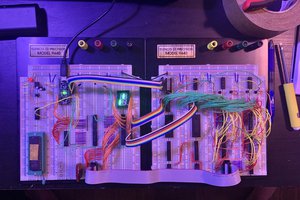

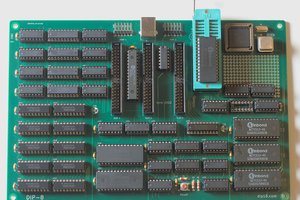

I have a working version of the architecture simulated in VHDL. It is synthesizable, and I have downloaded it to an Artix-7 development board - the Digilent Cmod. I have a few simple programs running with a UART interface. I have a bootloader/monitor running so I can load programs over the UART. I've written a simple assembler to generate machine code I can send to the bootloader. I've finished a schematic and layout for making a PCB.

Primary project goals:

- Implements only one instruction - move

- Can be built using a minimal number of simple DIP components (74xx TTL circuitry).

- All components are active. No obsolete or hard-to-find components. All components in stock at popular distributors.

- Useful - it needs to be able to run programs in a short amount of time.

Secondary project goals:

- Useful input mechanism. I expect a set of DIP switches for the input, but I'd prefer something more useful like a UART port or maybe a keyboard.

- Useful output mechanism. I could do a simple LED numeric display, but I'd prefer something more useful like a UART or at least a 4x20 character display. Perhaps I'd even do a video memory with a separate display.

- Easy and natural loading of programs. I'd prefer not to have a roundabout way to load programs into memory. Perhaps even use the above UART to send programs.

- Easily expandable for more memory. I'd like to be able to load very large programs.

- Write/adapt a compiler/assembler. I'd like to be able to take existing programs and compile them to run on the computer. This would probably be the last thing I do considering the complexity.

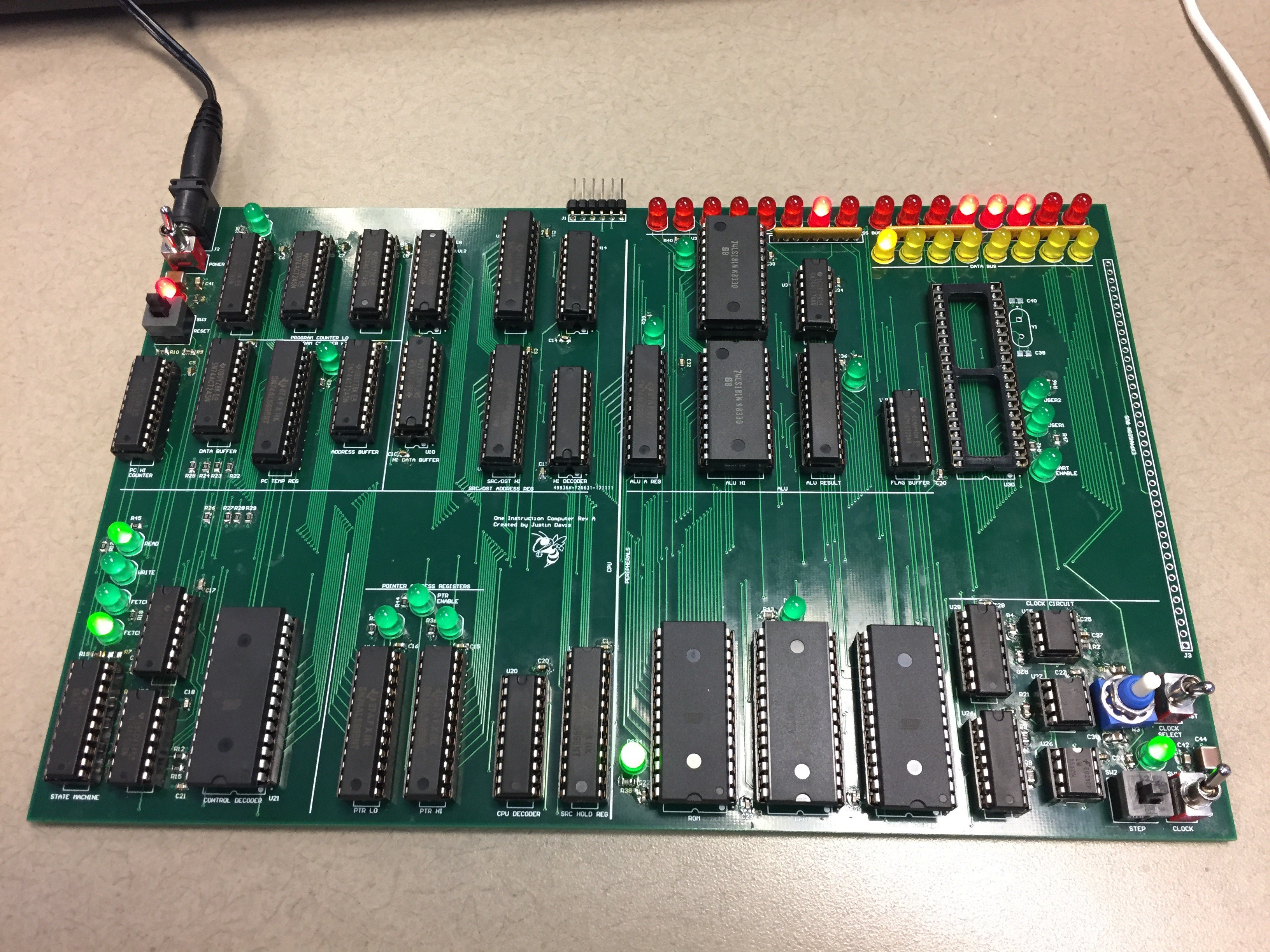

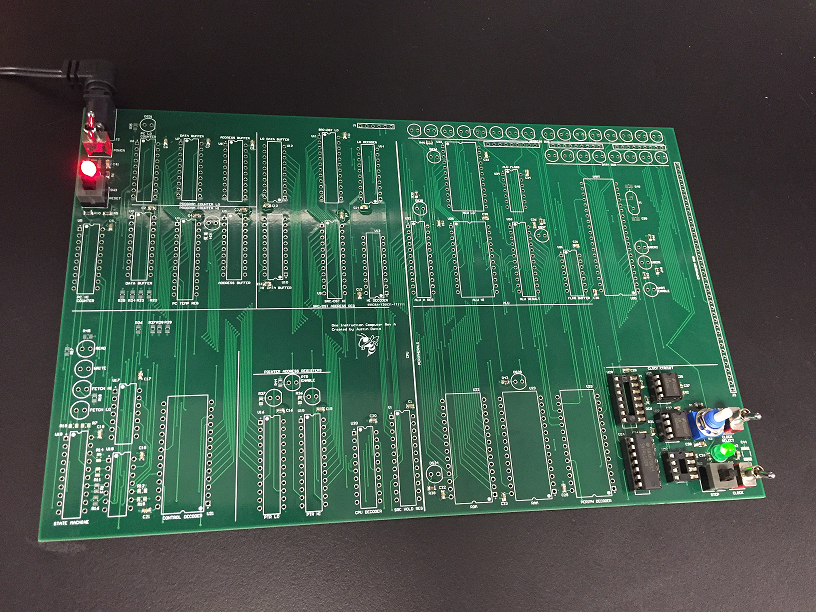

PCB Assembly Plan: bold is completed

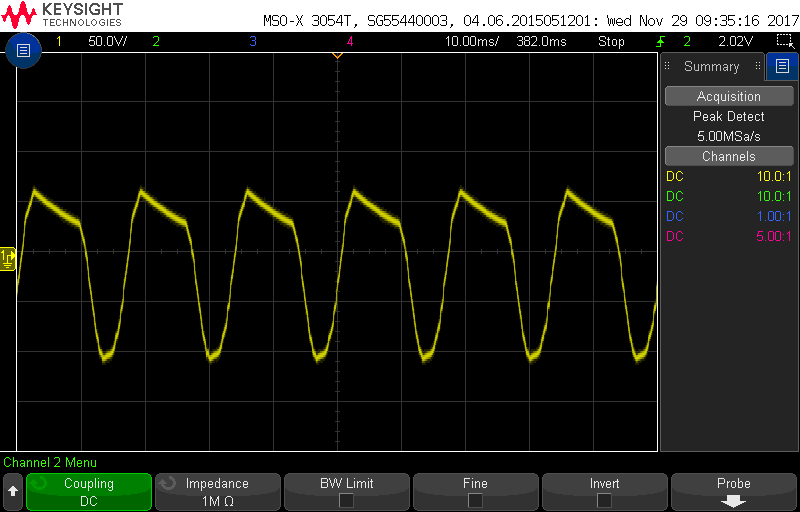

- Clock circuit with single-step mode and Reset

- Control state machine with AND/NOT gates and control LEDs

- Program counter Low and High with Memory Address Buffers and address LEDs

- Control Decoding

- Instruction ROM and data bus LEDs

- Src/Dst Hi/Lo registers with data buffers and Src/Dst decoders

- Source Hold Register

- Program counter Temp register and data buffers

- ALU A

- ALU '171 chips

- ALU result reg

- AEB/Carry FFs/buffers

- Pointer address registers

- UART

- RAM

Tim Ryan

Tim Ryan

Charlie Smith

Charlie Smith

kaimac

kaimac

Hi Justin,

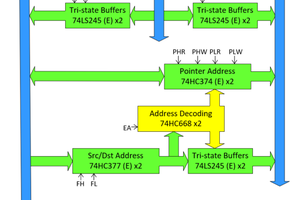

Step back and relook at what a TTA is:

MOV [DST], [SRC]

---

The machine cycles are:

Fetch SRC (address)

Fetch Data from [SCR]

Fetch DST (address)

Deposit Data to [DST]

This is what the timing diagram of the control signal looks like for the above machine cycle:

---

Sorry there is no load immediate but your assembler can store a constant for you to simulate a load immediate.

---

For indirect addressing (pointer to pointer moves, you will need these at some point), you will need self modifying code.

That is for another time.

--

If your happy with the above the decoder logic is four chips including the clock.

---

AlanX