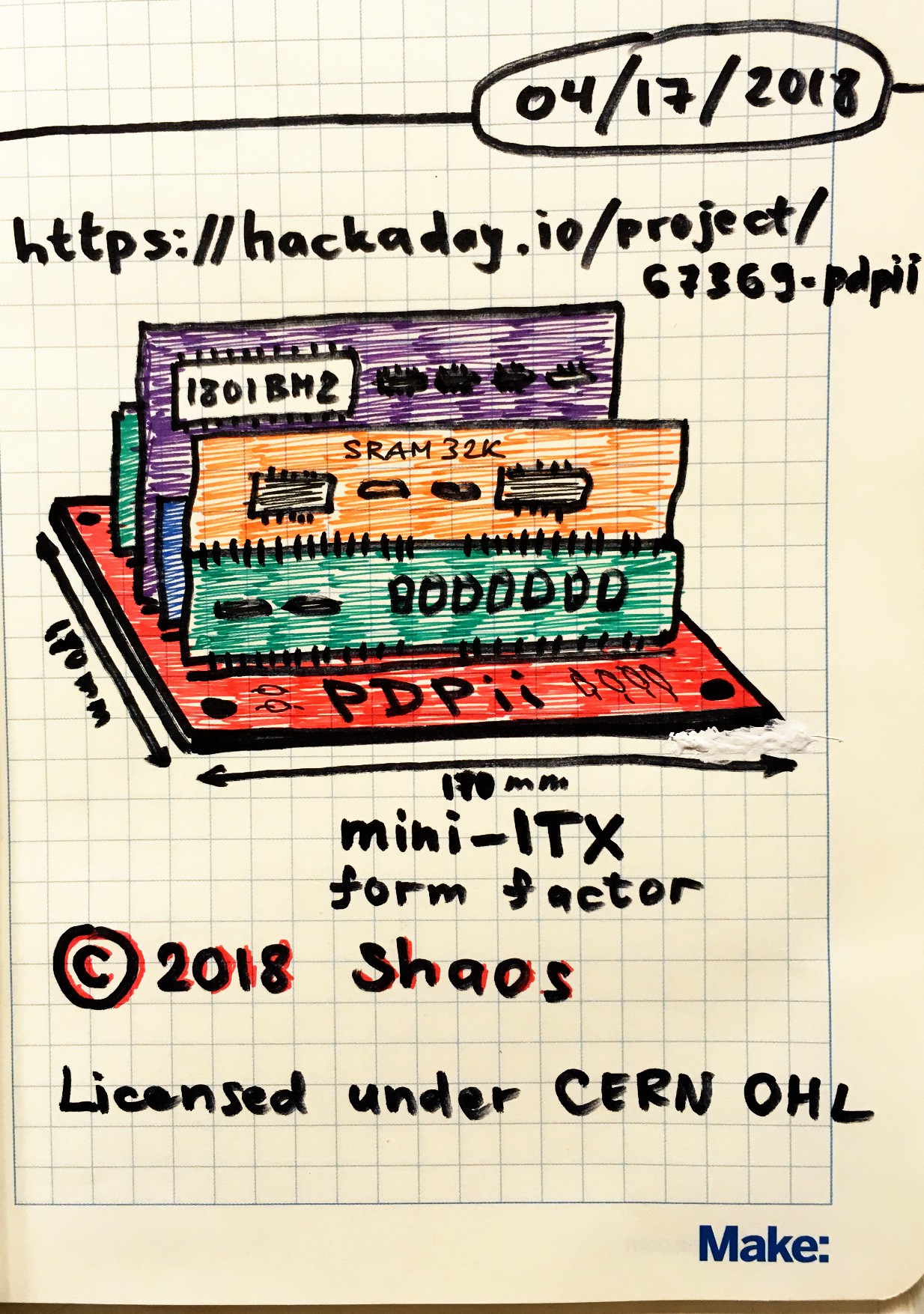

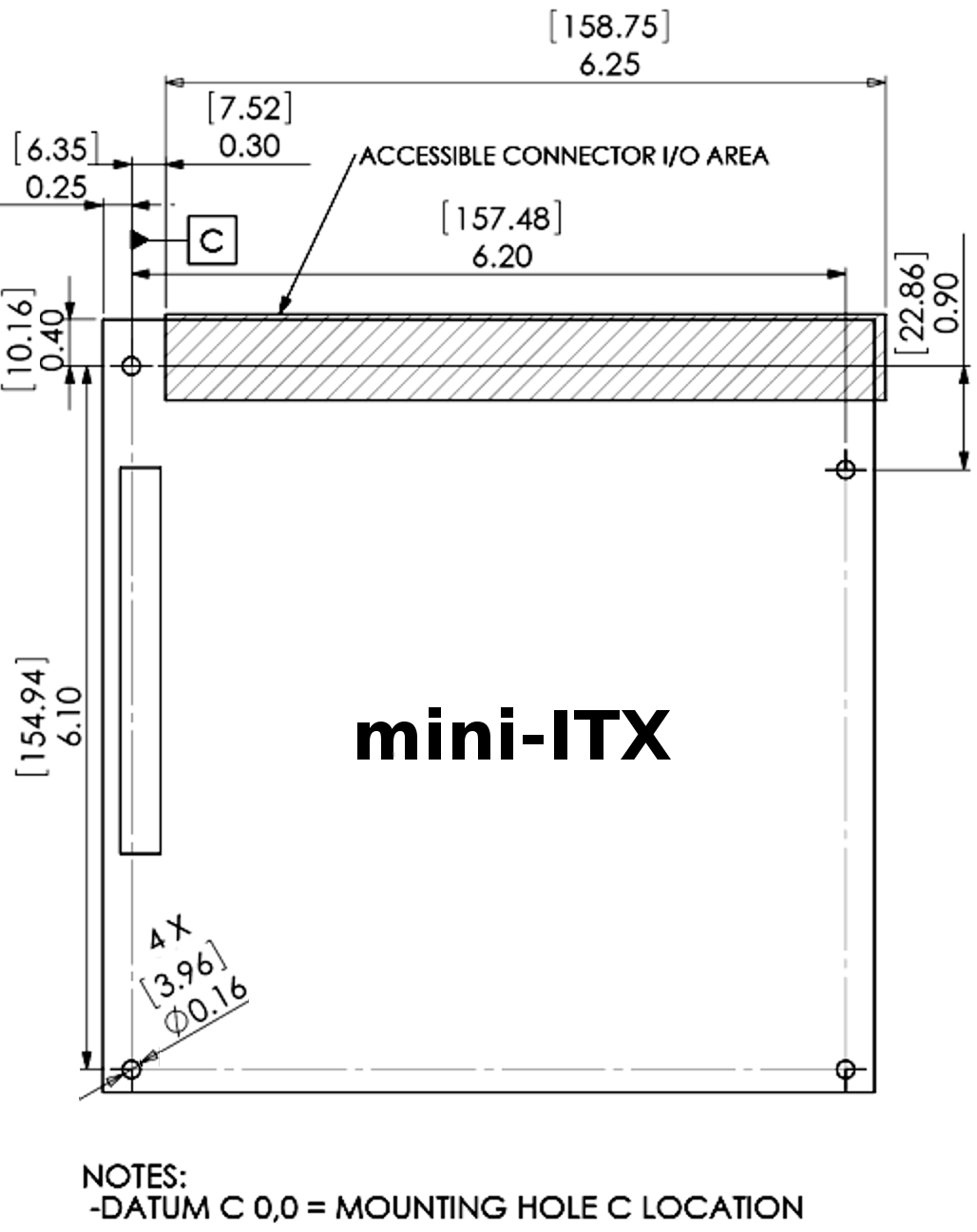

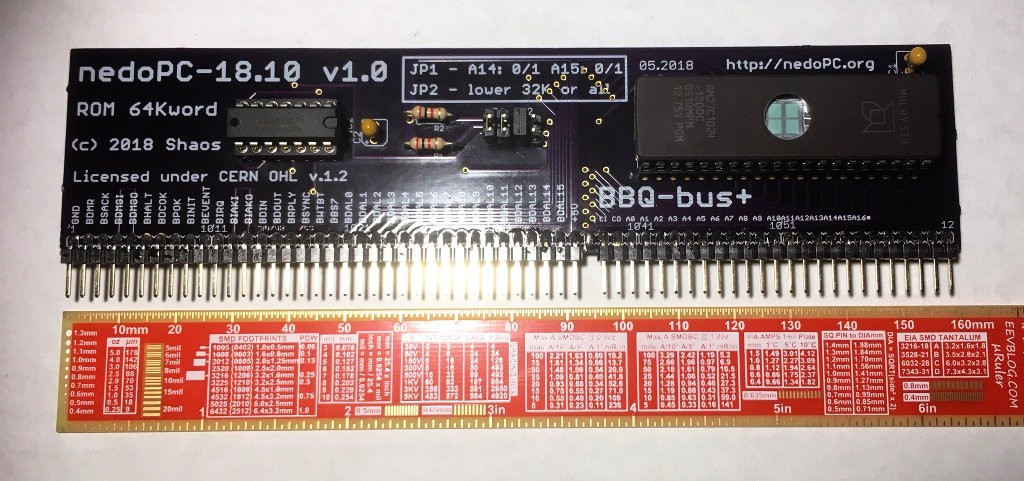

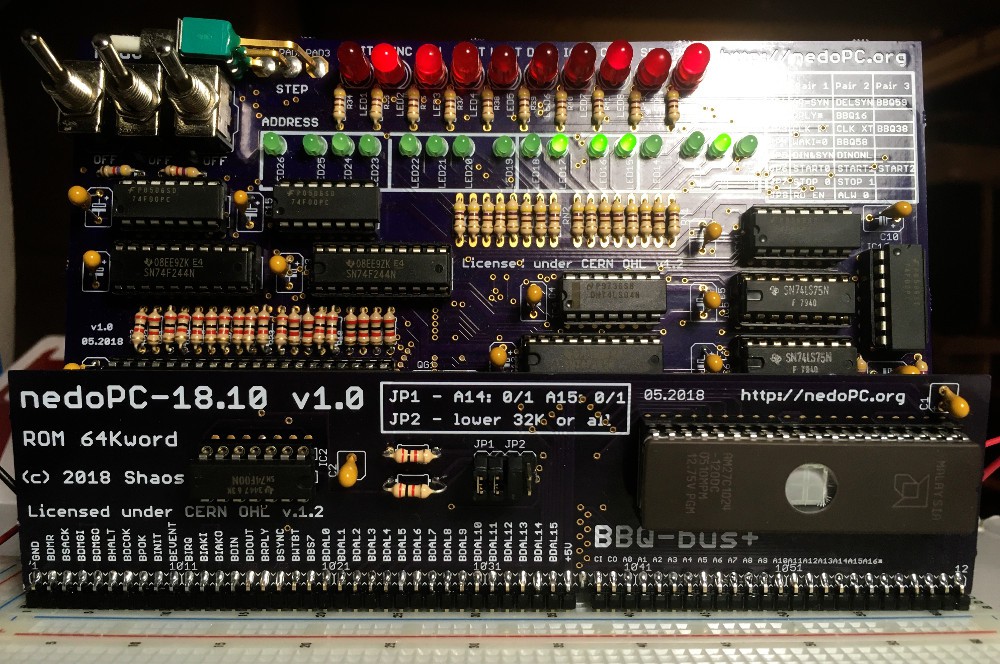

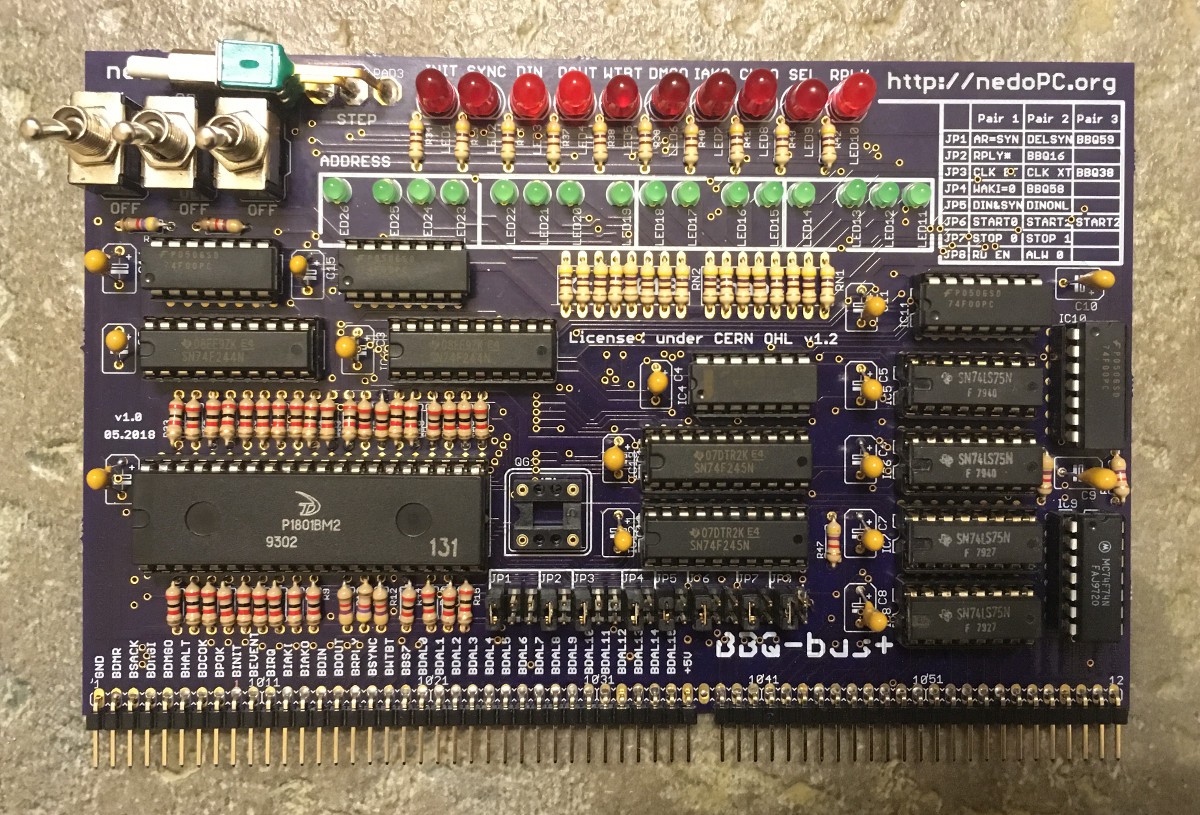

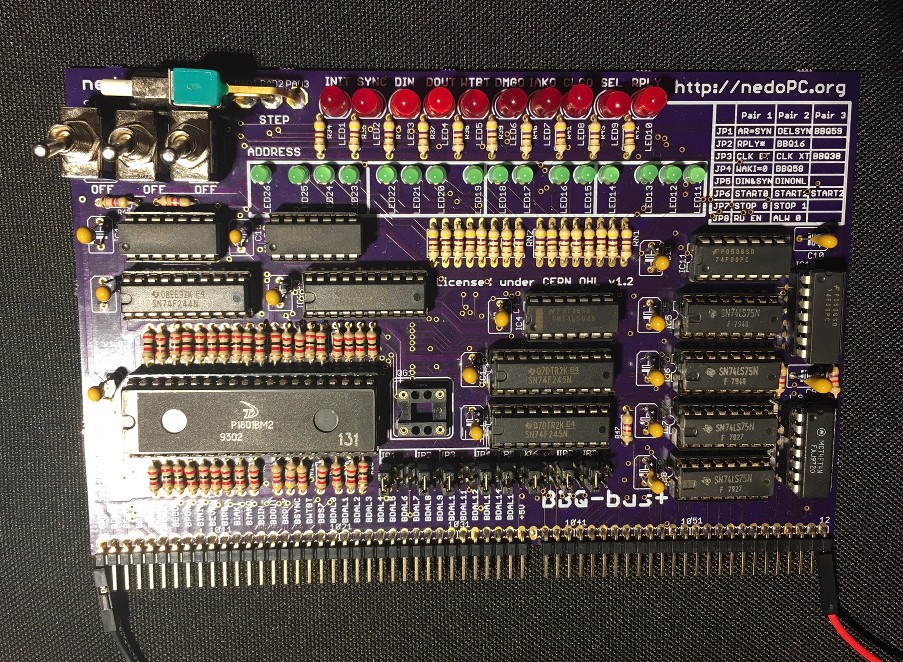

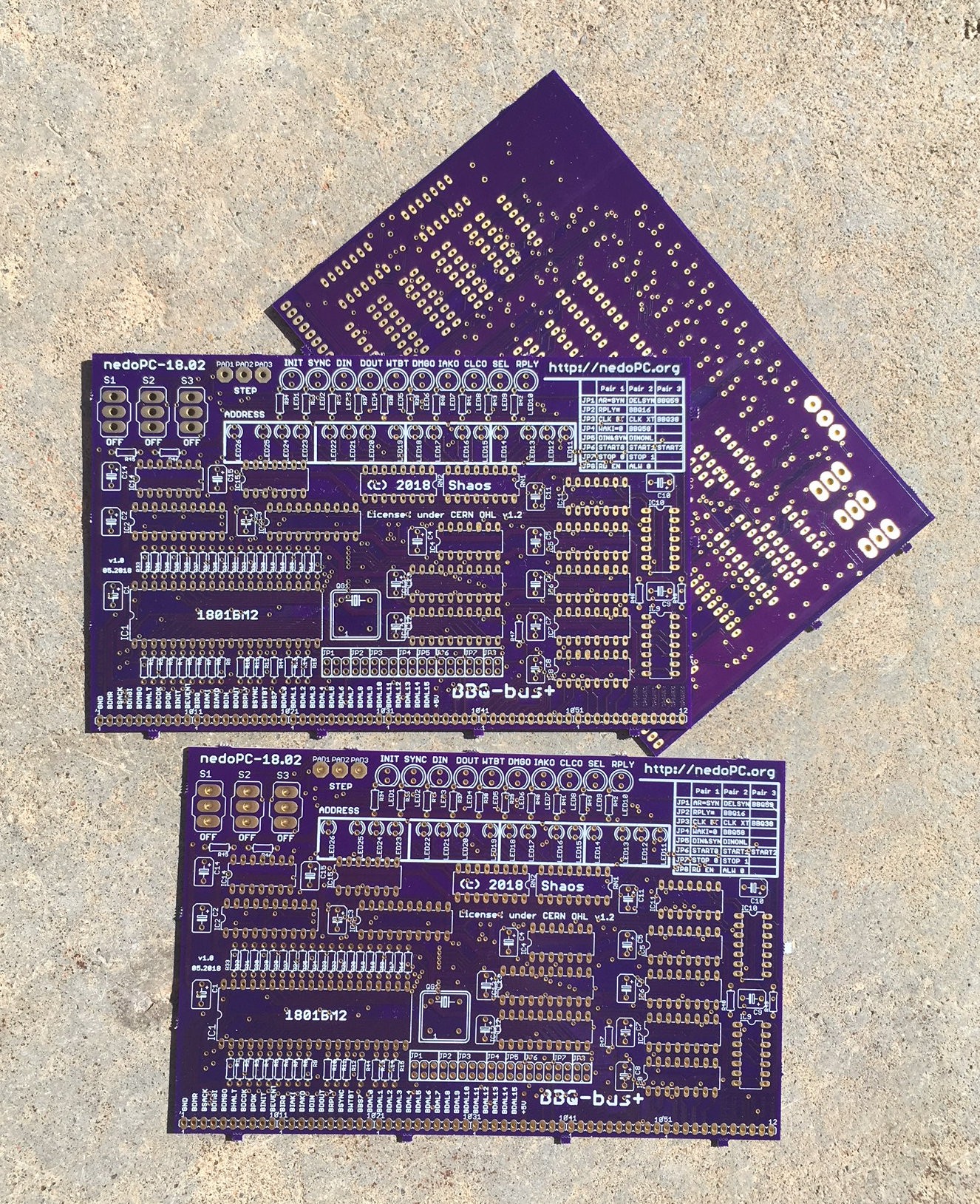

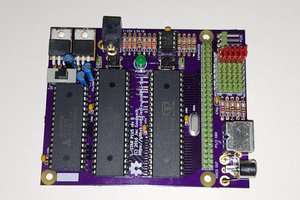

At present PDP-11 computer systems are mostly forgotten, but there are PDP-11 compatible Soviet microprocessors still available on eBay (never used "new old stock") as KR1801VM2 (КР1801ВМ2 in Russian) and I'm going to bring PDP-11 of some sort back - I'm designing an open source computer (licensed under CERN OHL v1.2) around that chip (VM2 was 2nd version of Soviet single chip implementation of LSI-11 system [ not a clone!!! ] which could be used to build PDP-11/03 kind of machine) with open source modules and backplane in mini-ITX form factor 170*170mm (see GitLab) that could fit into regular mini-ITX computer case (that is cheap) to make a true 16-bit modern retro computer with PS/2 keyboard (and may be mouse) and connected to [S]VGA monitor:

As you can see design is inspired by famous RC2014 ;)

UPDATE1: On April 26th this project was featured on hackaday.com

https://hackaday.com/2018/04/26/a-mini-itx-pdp-11/

UPDATE2: Mailing list about all nedoPC projects (not only this nedoPC-18 "PDPii"):

https://groups.google.com/d/forum/nedopc

UPDATE3: You can order PDPii printed circuit boards (multiple of 3) from OSHpark:

CPU module: https://oshpark.com/shared_projects/1tyHeC3z

ROM module: https://oshpark.com/shared_projects/84DgcRqv

Mini-ITX spec with all sizes could be found here

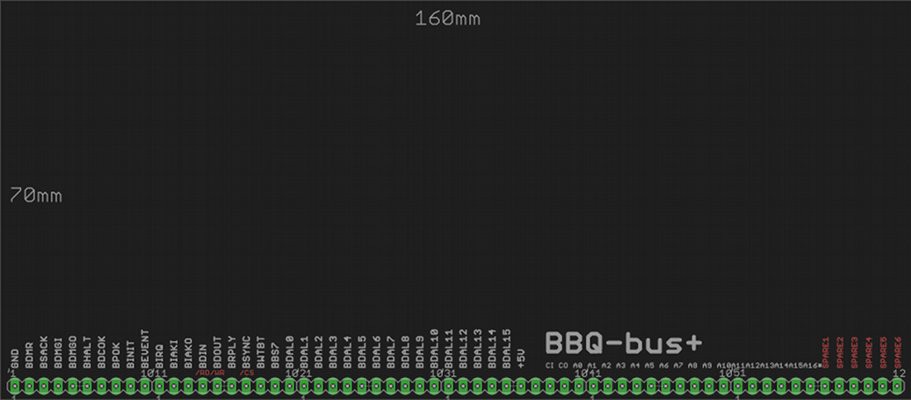

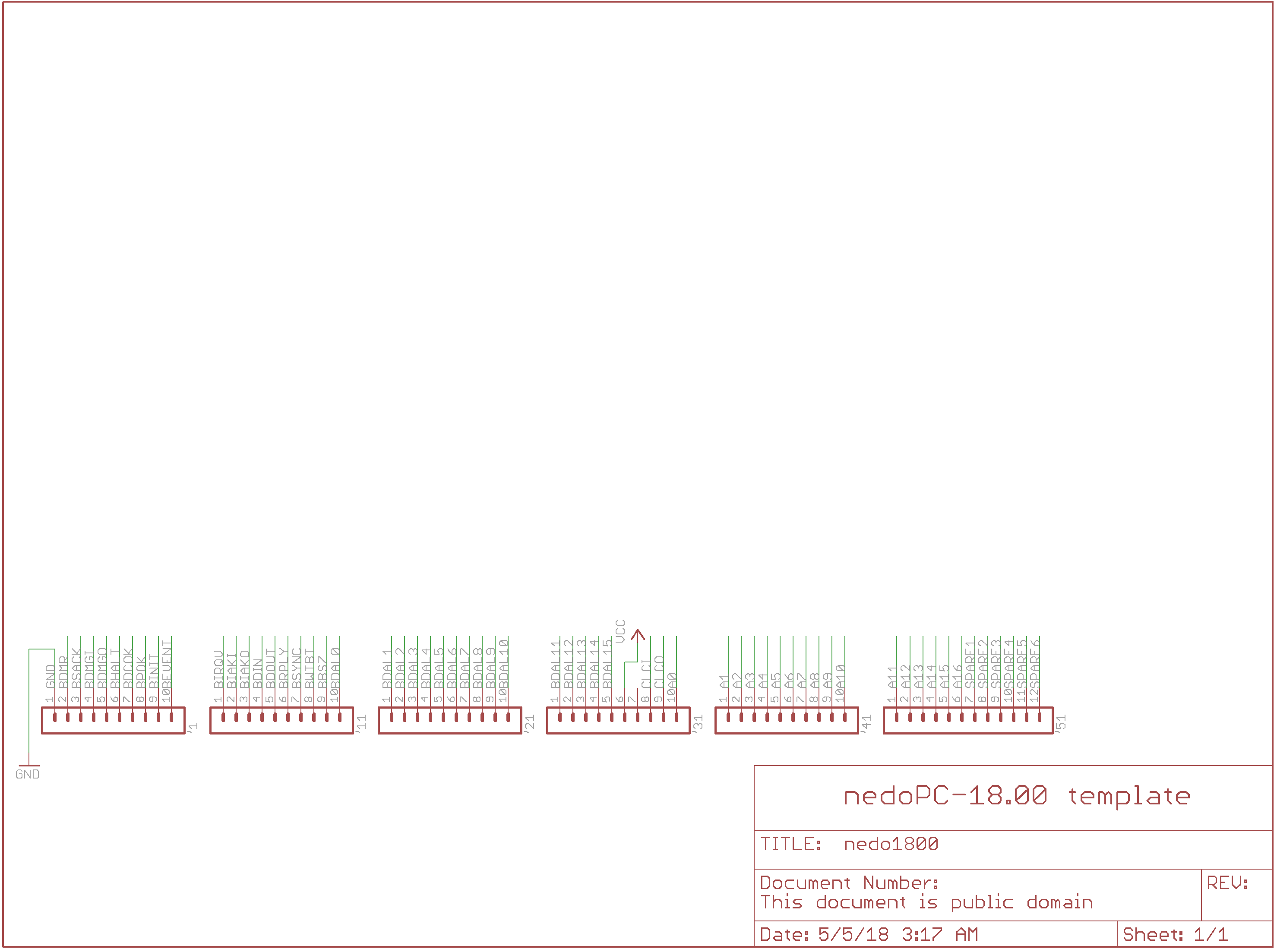

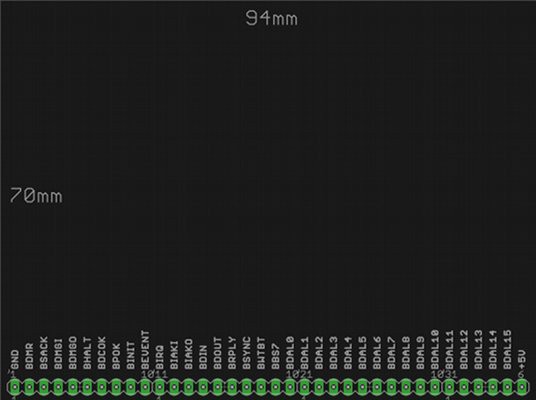

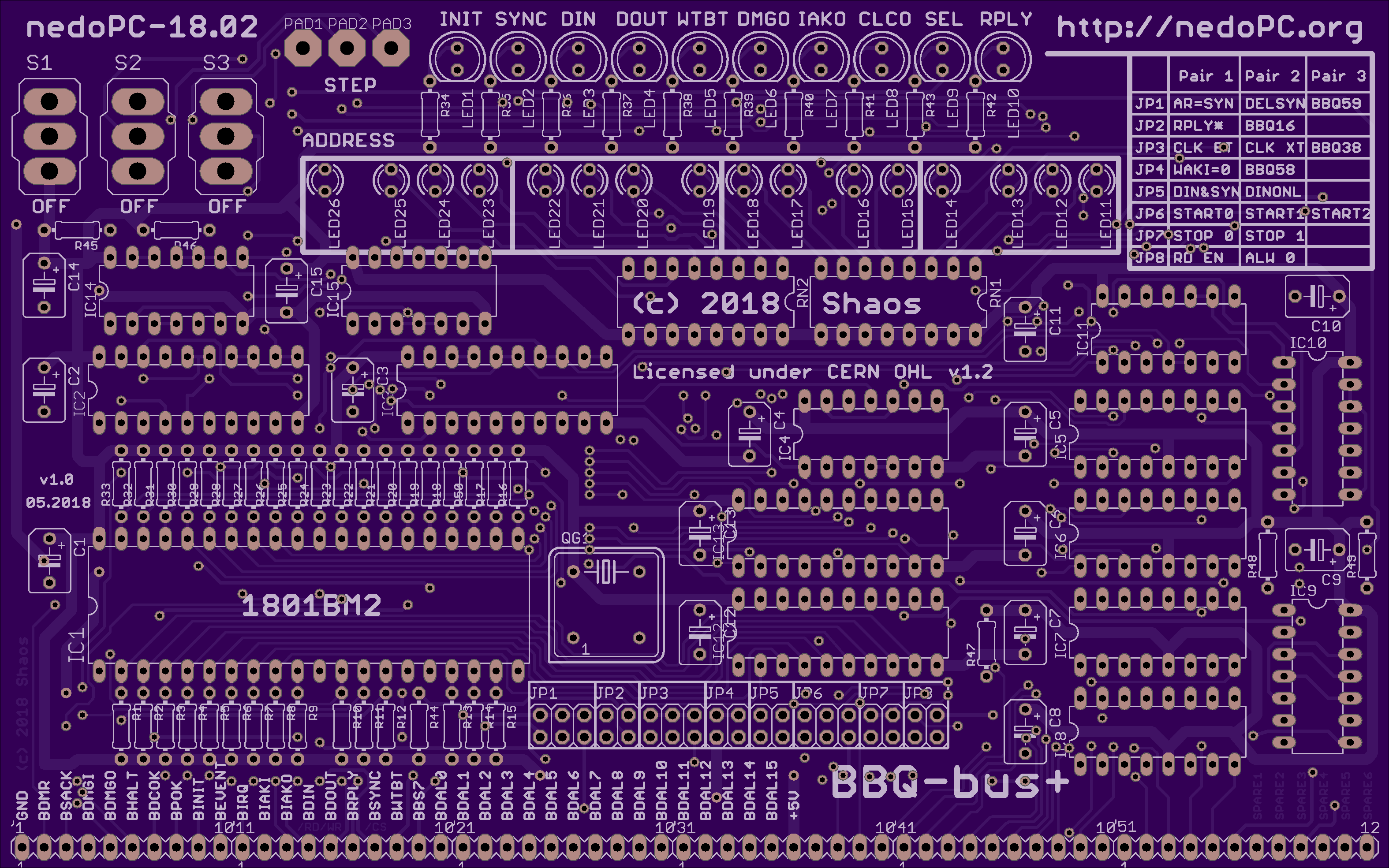

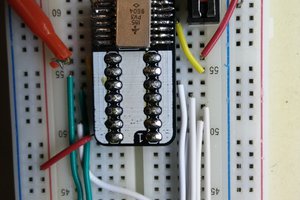

I didn't want to use Q-bus (called "LSI-11 bus" in earlier DEC documentation) as is (in it's original edge-connector form) because it's huge and almost half of contacts are not used, so I put all meaningful signals of Q-bus in 1-row header (slightly re-arranged) and in the same row (after 1 missed pin) I added all other signals from VM2 microprocessor and also de-multiplexed and inverted address lines - there are no modern ICs that could decode multiplexed Q-bus with proper handshaking natively (except for some number of old Soviet memory chips that mostly defective) so presence of already demultiplexed and inverted address will help to connect regular memory RAM and ROM chips. So it's 62-pin header (37th pin is missing) that could fit in 6.3 inches ( or 160mm that is coincidentally a limit for Eagle v5 Standard Edition that I own since 2007 ; ) and collectively I call this interface "Bread-Board friendly Q-bus extended" or BBQ-bus+ :)

| Position | Name (bold if Q-bus) | Where connected |

| 1 | GND | Ground - pin 1 and 20 of VM2 |

| 2 | BDMR L | /DMR - pin 12 of VM2 |

| 3 | BSACK L | /SACK - pin 13 of VM2 |

| 4 | BDMGI L | Daisy chained BDMGO |

| 5 | BDMGO L | /DMGO - pin 14 of VM2 |

| 6 | BHALT L | /HALT - pin 29 of VM2 |

| 7 | BDCOK H | /DCLO - pin 26 of VM2 |

| 8 | BPOK H | /ACLO - pin 25 of VM2 |

| 9 | BINIT L | /INIT - pin 27 of VM2 |

| 10 | BEVENT L | /EVNT - pin 30 of VM2 |

| 11 | BIRQ4 L | /VIRQ - pin 28 of VM2 |

| 12 | BIAKI L | Daisy chained BIAKO |

| 13 | BIAKO L | /IAKO - pin 24 of VM2 |

| 14 | BDIN L | /DIN - pin 22 of VM2 |

| 15 | BDOUT L | /DOUT - pin 18 of VM2 |

| 16 | BRPLY L | /RPLY - pin 17 of VM2 |

| 17 | BSYNC L | /SYNC - pin 21 of VM2 |

| 18 | BWTBT L | /WTBT - pin 19 of VM2 |

| 19 | BBS7 L | Logical 0 if A15=A14=A13=1 |

| 20 | BDAL0 L | /AD0 - pin 9 of VM2 |

| 21 | BDAL1 L | /AD1 - pin 8 of VM2 |

| 22 | BDAL2 L | /AD2 - pin 7 of VM2 |

| 23 | BDAL3 L | /AD3 - pin 6 of VM2 |

| 24 | BDAL4 L | /AD4 - pin 5 of VM2 |

| 25 | BDAL5 L | /AD5 - pin 4 of VM2 |

| 26 | BDAL6 L | /AD6 - pin 3 of VM2 |

| 27 | BDAL7 L | /AD7 - pin 2 of VM2 |

| 28 | BDAL8 L | /AD8 - pin 39 of VM2 |

| 29 | BDAL9 L | /AD9 - pin 38 of VM2 |

| 30 | BDAL10 L | /AD10 - pin 37 of VM2 |

| 31 | BDAL11 L | /AD11 - pin 36 of VM2 |

| 32 | BDAL12 L | /AD12 - pin 35 of VM2 |

| 33 | BDAL13 L | /AD13 - pin 34 of VM2 |

| 34 | BDAL14 L | /AD14 - pin 33 of VM2 |

| 35 | BDAL15 L | /AD15 - pin 32 of VM2 |

| 36 | PWR5V | +5V (switchable) - pin 40 of VM2 |

| 37 | NOT CONNECTED (a key) | |

| 38 | CLCI | CLCI - pin 16 of VM2 |

| 39 | CLCO | CLCO - pin 15 of VM2 |

| 40 | A0 | Latched inverted /AD0 |

| 41 | A1 | Latched inverted /AD1 |

| 42 | A2 | Latched inverted /AD2 |

| 43 | A3 | Latched inverted /AD3 |

| 44 | A4 | Latched... |

SHAOS

SHAOS

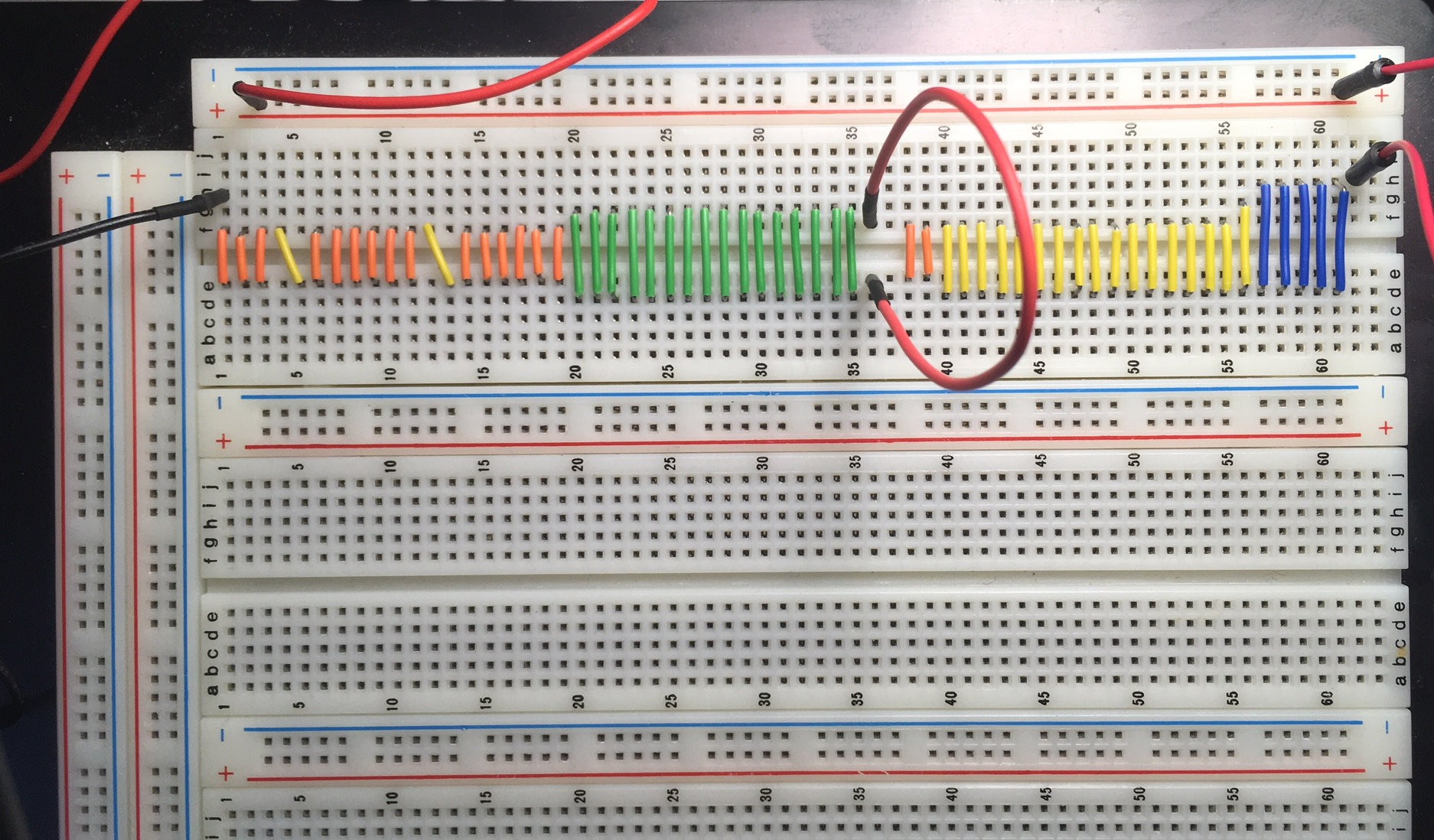

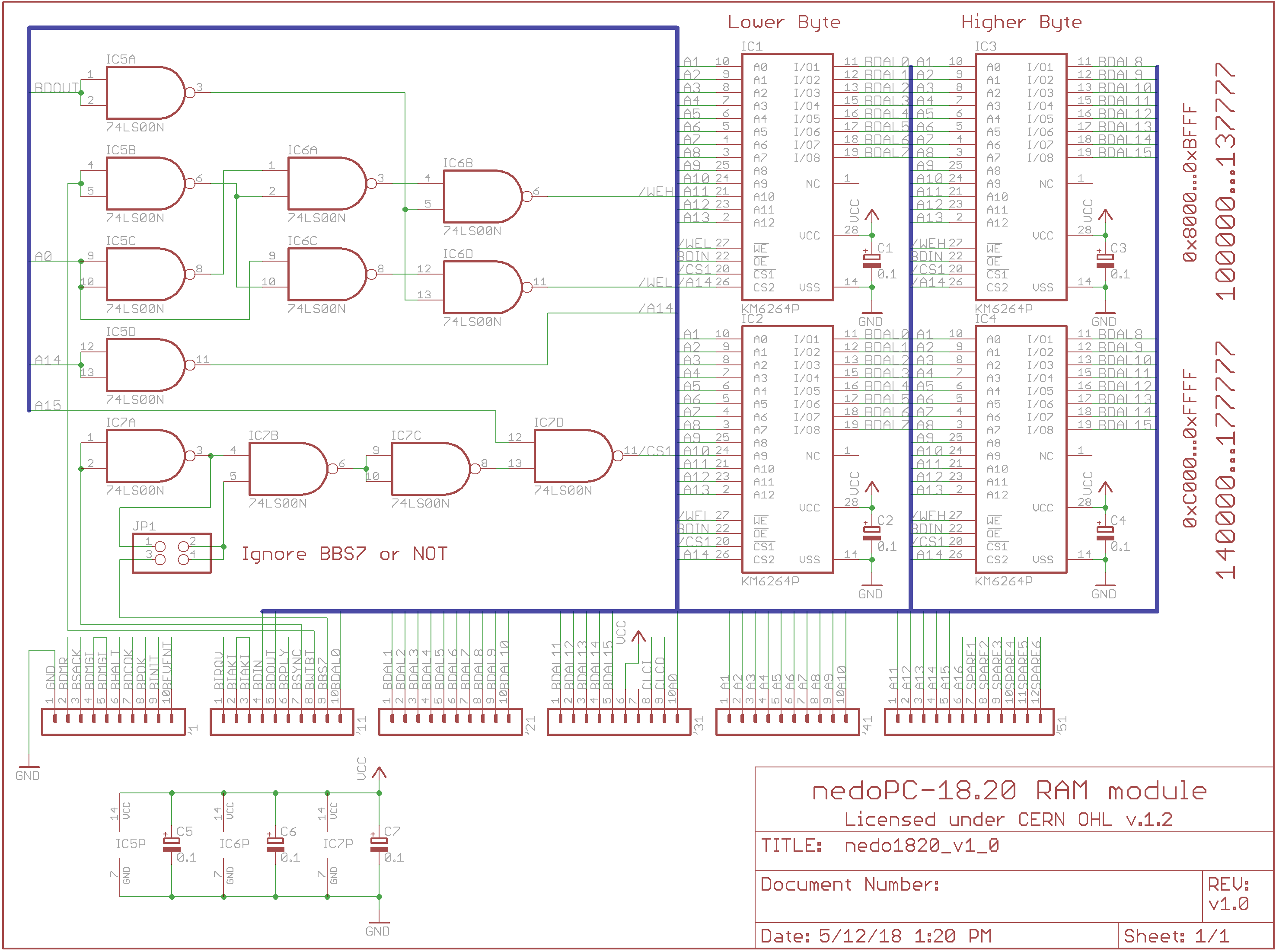

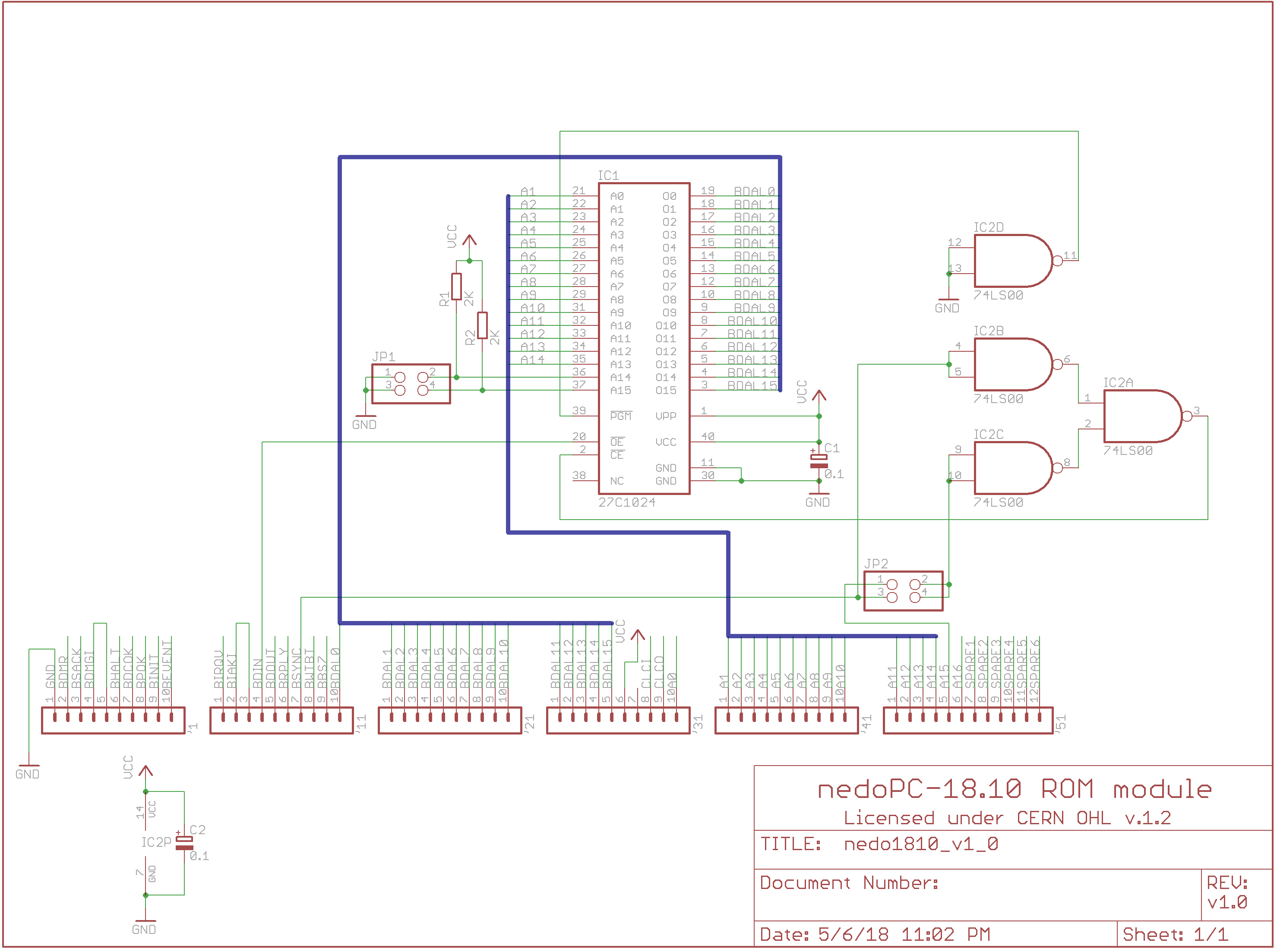

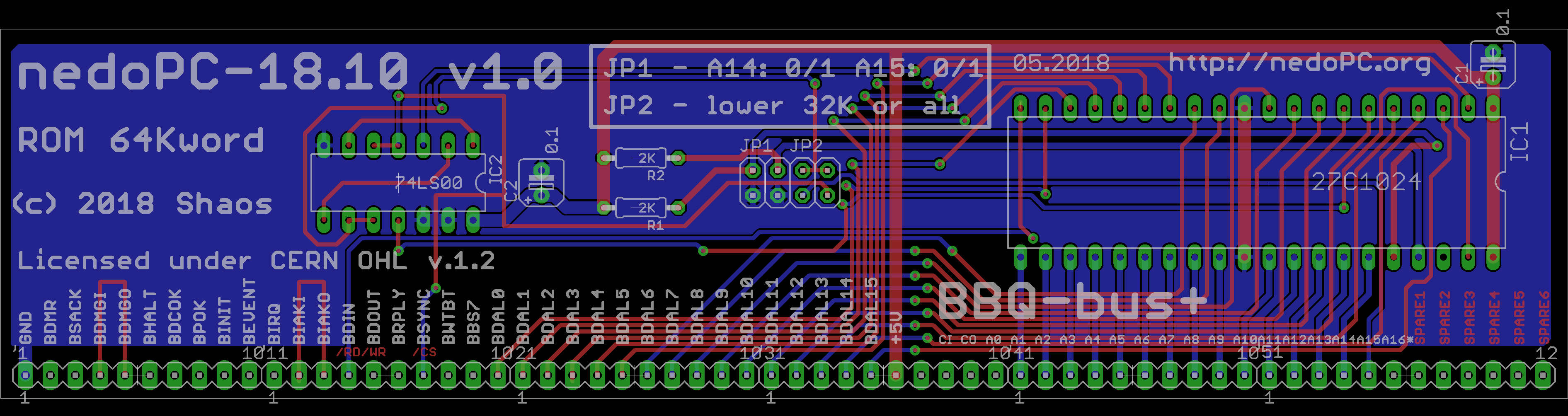

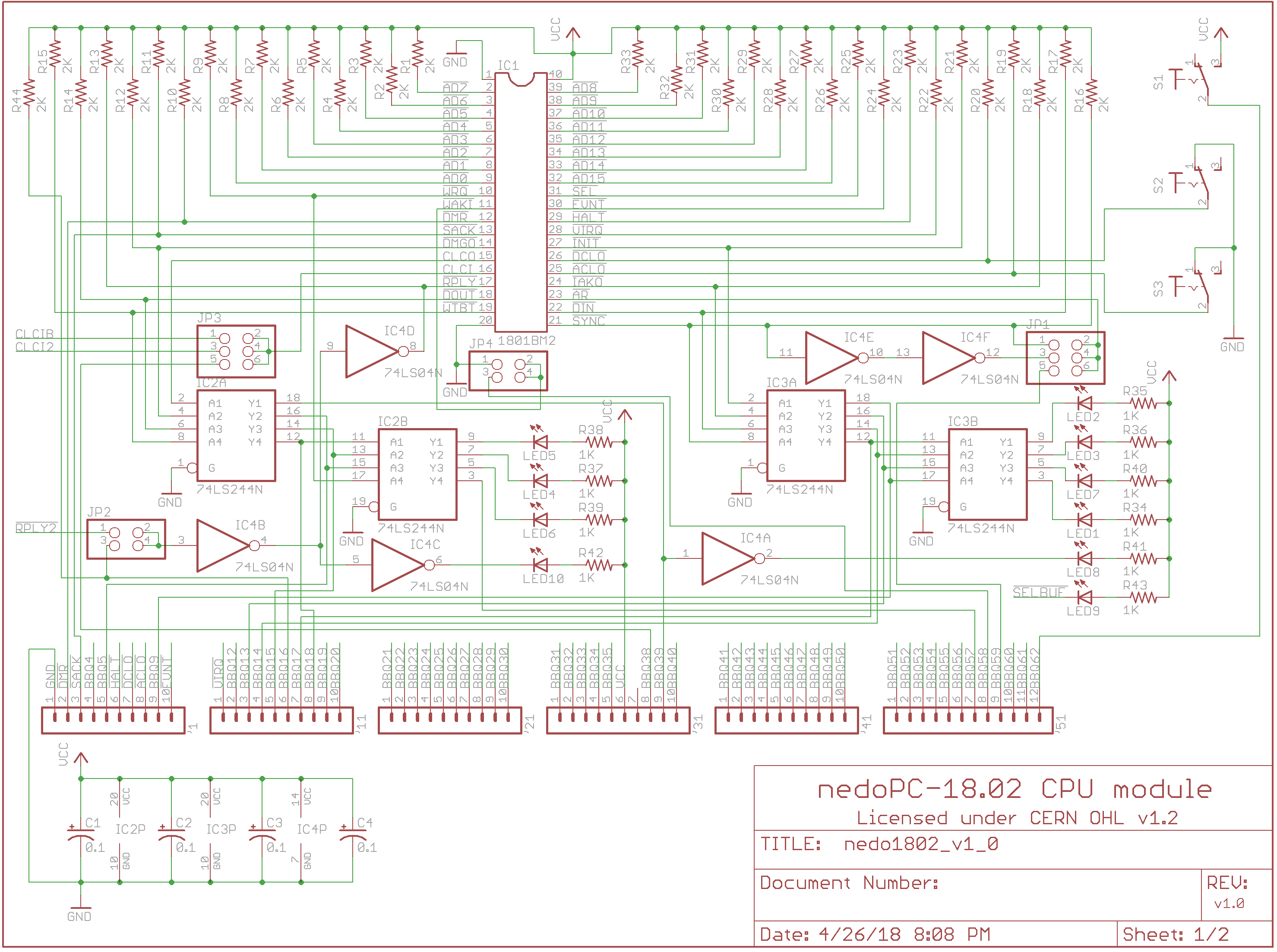

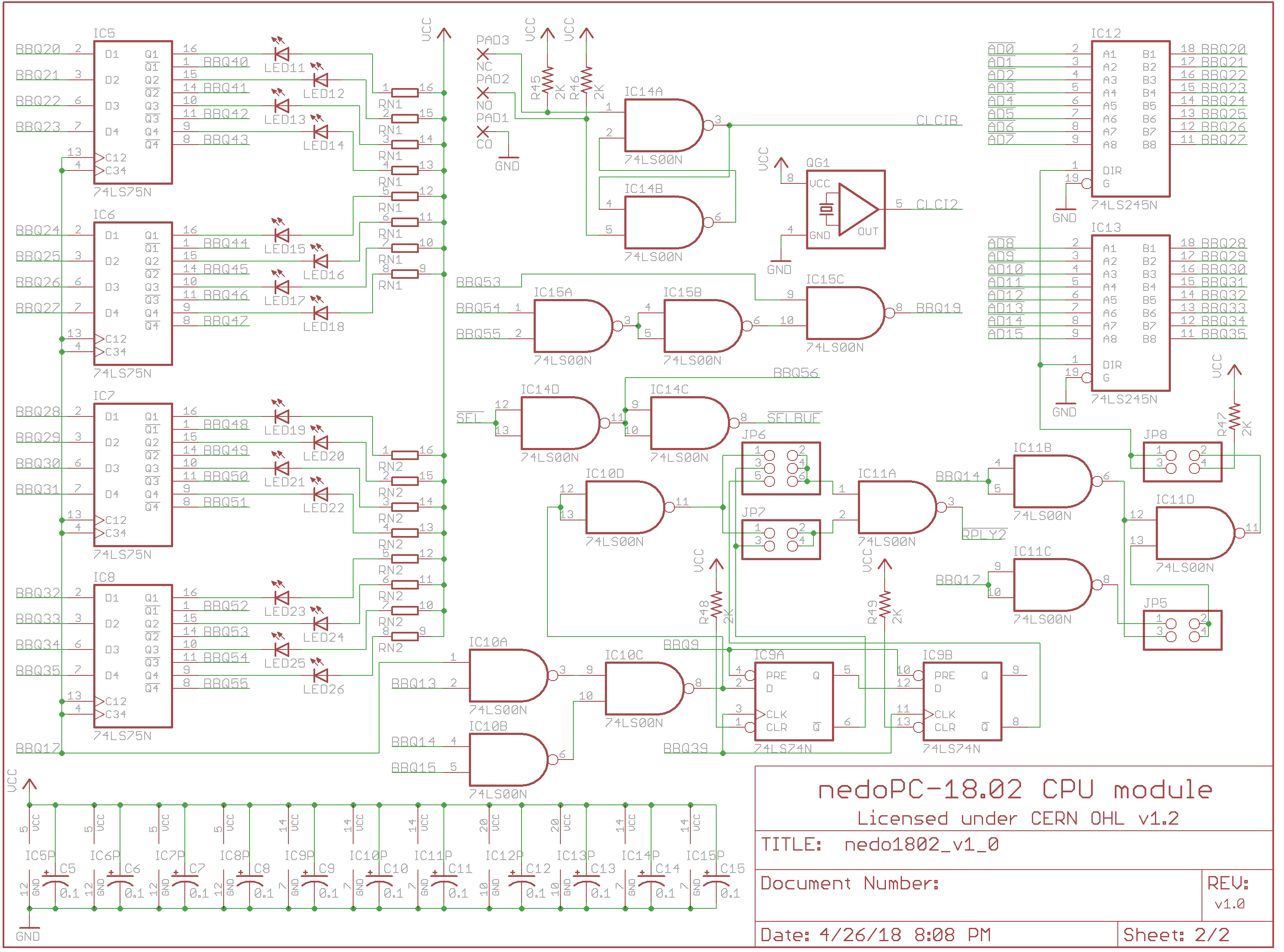

Schematics:

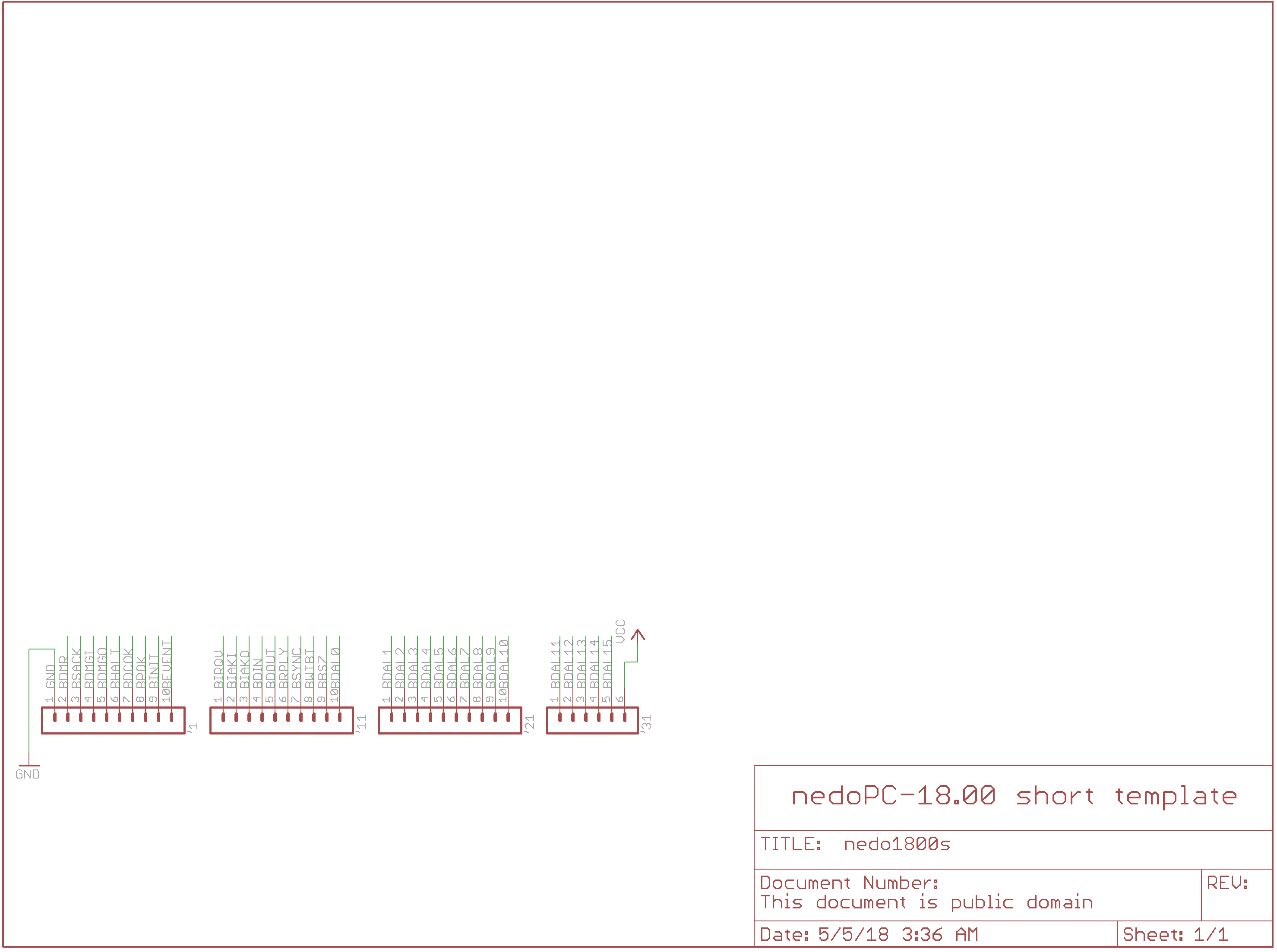

Schematics: Here you need to do address latch on your own, but PCB might be much smaller.

Here you need to do address latch on your own, but PCB might be much smaller.

Jac Goudsmit

Jac Goudsmit

Plasmode

Plasmode

Tyler Bourne

Tyler Bourne

EtchedPixels

EtchedPixels

For reasons that are entirely unrelated to either computing or the history thereof, in really any meaningfully establishable way at all, the name of your project invokes in my mind the name and character of an extraordinarily prominent user and "content creator" (ugh, I hate terms like that) on YouTube.