You might remember my musings with the XOR gate with interlocked NPN transistors discussed at Bipolar XOR gate with only 2 transistors

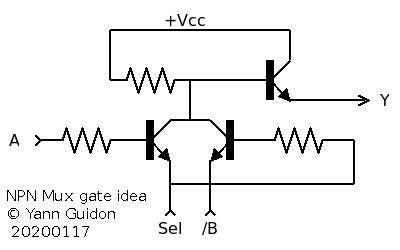

But thinking about how XOR is done with pass transistors in CMOS and the structure often creates a MUX, I wondered if I could translate this concept back to bipolar world.

This first result is pretty nice and compact though the circuit is highly unbalanced...

- A is a typical high-impedance input where a high signal is a valid 1.

- /B is a negated low-impedance input that must be shorted to -V to make a valid 1. Another transistor can do the trick though that would create another delay...

- Sel has to swing High and Low...

But for discrete, parts-constrained circuits, that might work...

The output could be used to directly drive another MUX stage if the next MUX swaps the NPN for PNP (and reverse polarity) though a big MUX could also be built with the single-transistor NPN-ANDN gate to then drive a big CTL AND gate.

Has anyone seen this circuit before ?

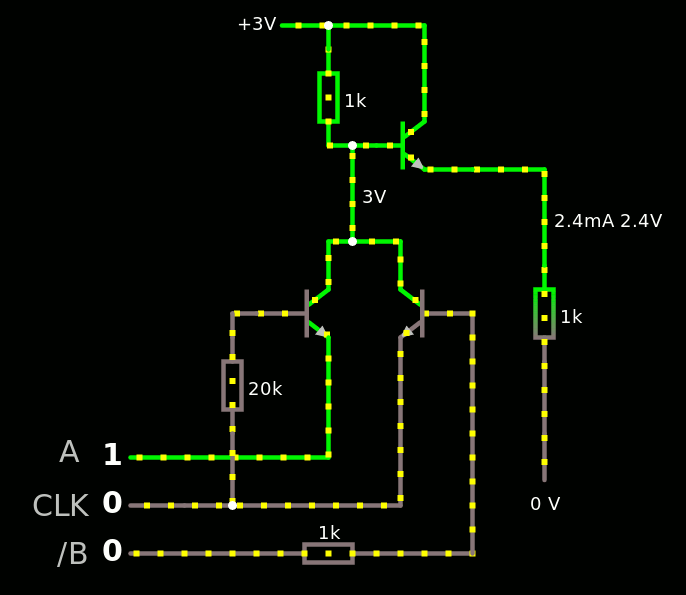

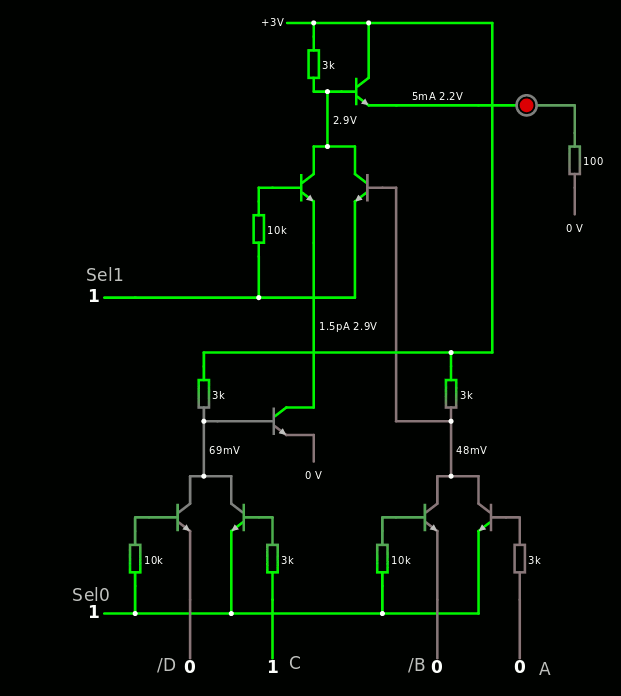

The MUX seems to work well on this Falstad simulation:

Another Falstad sim was required to validate the enhancements : an additional transistor to de-invert /B can be useful...

The source code is :

$ 1 0.000005 10.20027730826997 50 5 43 w 144 112 352 112 3 v 144 400 144 112 0 0 40 3 0 0 0.5 r 352 112 352 176 0 1000 t 304 240 336 240 0 1 0.6163510467707772 0.6473024119705006 100 t 416 240 384 240 0 1 -0.030951365199723496 0.027087887962126838 100 t 352 304 384 304 0 1 0.6173128261844162 0.6352410780104729 100 r 432 112 432 176 0 1000 r 240 304 304 304 0 1000 r 240 240 304 240 0 1000 w 352 176 352 208 2 w 336 224 336 208 0 w 336 208 352 208 0 w 352 208 384 208 0 w 384 208 384 224 0 w 144 400 336 400 0 w 384 400 384 320 0 w 384 288 384 256 0 w 304 304 352 304 0 L 240 304 208 304 0 1 false 3 0 L 240 240 208 240 0 1 false 3 0 L 240 368 208 368 0 1 false 3 0 w 336 400 384 400 0 w 336 352 336 256 0 w 336 352 432 352 0 w 416 240 432 240 0 w 432 240 432 352 0 t 304 368 336 368 0 1 0.6161066110712008 0.6611227508593843 100 w 352 112 432 112 0 w 432 240 432 176 0 w 336 400 336 384 0 w 464 208 384 208 0 r 240 368 304 368 0 1000 t 464 208 496 208 0 1 -2.924032495012093 0.07596750308398237 100 w 432 112 496 112 0 w 496 112 496 192 0 r 496 288 496 400 0 1000 w 384 400 496 400 0 w 496 224 496 288 3 38 18 2 0 3 B\sLow 38 18 1 0 3 B\sHigh 38 19 2 0 3 A\sLow 38 19 1 0 3 A\sHigh 38 20 2 0 3 CLK\slow 38 20 1 0 3 CLK\shigh

I have re-wired the B base resistor : it's now a pull-up that is shorted to 0V by the main SEL input. I added another transistor on the B input to get rid of the inversion (and some isolation).

The output is inverted with an common collector output stage, though an open collector is also possible, it would re-invert the value and make it a non-inverting MUX.

The select input and transistor can be shared by more than one MUX, which makes it an attractive solution for selecting a whole bus for example.

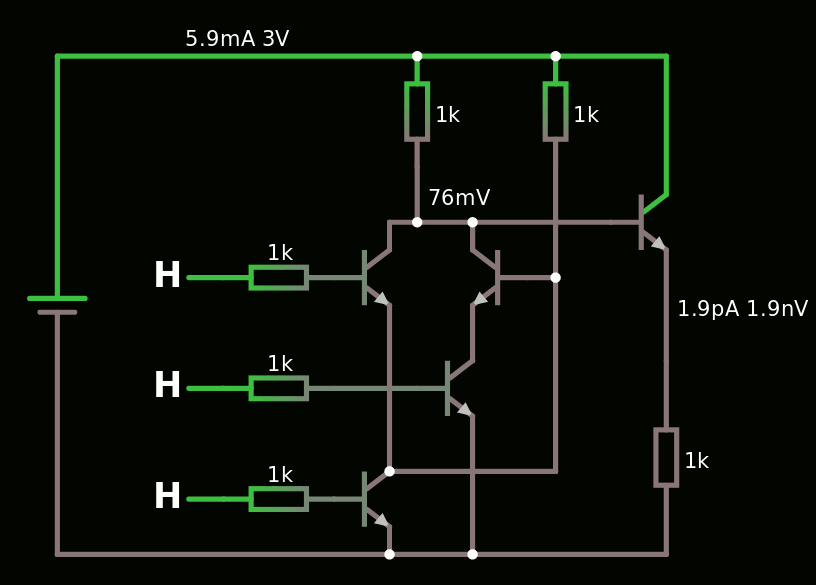

Here is the non-inverting MUX with open collector output :

So this is the version that would solve the problem found by @roelh :-D

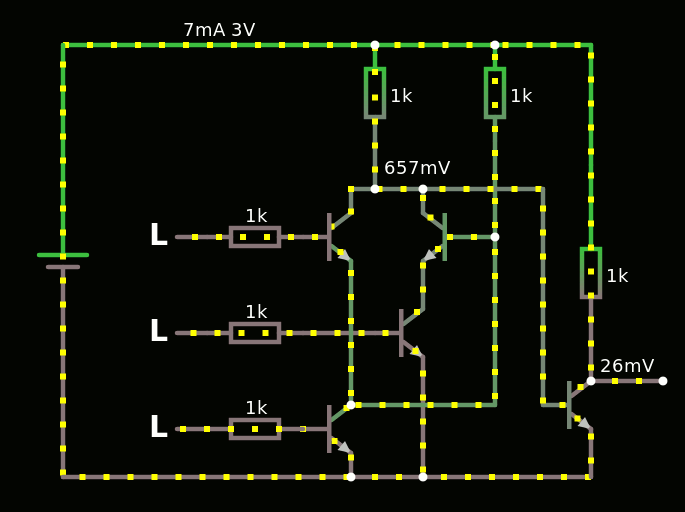

And when you have a MUX2, you can cascade 3 of them to build a MUX4 :-)

There are inversions here and there but some are opportunities to save a transistor.

Yann Guidon / YGDES

Yann Guidon / YGDES

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.

Nice MUX gate, Yann ! Could also be used for DCTL when base resistors are removed.

Are you sure? yes | no

but that could fry the base if it is not protected...

Are you sure? yes | no

In DCTL, the base current is limited by the collector resistor of the previous stage, so the base resistor can be omitted. You just have to be careful when a stage drives several inputs.

Are you sure? yes | no

I overlooked that detail, yes :-)

Are you sure? yes | no