gelFORTH

a Forth for interactive hardware design on the PSoC 5LP

a Forth for interactive hardware design on the PSoC 5LP

To make the experience fit your profile, pick a username and tell us what interests you.

We found and based on your interests.

gelFORTH-AndreasWagner-slides-ForthDay.pdfhttp://www.youtube.com/watch?v=ASgBoKisWac&t=45m48sAdobe Portable Document Format - 7.46 MB - 11/20/2016 at 18:32 |

|

|

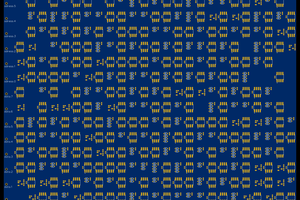

Lately I’ve been writing @ and ! words that do more. For instance, I have the Cypress PSoC 5LP bitstream that I am reverse engineering for gelFORTH:

!bitstream ( startpoint endpoint --) takes the plain-text human readable routing path coordinates as parameters, and maps them to bitstream using Mill’s Methods, an approach similar to the one described in the paper From Bitstream to Netlist. !bitstream effectively maps netlist to bitstream and stores it to the live PSoC over the SWD interface or into a configuration blob.

bitstream@ ( endpoint -- startpoint) takes the endpoint reference and gets the startpoint mapped to it. This is the “from bitstream to netlist” word.

endpoint need not be an individual routing switch.

Mill’s methods work at different levels of granularity. If they can’t

yet isolate a switch, maybe they can isolate a tile. Conversely, if bits

within a register have been isolated but not the register bytes, the bytes

can be viewed as a single overlapping site because we’ve found how the

pattern repeats across those tiles. The pattern may repeat across tiles

with identical structure or in the same tile but across different

projects/bitstreams. The endpoint could also just be: The PSoC 5LP.

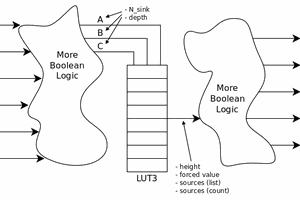

So, these fetch and store words don’t just fetch and store to a memory address, they also do a lot of heavy lifting. After !bitstream and bitstream@

have reverse engineered the bitstream automatically, these routing

words can be compiled to a simpler formula. Looking at Mill’s

Methods you might notice that they look a lot like Quine-McCluskey

or Karnaugh maps in that the mapping function is determined by what

varies and what doesn’t. Sounds like I could even make them defining

words for defining new @ and ! words.

I mentioned in my gelFORTH talk on Forth Day that on a CPLD or FPGA device with a configurable routing fabric, @ and ! do not just fetch and store values from some memory address. On such a configurable device the ! must actually configure a route to the said resource and @

references that variable source of data. These words are equivalent but

sometimes they do more. I may just rename the minimized, device

resident forms of the words !bitstream and bitstream@ to just ! and @ Parallelism is implicit by the way.

Thanks Ed0 for pointing me to that paper!

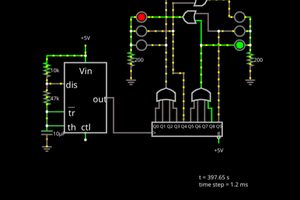

I'm cross-referencing the TRMs with the DSI patent by looking at how the addressing scheme connects the two in a way that makes mathematical sense... and well, I can now compile an XOR gate from gForth to the UDB + routing/DSI system and light up the blue led when I set either of the input pins with my Bus Pirate.

As I had hoped, the PLDs are also reconfigurable during operation, not just the DSI through the Dynamic Configuration RAM.

At first I tried to halt the PSoC before writing the configuration bytes over SWD. But for this to work, I needed to wipe the entire PSoC and write the configuration bytes over SWD without halting.

I used the mostly complete (?) openocd support for the KitProg and PSoC 5LP (by @cyrozap and Andreas Färber) to read and write the configuration bytes from extensible Forth over the tcl rpc interface.

I've been doing a deep brainstorm on how best to factor the UDB, Routing, and DSI code such that it will work well for partial dynamic live reconfiguration, or in a way, compiling Forth words to Boolean algebra (the CPLD) from the interpreter. Once I've figured more of that out, cleaned-up my experiments, and reached some stability in my approach I think I can release the code to the world. Yay! Thanks for reading!

Create an account to leave a comment. Already have an account? Log In.

Check out the HaD project #eForth for cheap STM8S gadgets - it will tickle your nostalgia even if no UV eraser is needed.

I'd never heard of FORTH, but am looking into ways to rapid prototype PSoC beyond the included cypress blocks. Do you think something like Simulink/Xcos co-design can be possible, or maybe generate netlist to import into PSoC?

Nice talk at SVFIG Forth Day! Will the slides be available?

Thank you Thomas! I'm glad you were able to get in touch with Dr. Ting. I've uploaded the PDF slides to the files section.

Thanks again Andreas! I've had the first mail exchange with Dr. Ting now.

In your talk you mentioned "string diagrams" along with ladder logic. Do you have a pointer to an explanation of this concept?

Here is /u/phalp's comments on string diagrams in Forth: https://www.reddit.com/r/Forth/comments/599lb4/symbols_for_stack_operators/d9e7vqg/?context=9999 and here's one of many blog posts explaining the concept for linear algebra etc: https://graphicallinearalgebra.net/2015/04/30/spoilers-adding-part-2-and-zero/

That's really cool! After your talk I read a bit about category theory and string diagrams, and while I found the concept very intriguing, I couldn't make the match with parallelism or ladder logic. Did you have a chat with the guys from Berkely to discuss parallelism?

https://people.eecs.berkeley.edu/~mangpo/www/papers/chlorophyll-gesture-lctes16.pdf

I'll be talking about gelFORTH at the Silicon Valley Forth Interest Group on Forth Day! http://svfig.github.io/ https://www.meetup.com/SV-FIG/events/234884641/

Really cool paper Ed0! I will have a chance to print it out and read it tomorrow morning. It looks like it has some useful techniques and strategies inside generally applicable to FPGA's as well as CPLD's. Recently I've started refining a semantic web triplestore database and semantic web ontology containing what I have learned. http://hub.darcs.net/pointfree/librefpga-triples Although I have largely understood the UDB array and digital routing fabric by now, I think better tools will be a useful time investment for the Universal Analog Blocks and other stuff on the PSoC going forward especially because the Cypress engineers at the Bay Area Maker Faire told me the analog array will be more difficult to figure out. Thanks Ed0!

Become a member to follow this project and never miss any updates

Al Williams

Al Williams

Tim

Tim

Yann Guidon / YGDES

Yann Guidon / YGDES

Wow! Like a journey back to my youth. It's a good 30+ years since we ran commercial systems from Stephen Pelc and Bess Rather. I miss those days of rows of chips sitting next to the UV eraser... Just kidding, source level debug & real time trace on an STM32 is what allowed C to rule the world. Still miss the FORTH community though.