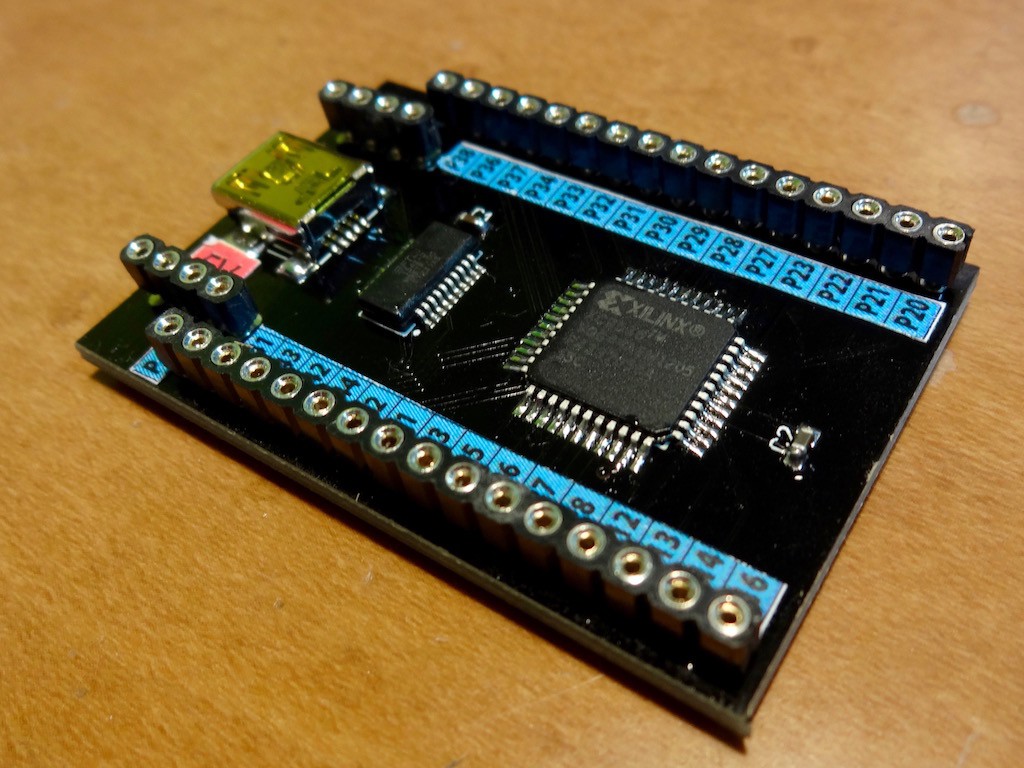

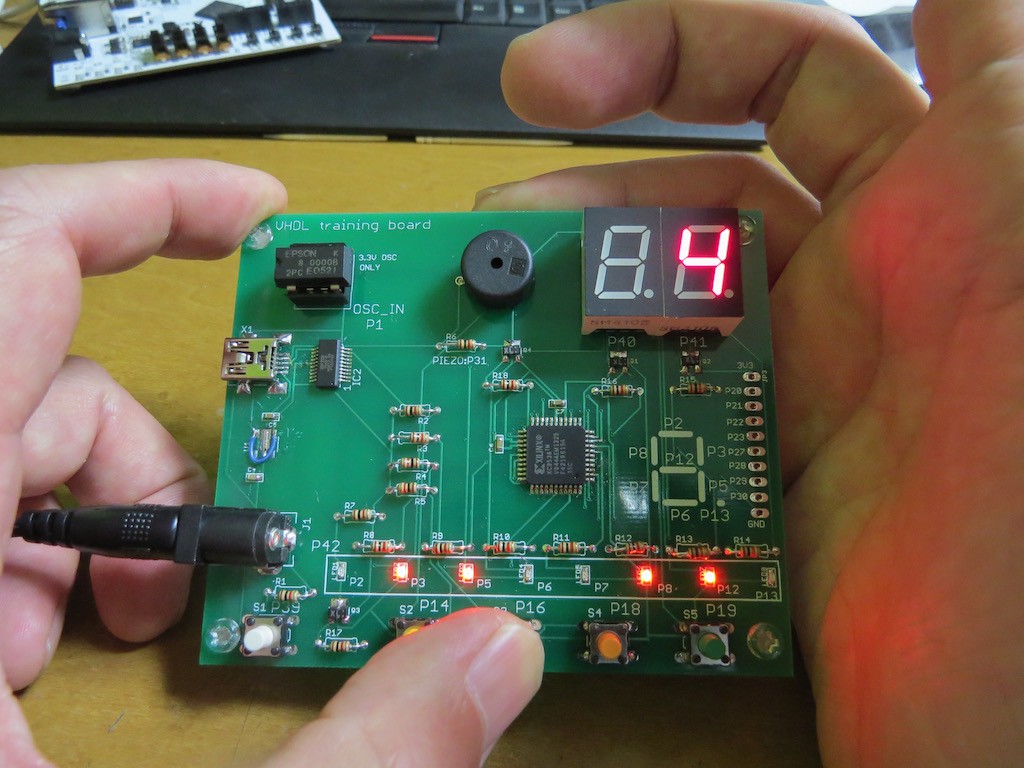

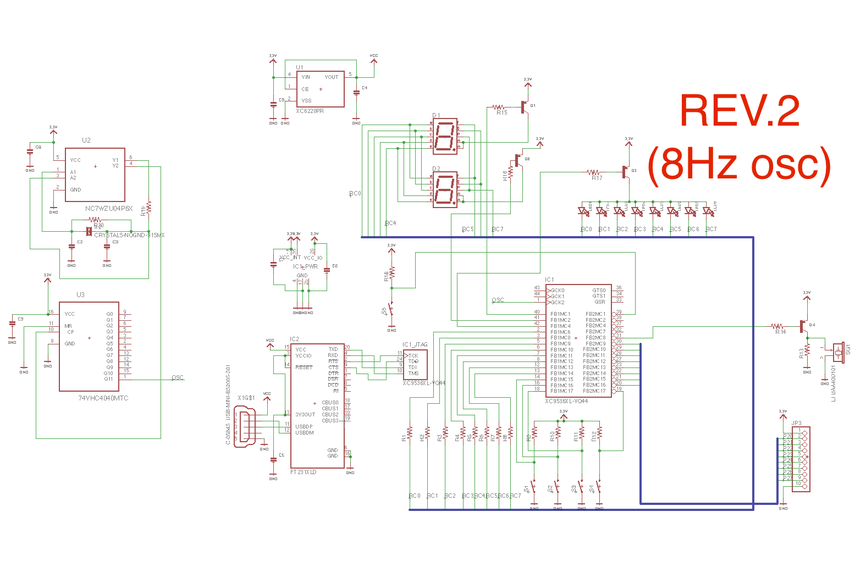

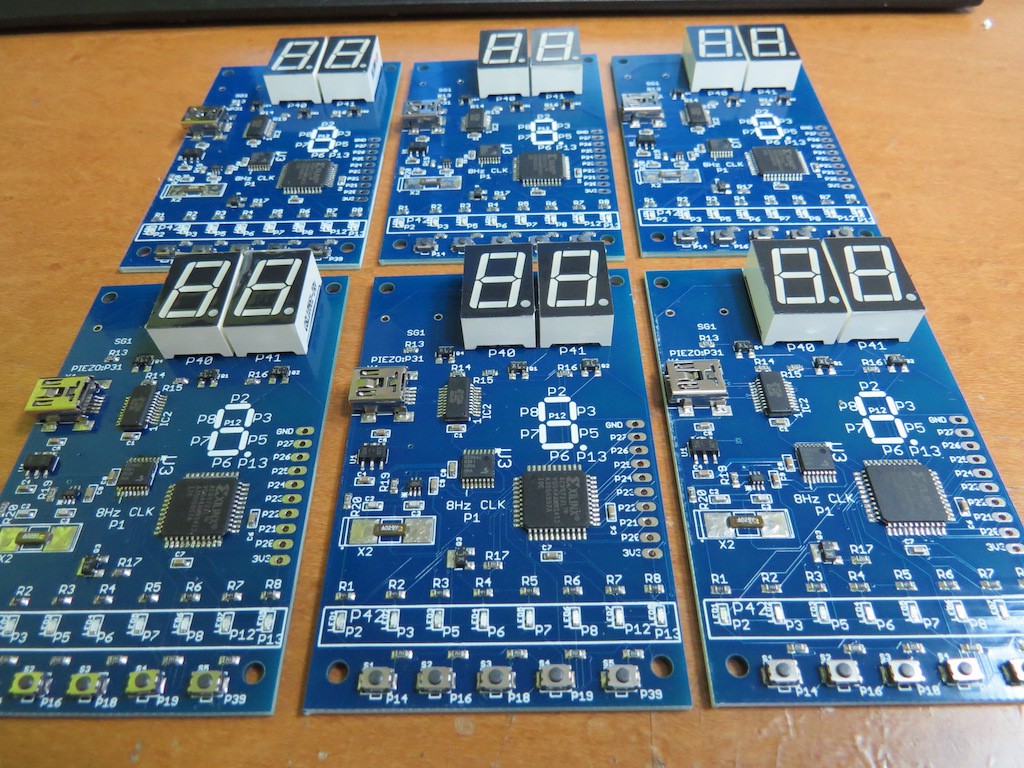

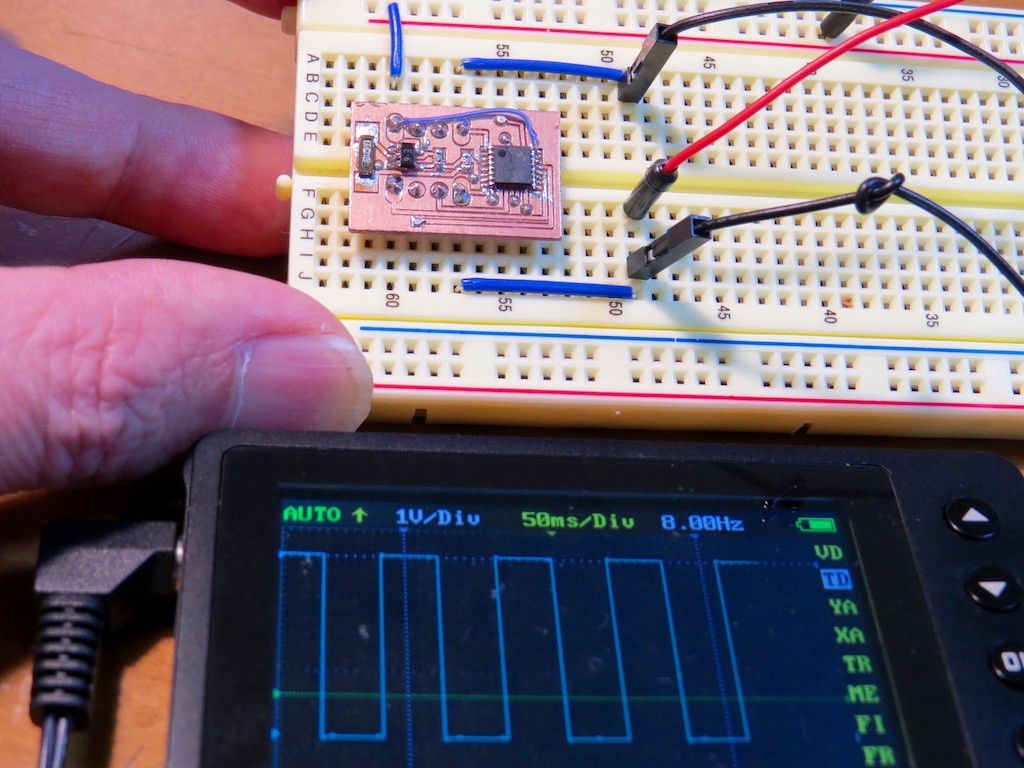

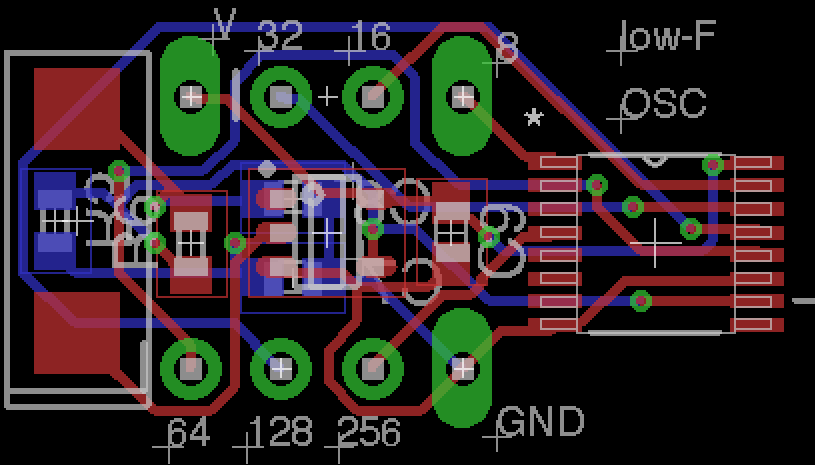

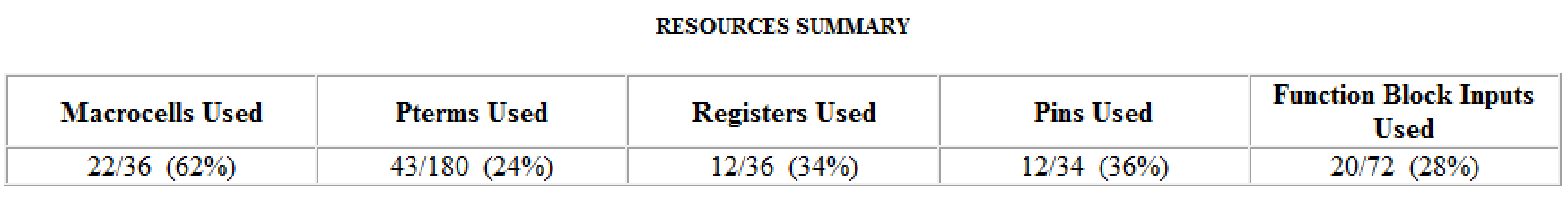

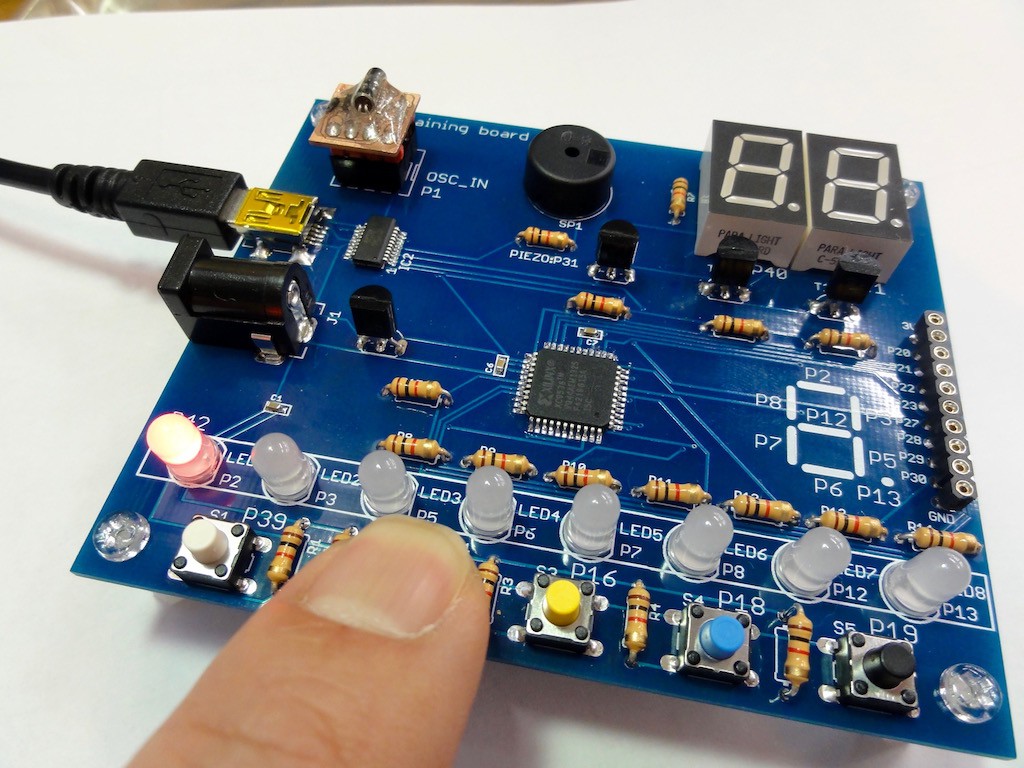

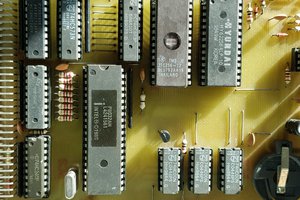

My previous creation of CPLD board in the above picture is surely working for VHDL training, but it is too simplified and we need wiring of switches and LEDs for testing the results. Indeed the macro-cell in this CPLD is just 36 and just switch and LEDs are enough to test its function. (If our project excesses the level of CPLD, then we should jump expensive FPGA board!). This time I made a bit more 'complete' learning board as in the picture below.

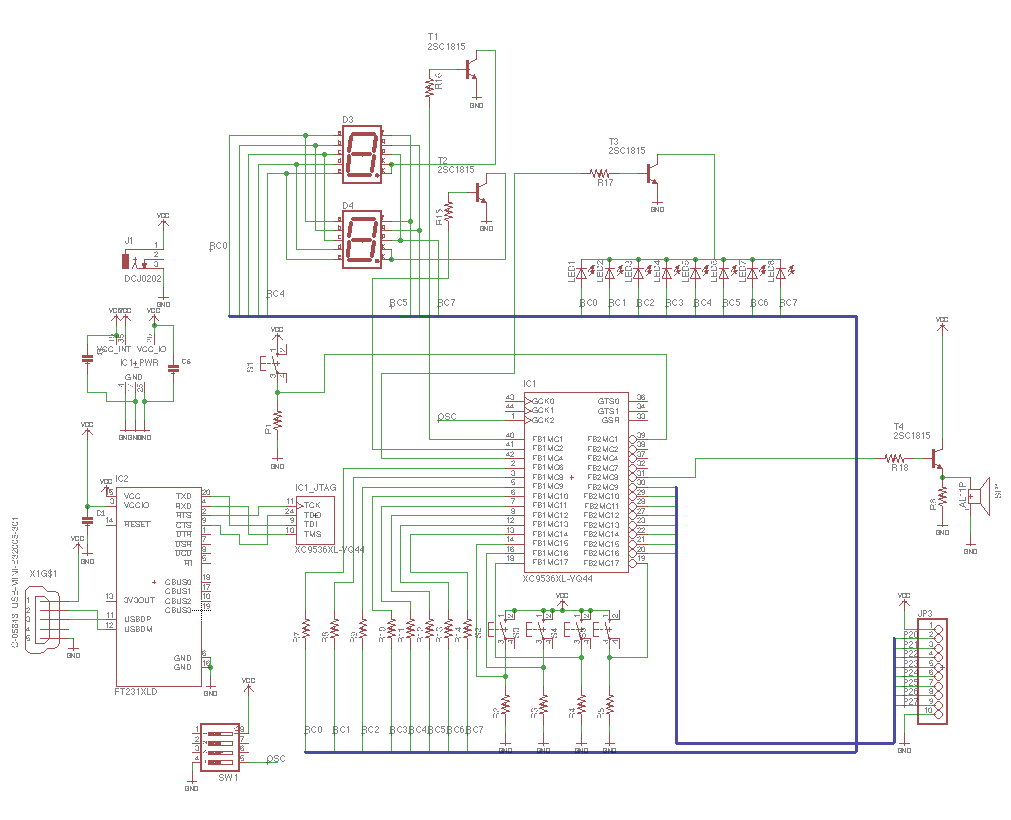

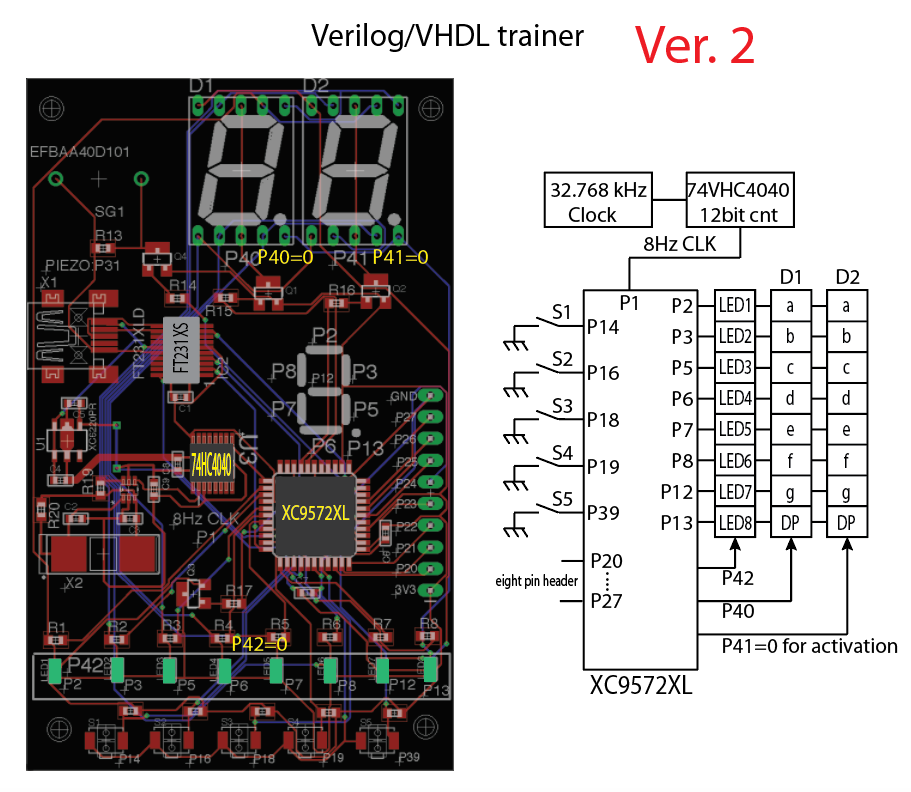

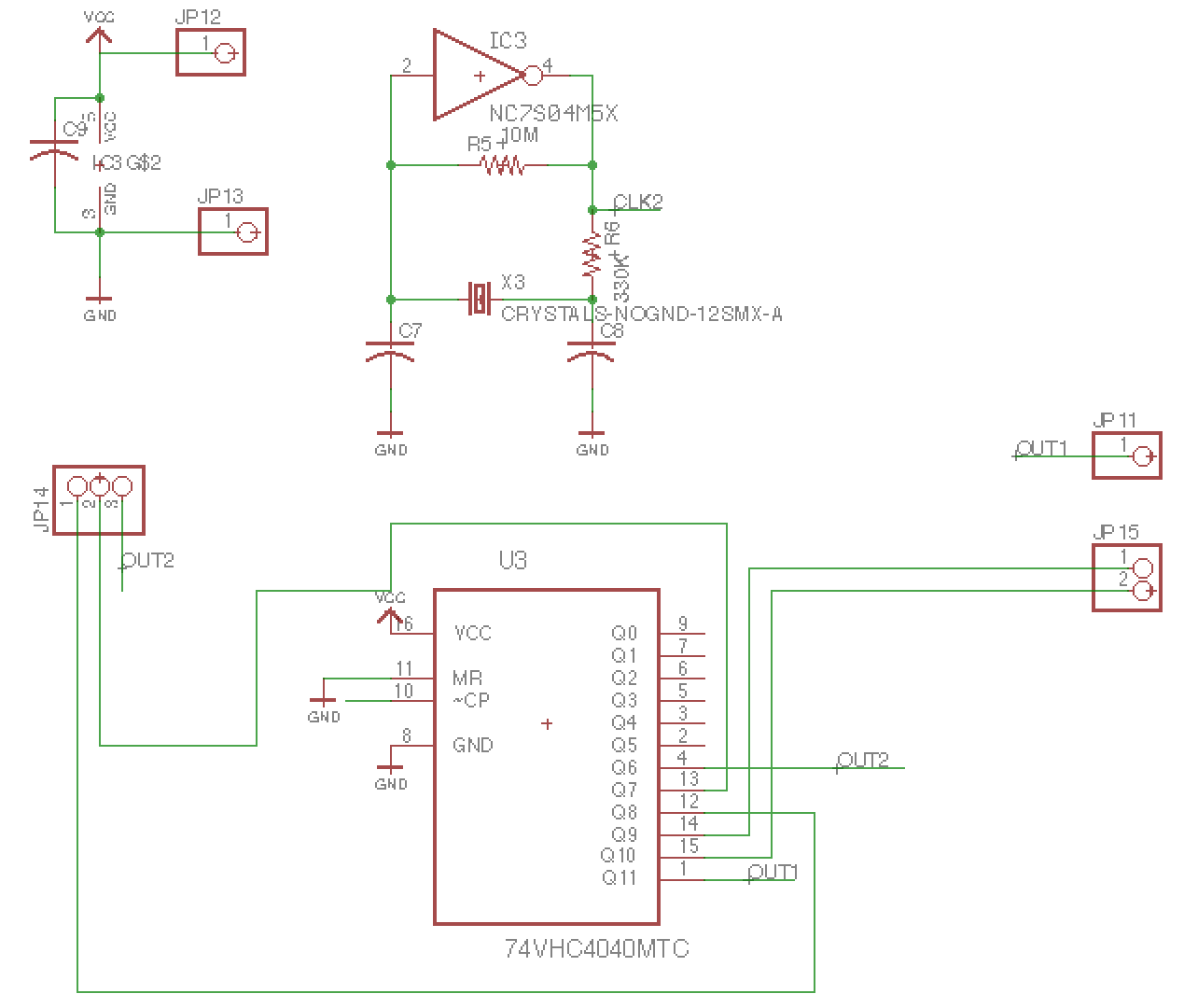

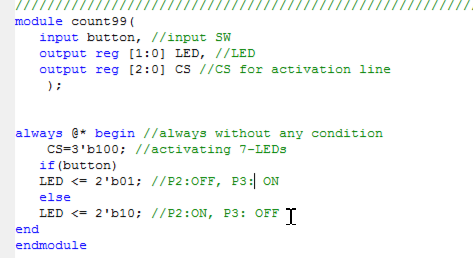

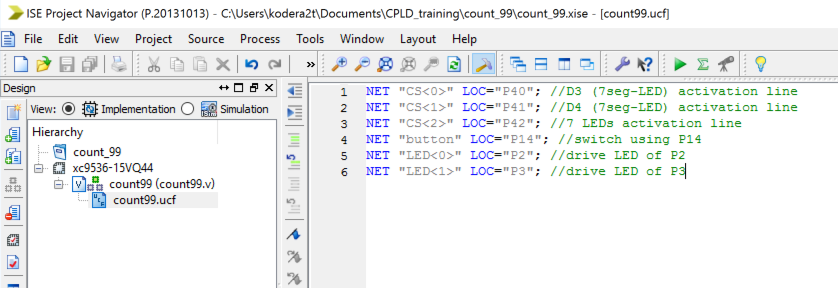

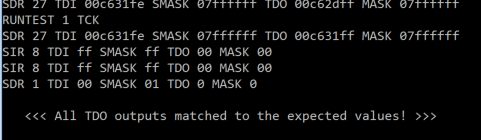

Two 7-seg LEDs and 8-LEDs has a "bus-connection", and another single bit requires for the activation for each components. On-board OSC is connected to P1 and we can learn counter description and some timing device implementation. This is really optional but I also put one piezo element as a sounder through impedance converter.

The board in the picture is still prototype and I may sell this board at my tindie store later.....

kodera2t

kodera2t

ziggurat29

ziggurat29

mit41301

mit41301

Dave Vandenbout

Dave Vandenbout