April 25, 2025...

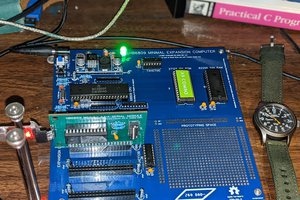

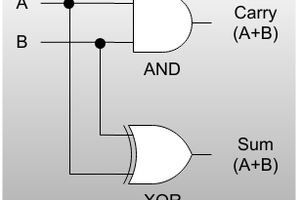

I updated the PCBs to include all my patches and posted them to the github page. There are two categories for the PCBs: One category is 'generated' where the partially-routed PCBs are generated from the Verilog-like module files then the routing is completed manually. There are no schematics as such for the generated PCB files, see the https://www.outerworldapps.com/pdp8v/designdetails.html page for details. These are the main processor circuit boards, ACL (accumulator/link), ALU (arithmetic logic unit), MA (memory address register), PC (program counter), RPI (raspberry pi/leds), SEQ (sequencer).

The other category is 'manual' that have manually entered schematics via Kicad, ie, all the other boards. The important ones are BACKPLANE and EIGHT (8-tube boards).

Recently (Apr 7, 2024)...

Have been getting maindec stuff going again, by updating the github repo (no hardware changes).

Also did a little with the TC08 dectape emulator, though it doesn't boot OS/8. Reading on the web about TC08 and dectape, sounds like the drivers do a lot of cycle dependent stuff. For example, the OS/8 boot block switches the field number in the middle of the transfer. So I'm not going to put much more effort in it, sounds like too much of a tar-baby for me. The RK8JE emulator works with OS/8 so that's good enough.

Source code breakdown...

- asm - pdp8 assembler (allows long labels) and linker

- cc,ctrl - left-overs from hode, no pdp-8 stuff

- de0 - out-of-date DE0 FPGA implementation

- driver - autoboardtest, raspictl programs that run on PC,RasPI to control the tubes

- filesys - an aborted attempt to write a PDP-8 file system

- focal - focal-69

- freqcounter - arduino-based front panel frequency counter (pcb in kicads/freqctr)

- iowarrior - makefile that downloads and builds IO warrior library - not used

- kicads - various PCBs

- maindec - scripts to run maindec programs on simulator and on tubes

- modules - processor source code

- netgen - takes modules files and generates PCBs, real Verilog, C++ simulator, TCL simulator

- scheme - a scheme interpreter

- silly - silly programs

- zynq - up-to-date Zynq/ZTurn FPGA implementation

About the tubes...

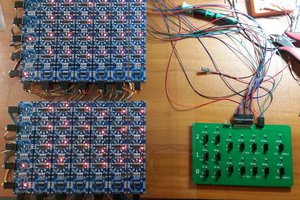

So back in June or July 2022 I didn't know what tubes to use, I was thinking 12AX7 but they are $10..$20 apiece. I went to MIT flea market and saw someone with a couple tables of tubes, and looked at what he had. I noticed a carton of 5 6J6s and wondered what they were. So I looked on my phone and saw that they were dual triode, common cathode. I thought I could use them. So I gave him the $10 he wanted. I put one on perfboard and did measurements and it seemed to work pretty much as the datasheet said. Then I had some small circuit boards made that would have one tube and places for the resistors, diodes, capacitors and connectors to make a pair of and-or-invert gates. When they arrived, I hooked it all up and tried it out, seemed to work ok as gates. Then I took three of the tubes (6 gates) and made a D-FF and that seemed to work. IIRC, clocked around 100kHz (ahem kcps).

Meanwhile I wondered how common are the 6J6s? Looking on the Internet and eventually ebay of course, I found someone selling cartons of 200 6J6s for $150. This is too much of a co-incidence and probably one of those ebay too-good-to-be-true deals. But it was worth the risk of $150. And amazingly, a box arrived and had some label for some DoD installation in Utah, dated October 1985. Opened it up and little plain-white cartons of 5 tubes, each box stamped 6J6A. So I tried them in my D-FF setup and they worked! Then I thought hope there are still more of those cartons available. Fortunately, yes, so I bought two more cartons, thinking one would be enough (giving me 400 tubes), but good to have an extra carton so I have plenty of spares for an extra $150. Unfortunately...

Read more »

Dave Collins

Dave Collins

ziggurat29

ziggurat29

Dave's Dev Lab

Dave's Dev Lab

Al Williams

Al Williams

What a project ! Fantastic !