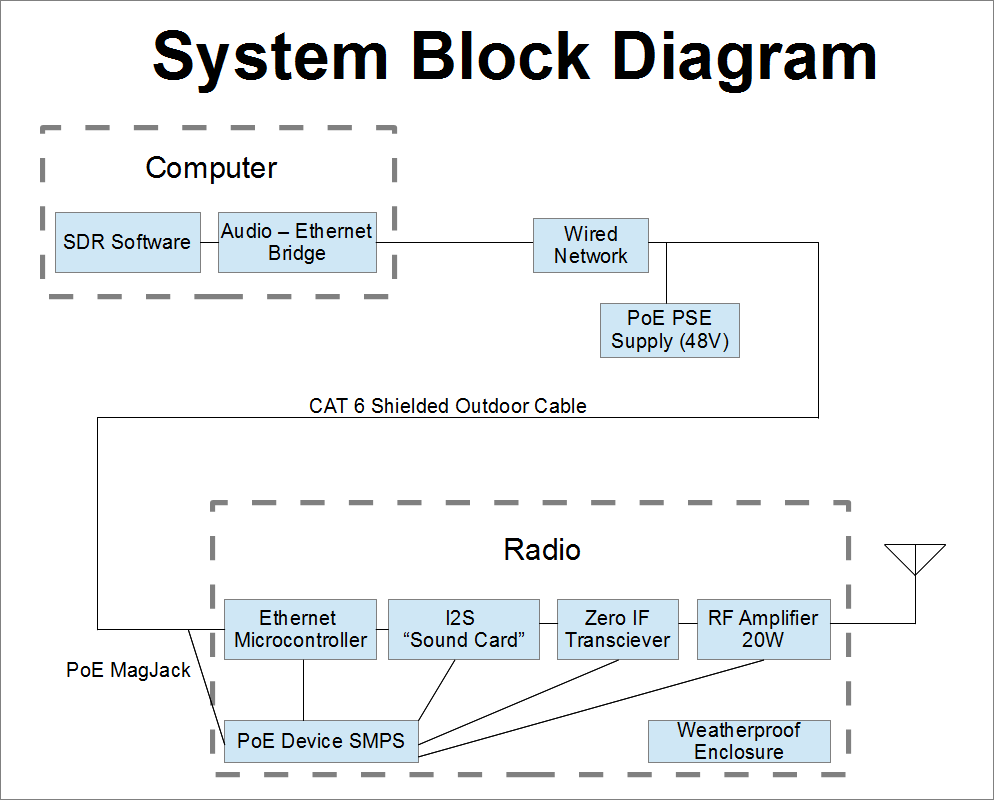

Basically, this is a "headless" radio designed to be computer controlled. We get a lot of value out of an Ethernet cable, as it carries the baseband signal, power, and control. Below is the system block diagram:

Stop wasting time and money on expensive coaxial cable and put the whole radio right at the antenna feedpoint!

I've been trying hard to get CS4270 to work but without any luck. Can you share any further information?