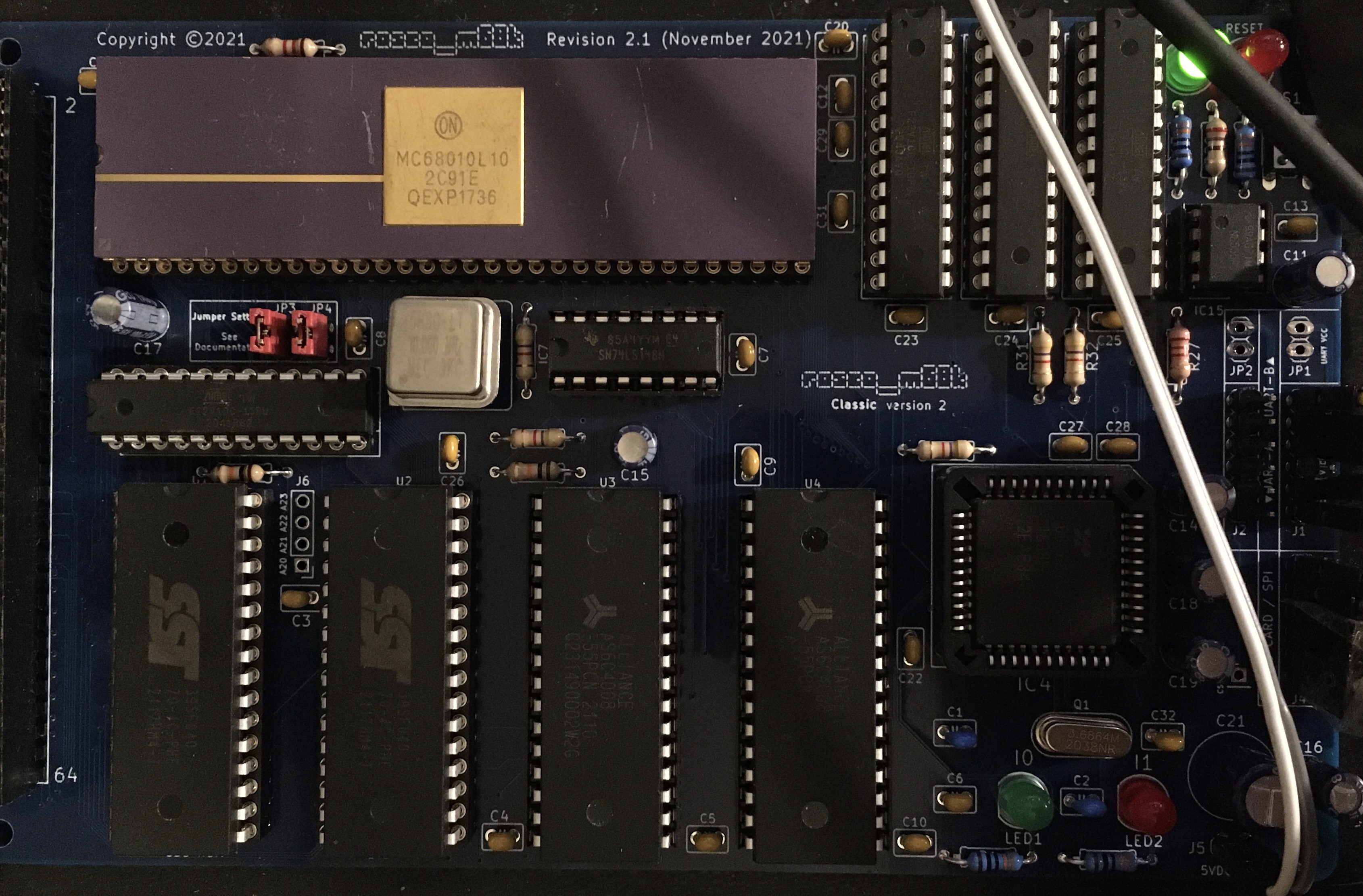

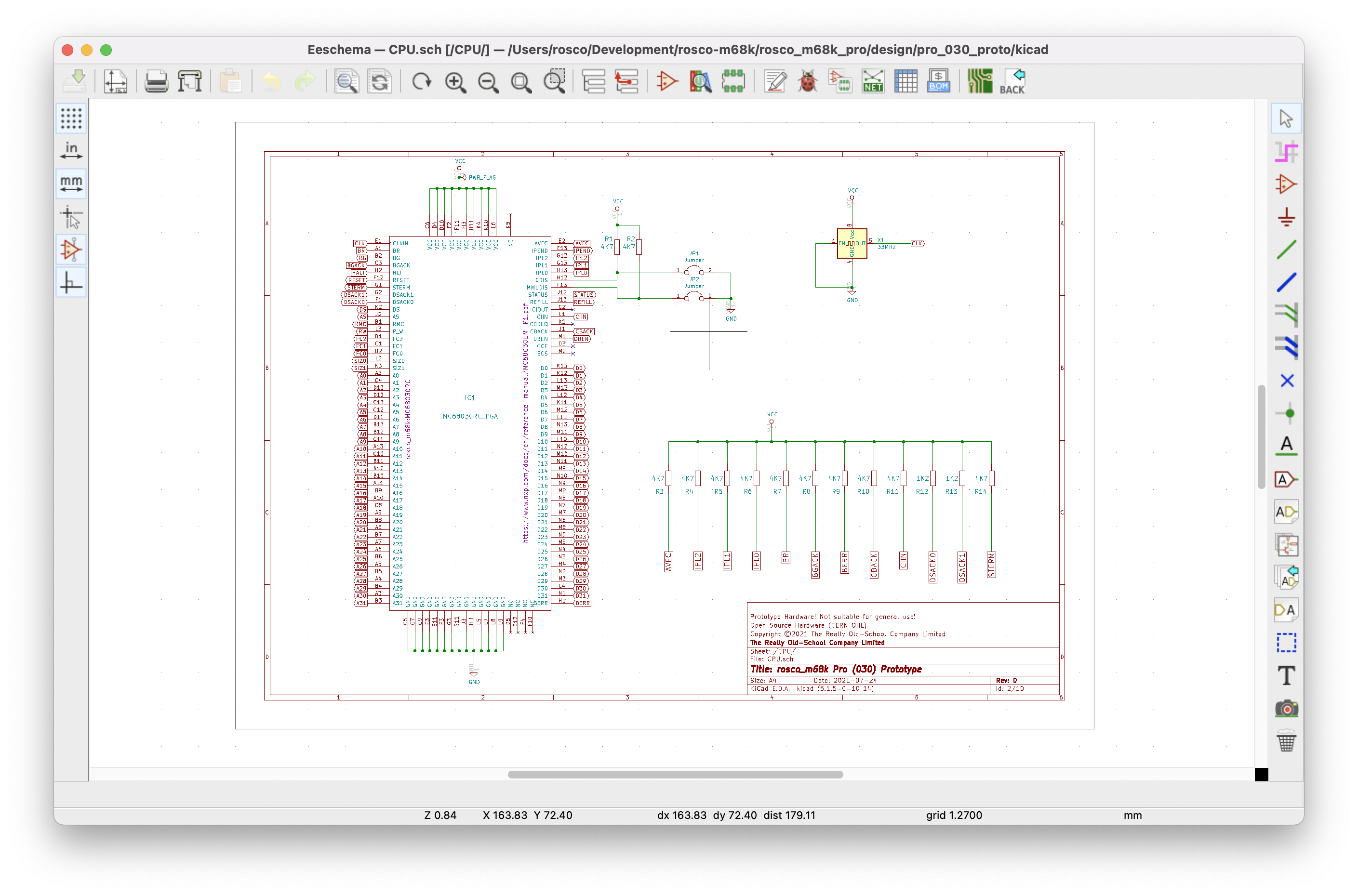

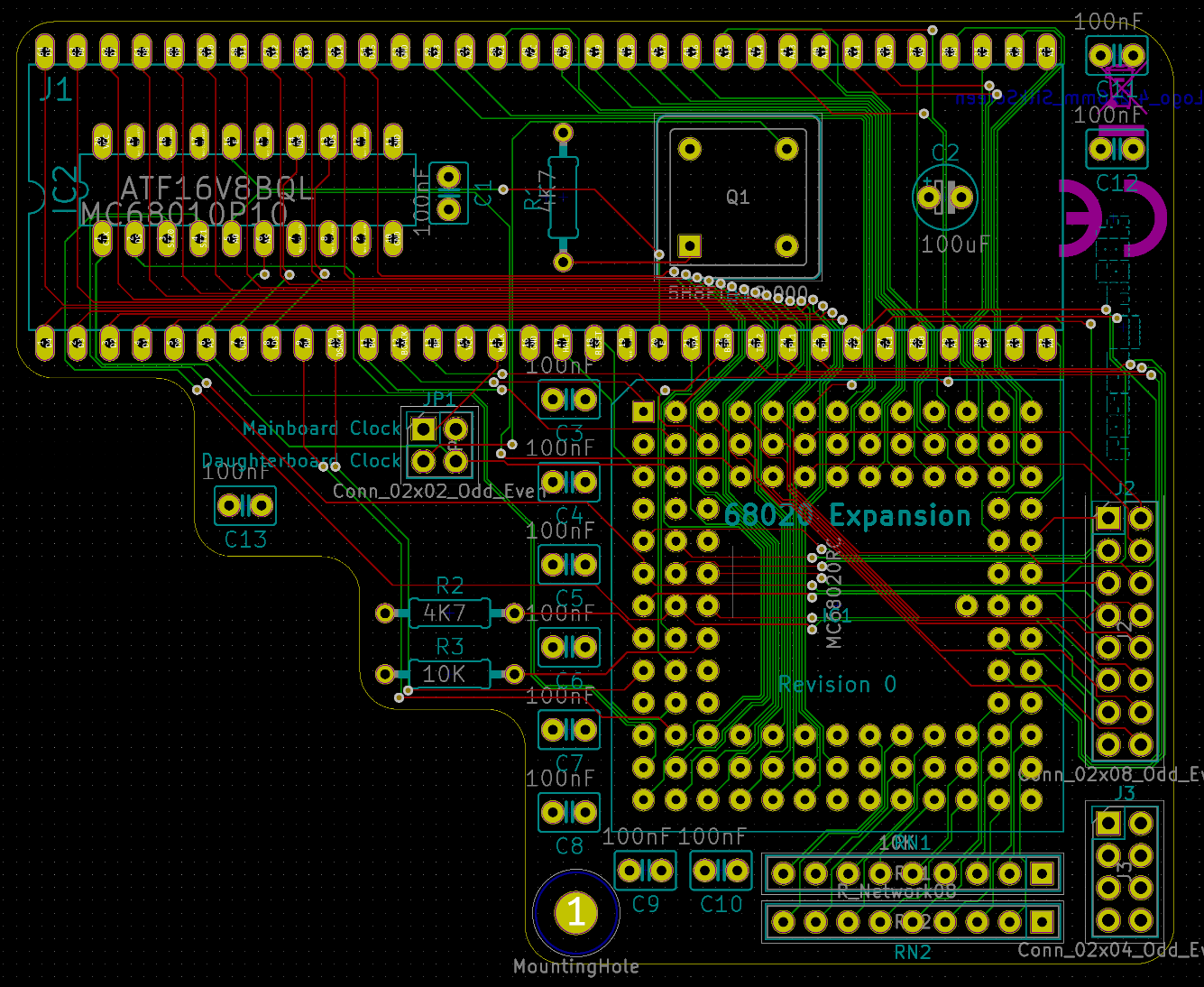

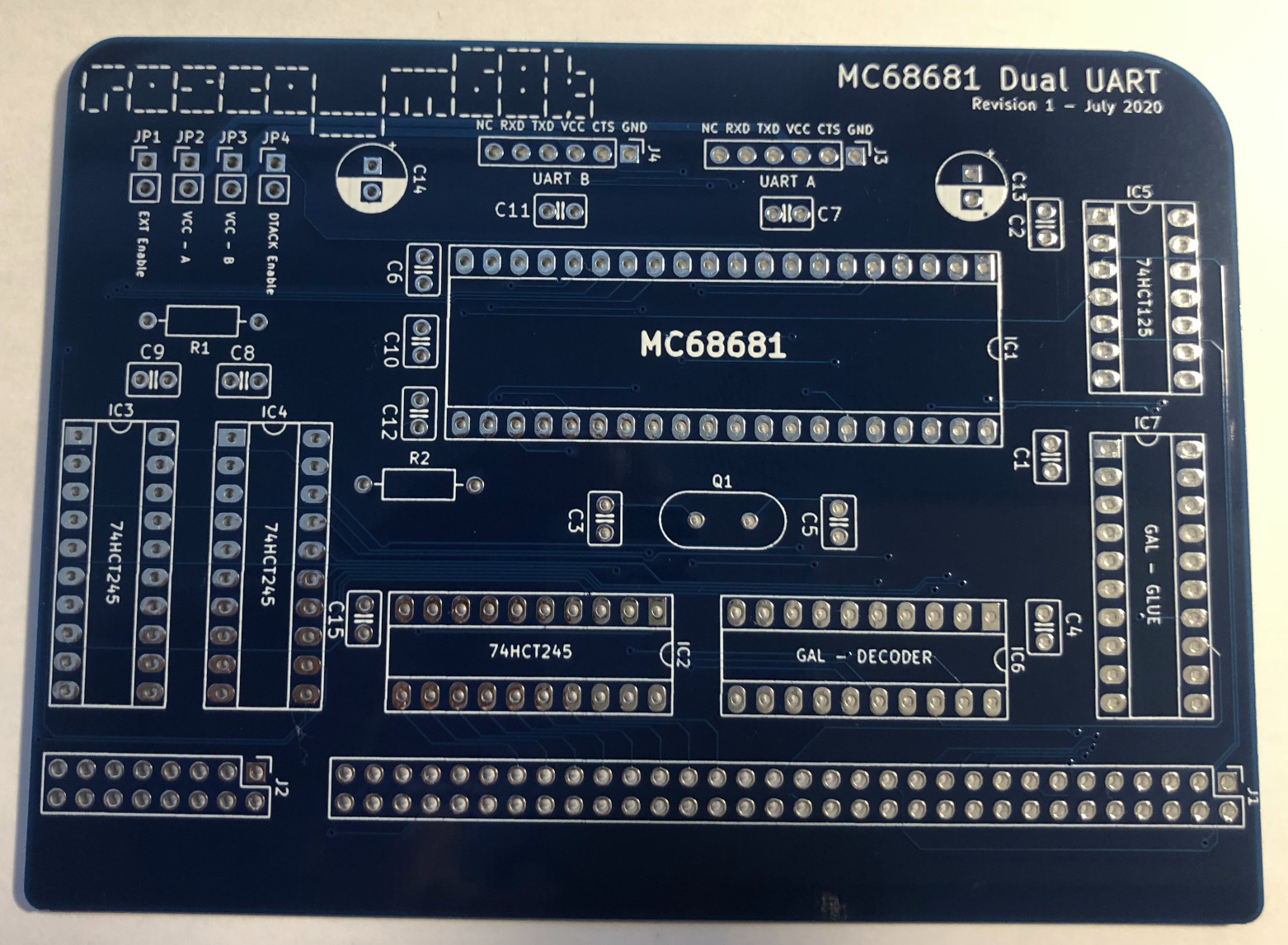

This project is a general-purpose Motorola 68k computer designed and built from scratch using mostly period-appropriate parts. It started out as a breadboard project, and has now progressed through a revision zero prototype, to a much-improved revision 1 board design that is available to buy as either the bare board or a self-assembly kit.

The system is based on a 68010 running at 8MHz with 16KB ROM and 1MB RAM, and with a mix of PLD and TTL glue logic. It has an on-board UART and includes a serial boot loader that can load code over the serial port (using the widely-supported Kermit protocol). A simple proof-of-concept "kernel" also exists that can be loaded via the boot-loader, and gives a good starting point for developing code to run on the computer (i.e. it provides ready made link scripts and so on).

In terms of hardware hacking, the board provides a few GPIO pins with interrupt capability, as well as two software-controlled timers that can handle delay mode, event counting and (primitive) PWM. These are handled on-board by the MC68901 multi-function peripheral. All signals are also broken out on an expansion connector, so it should be quite easy to build expansions for this system to handle pretty much anything you can think of.

The next steps for the project are to design and build a graphics adapter (probably based on the Yamaha V9958) and other expansion cards, and to make these available to others who want their very own modern(ish) M68K computer!

Ross Bamford

Ross Bamford

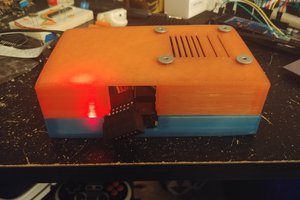

Behind that awesome front-panel, Henk's put together a full case, including expansion slots (based on a version of my baseboard, which he's had to hack due to my lack of foresight or regard for standards - suffice to say I'll know better in future and will be designing with the case in mind!).

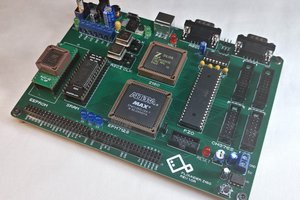

Behind that awesome front-panel, Henk's put together a full case, including expansion slots (based on a version of my baseboard, which he's had to hack due to my lack of foresight or regard for standards - suffice to say I'll know better in future and will be designing with the case in mind!). And here it is with the rosco_m68k in place (at right of the picture), along with the expansion card that interfaces to the front-panel. (at left).

And here it is with the rosco_m68k in place (at right of the picture), along with the expansion card that interfaces to the front-panel. (at left).

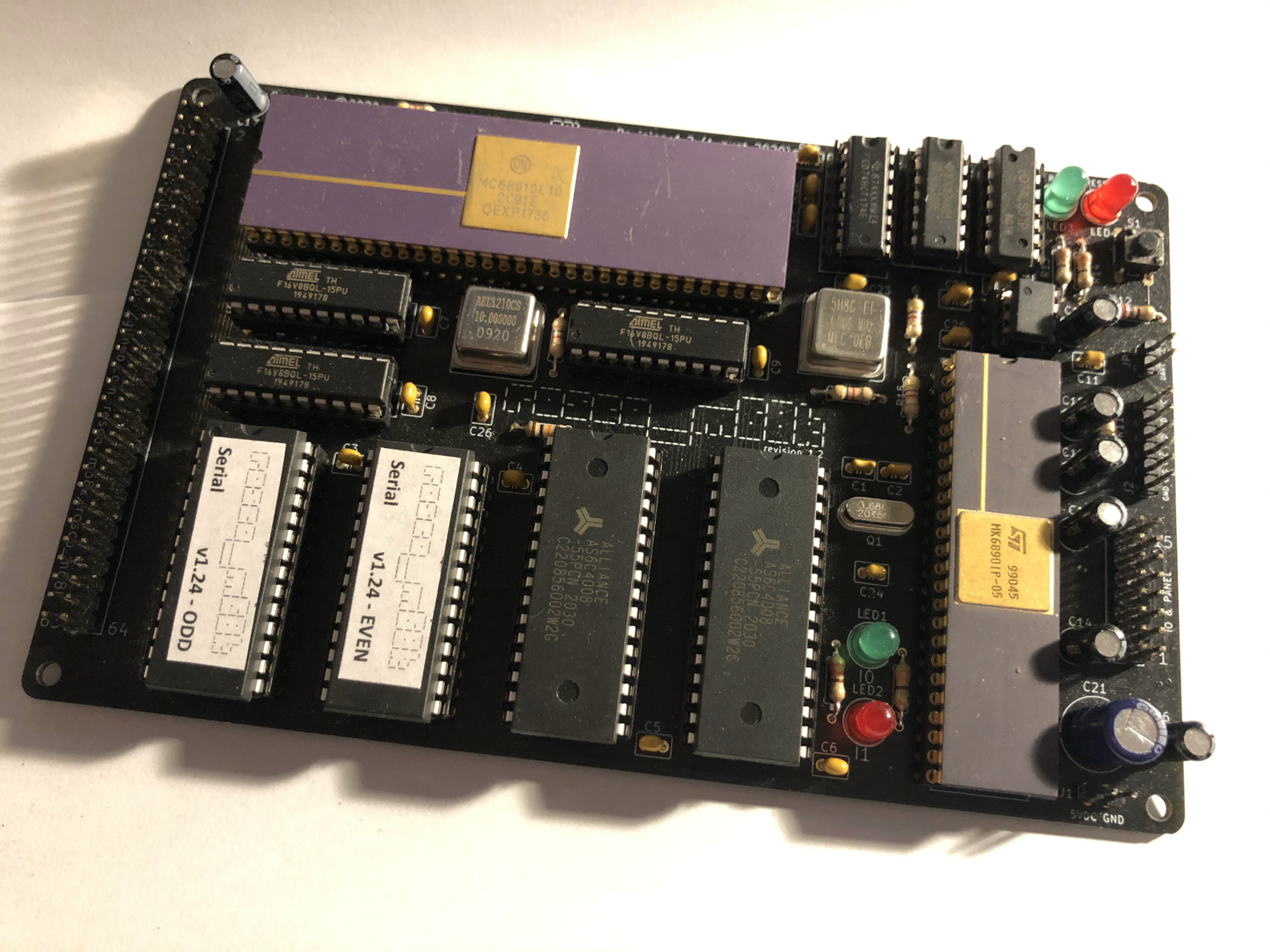

Even with the 16-bit bus (and with a relatively-slow 12MHz 020), this is already showing an impressive turn of speed in benchmarks. The 10MHz 010 dhrystone results were:

Even with the 16-bit bus (and with a relatively-slow 12MHz 020), this is already showing an impressive turn of speed in benchmarks. The 10MHz 010 dhrystone results were:

Colin Maykish

Colin Maykish

FloppidyDingo

FloppidyDingo

john lemme

john lemme

Have you tried to get Linux to run on it? It should be possible now, even with only 1MiB or RAM: https://tiny.wiki.kernel.org/