This project consist of 3 sub-projects

- Enabling Input

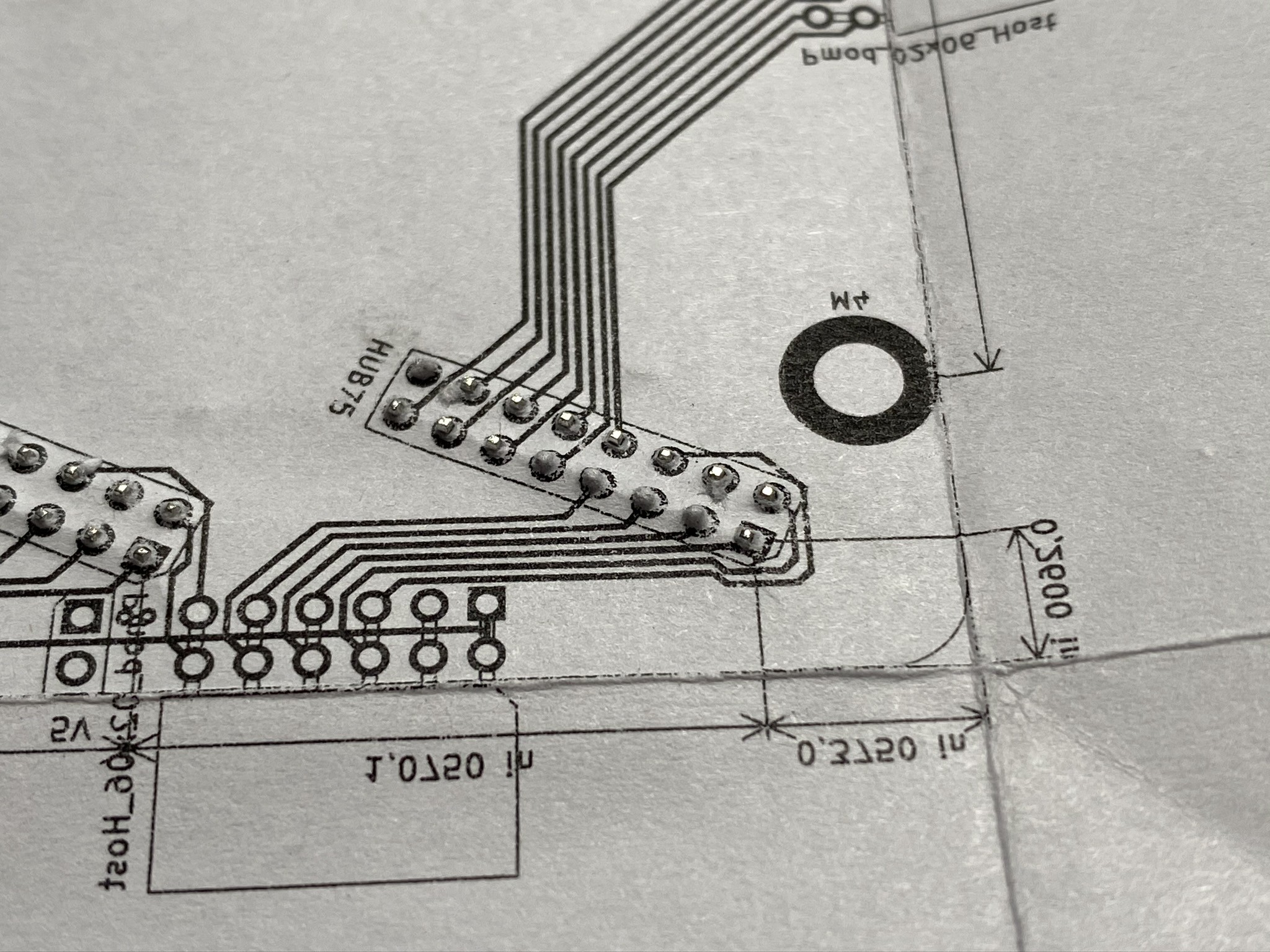

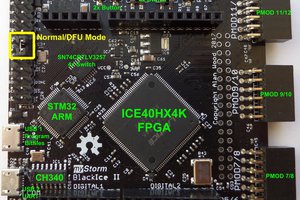

- All the pins of the HUB75 connectors are connected to outputs of

level shifters. They need to be replaces by something that allows bidirectional data communication

- All the pins of the HUB75 connectors are connected to outputs of

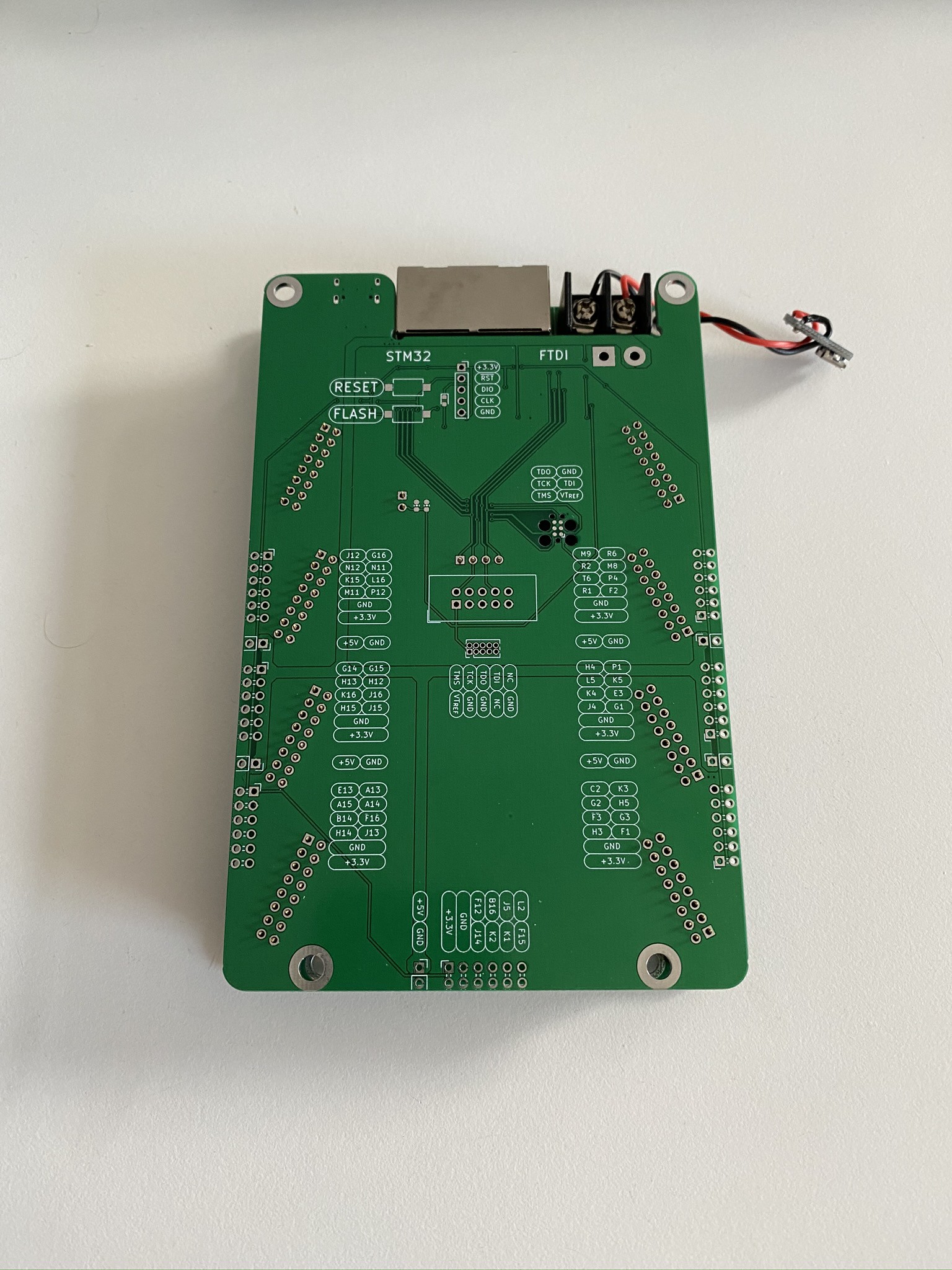

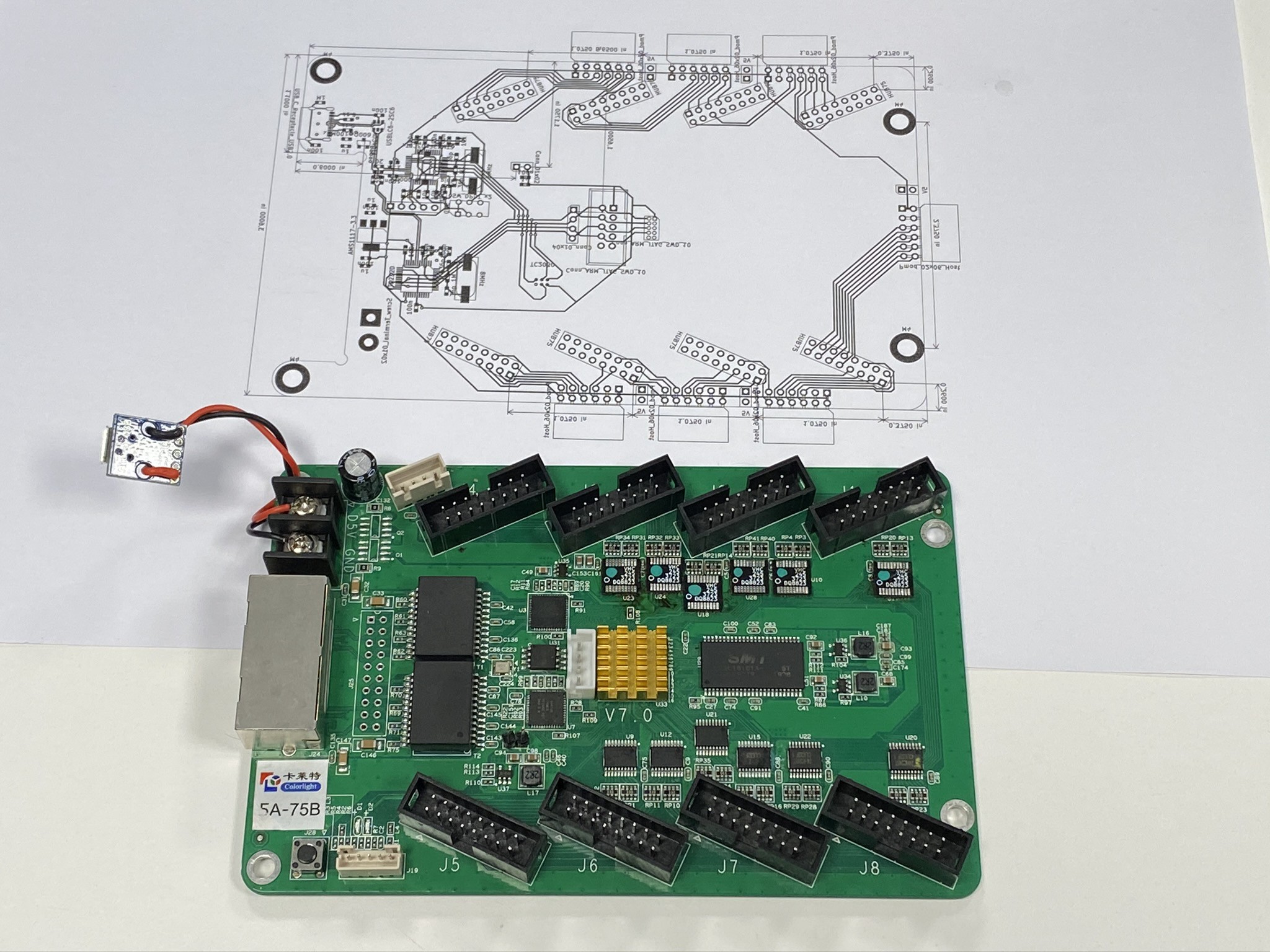

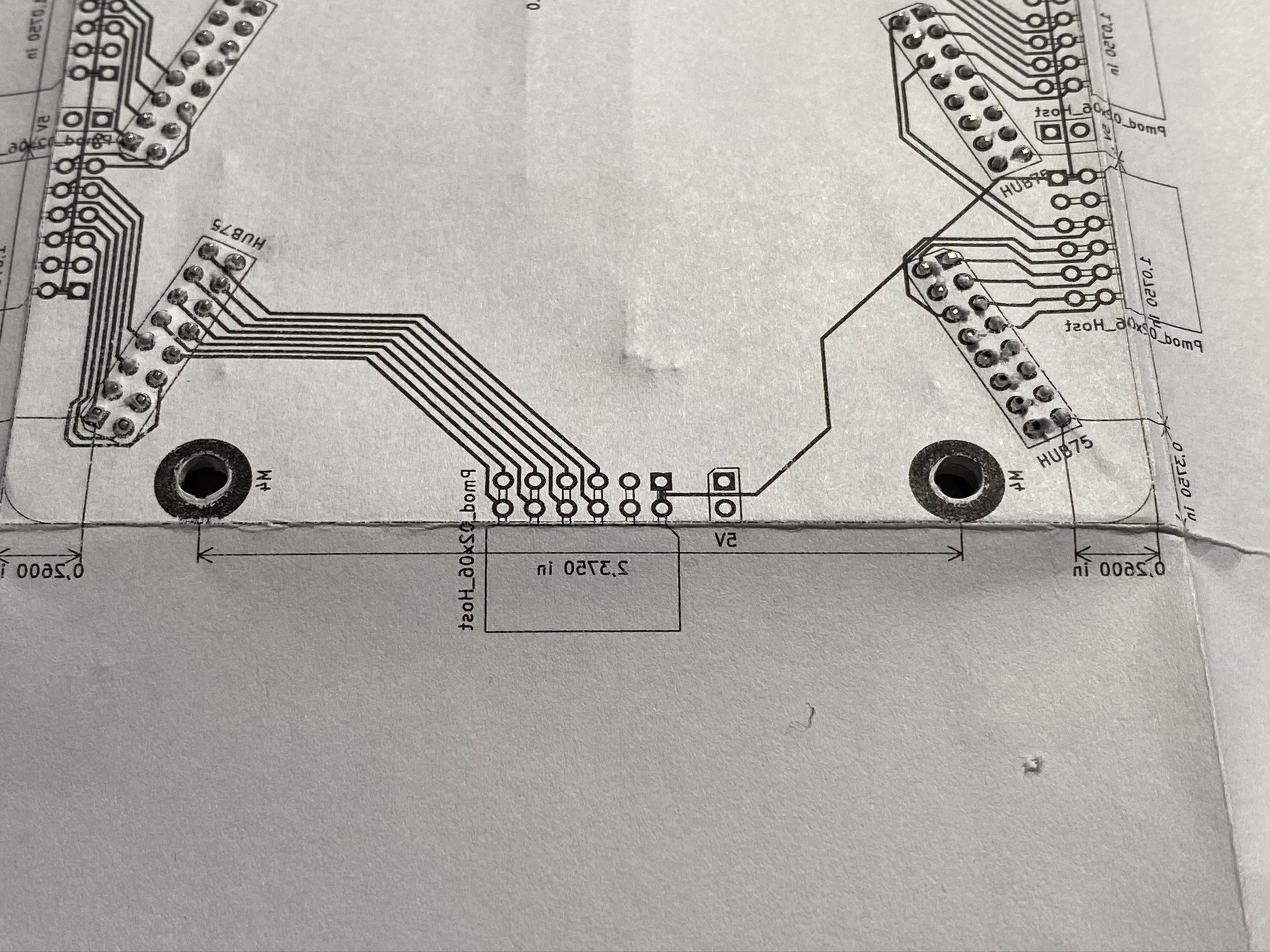

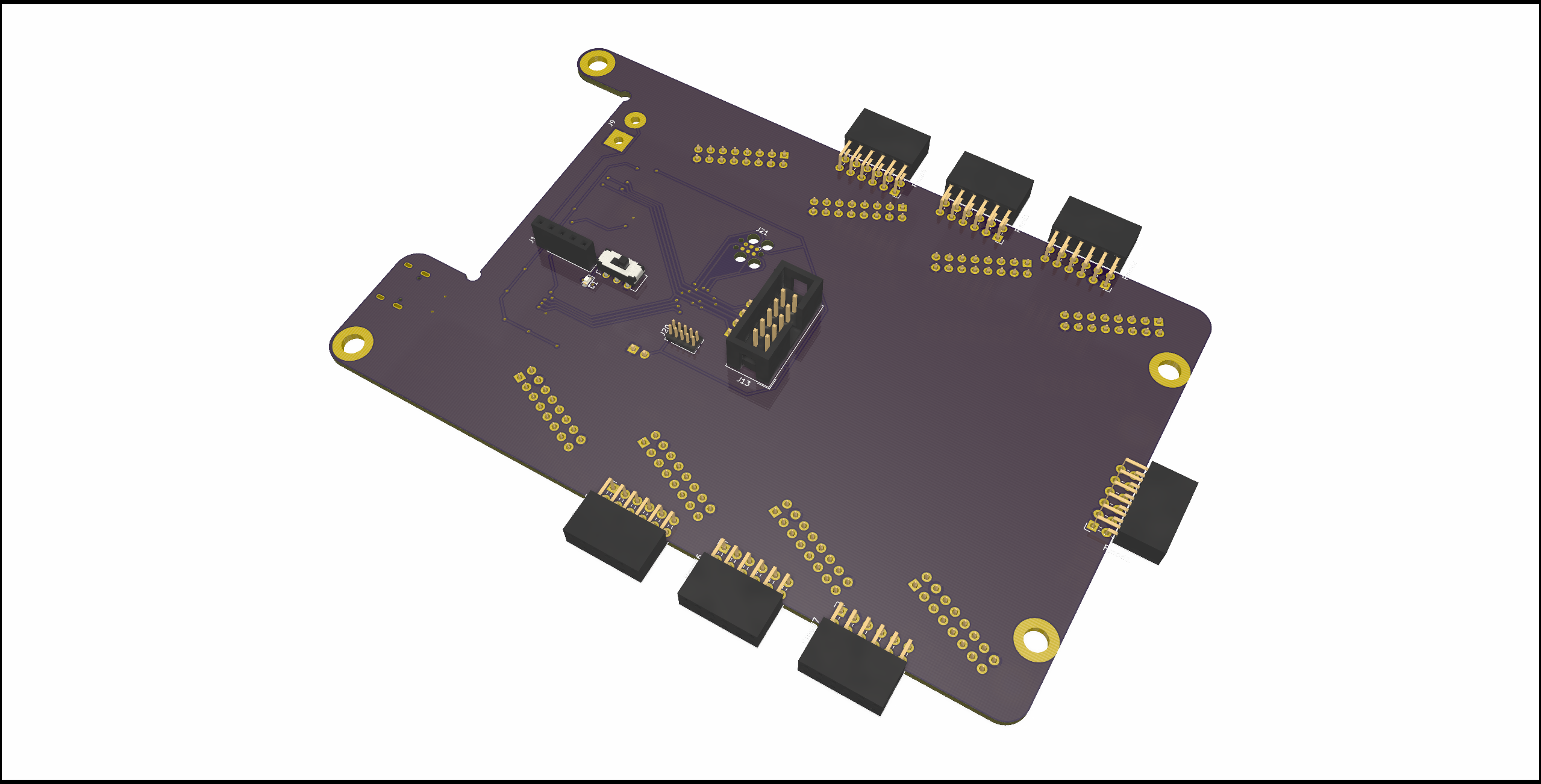

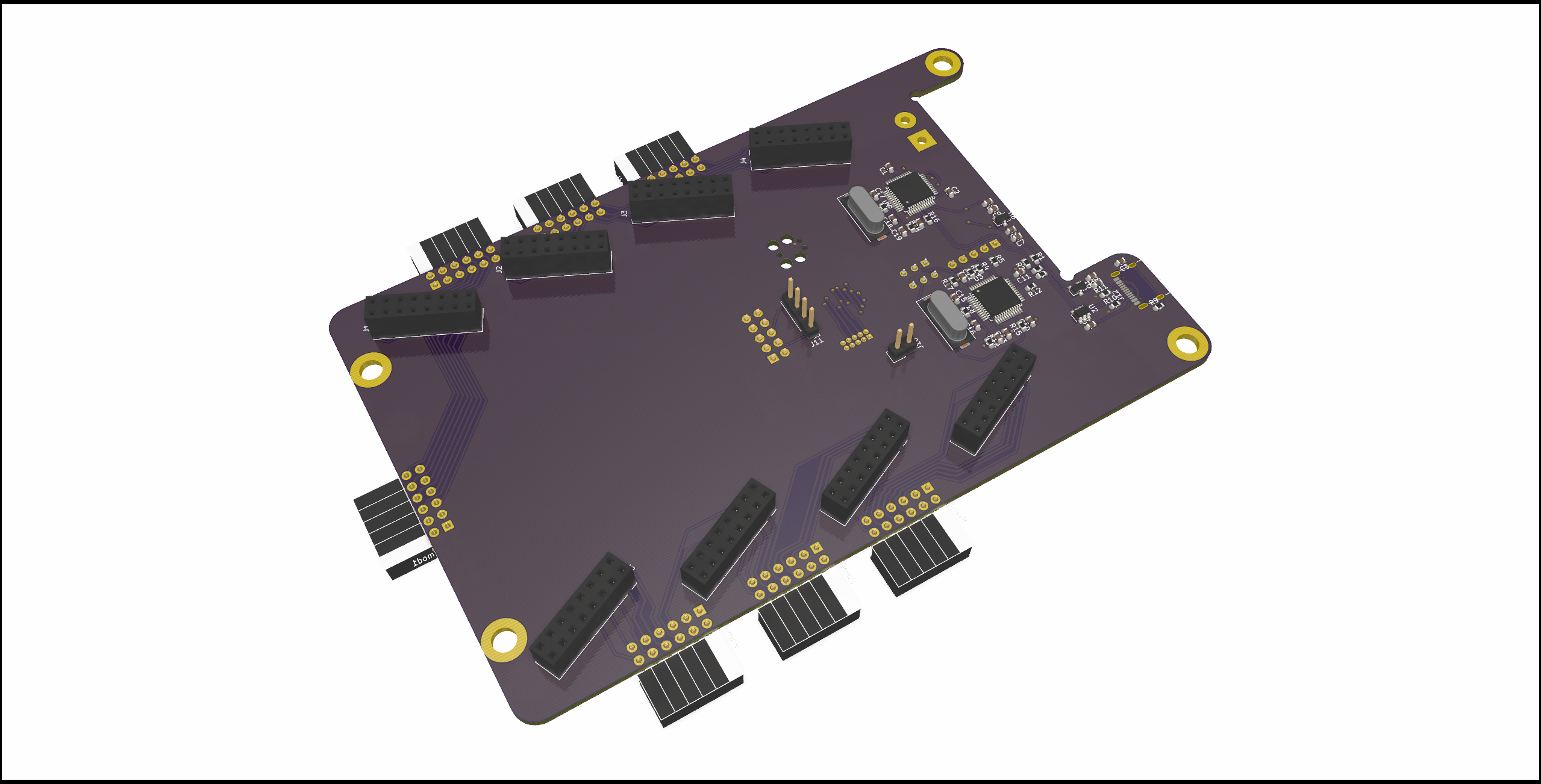

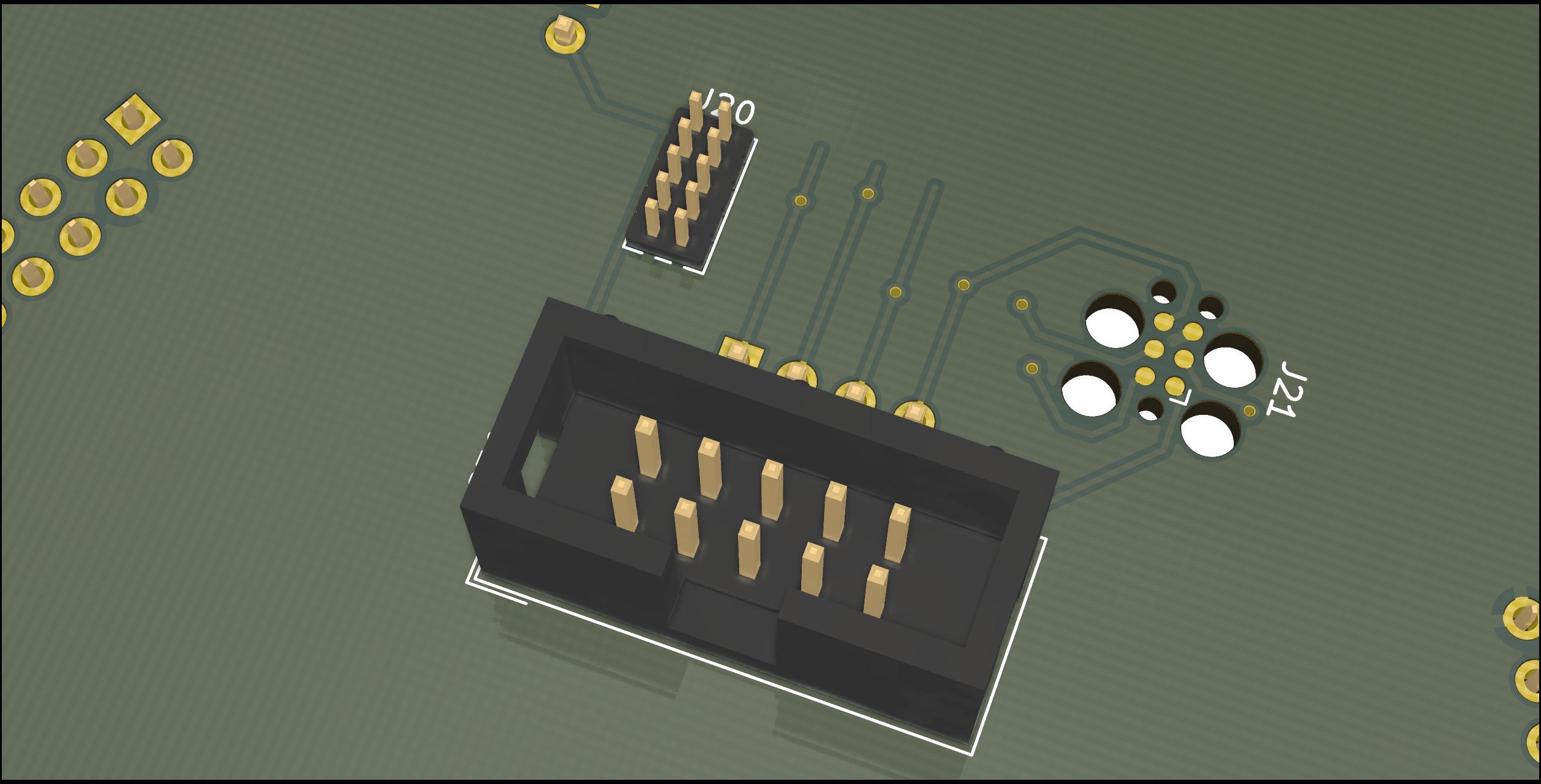

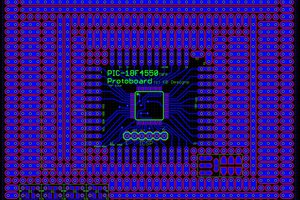

- Designing the PCB

- It shall provide programming via JTAG, as well as serve as a breakout board for all the signal.

- Porting Code

- LiteX already provides a platform definition written in Migen. I would like to port it to nMigen.

marble

marble

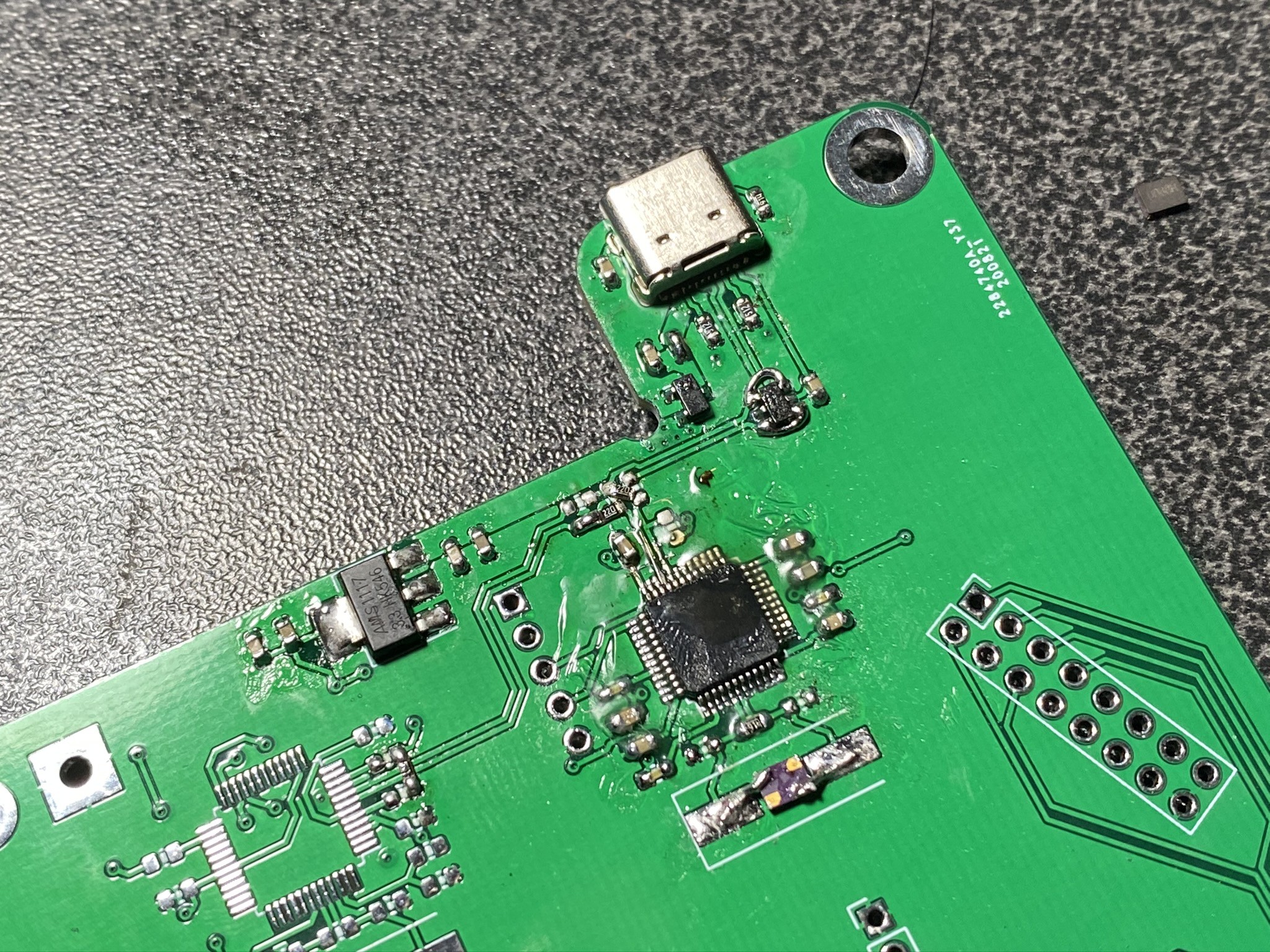

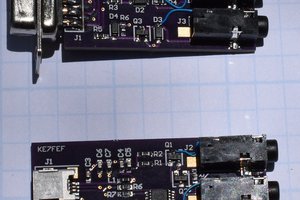

After finding and fixing the mistakes over the weekend I successfully flashed the versaloon firmware onto the STM32.

After finding and fixing the mistakes over the weekend I successfully flashed the versaloon firmware onto the STM32.

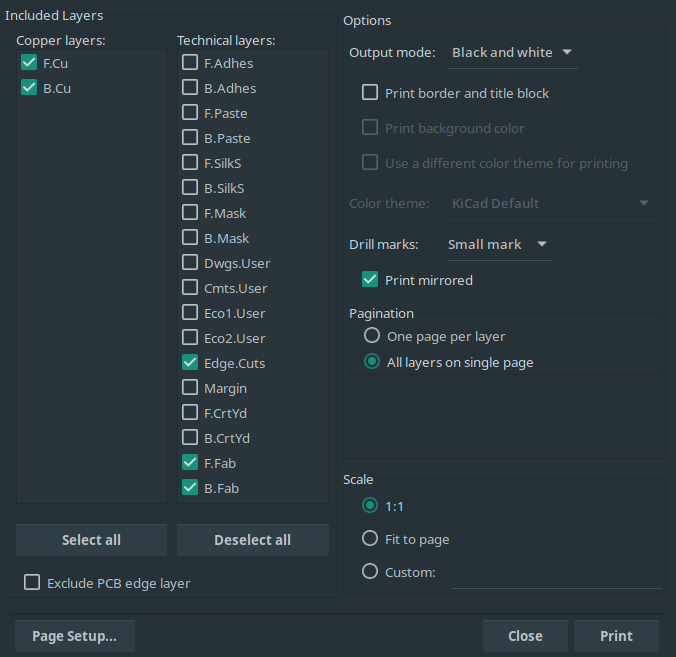

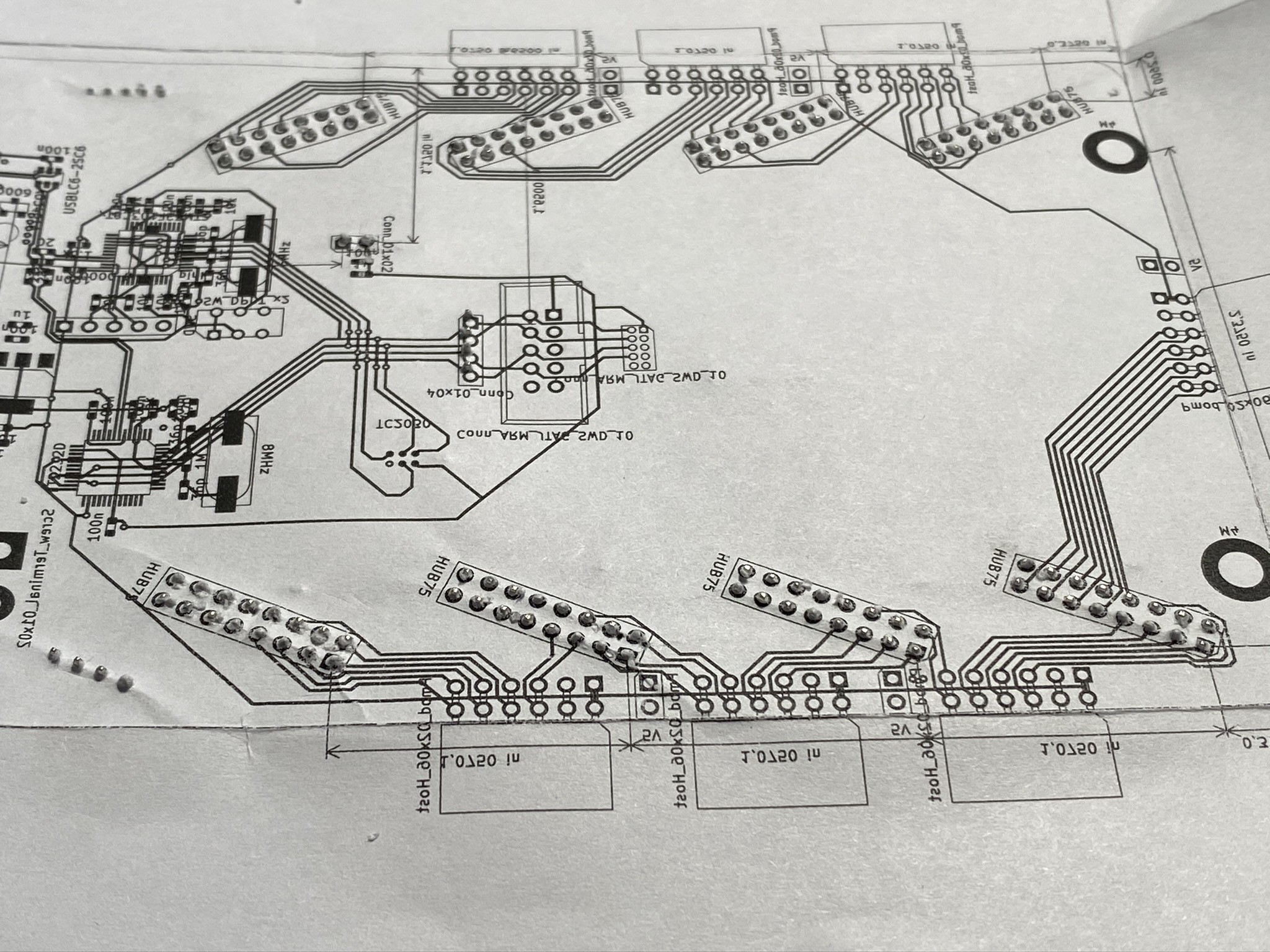

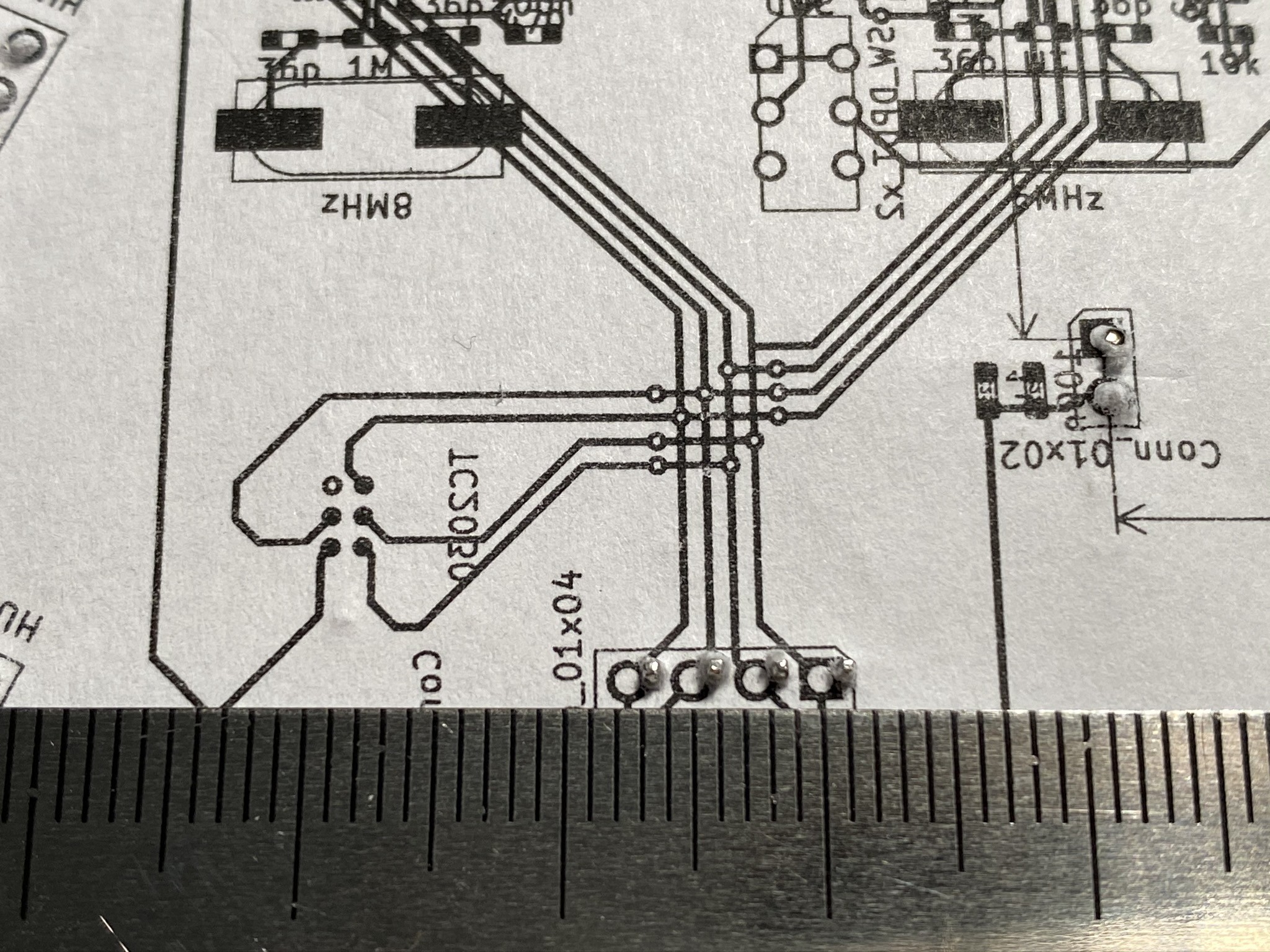

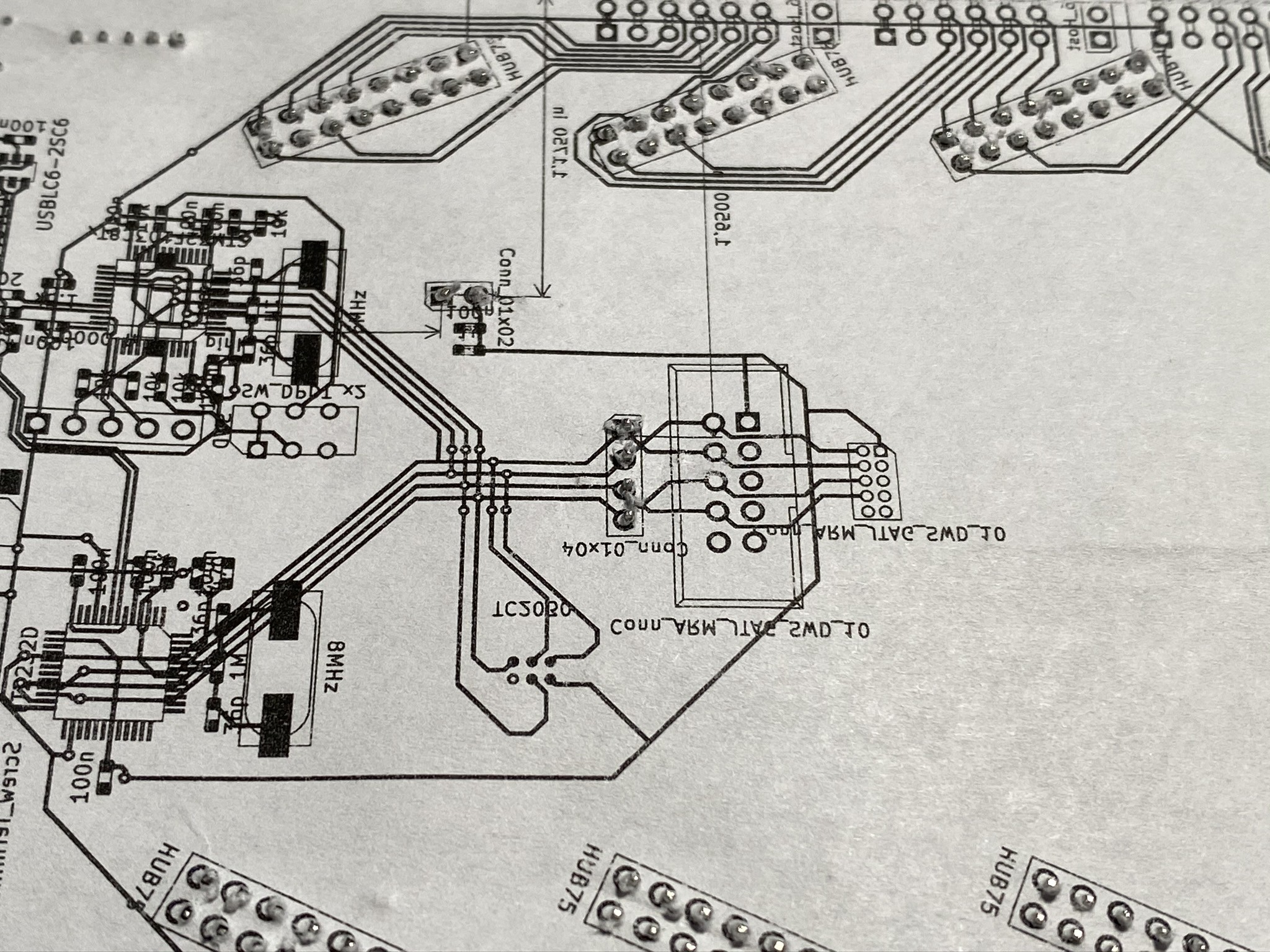

I also sorted the schematic. It's very straight forward.

I also sorted the schematic. It's very straight forward.

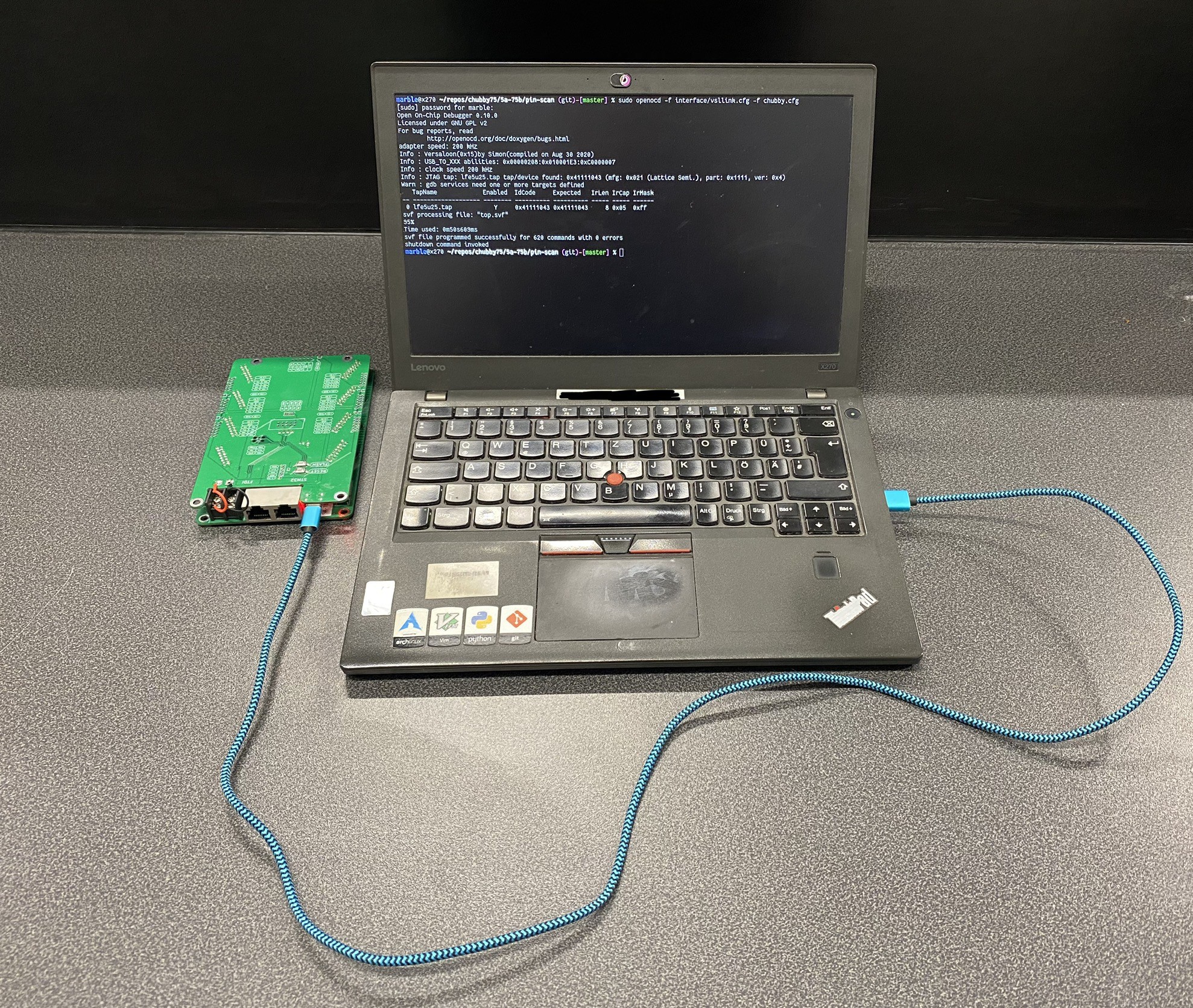

I tested the setup with the

I tested the setup with the

Bharbour

Bharbour

deʃhipu

deʃhipu

Kent

Kent