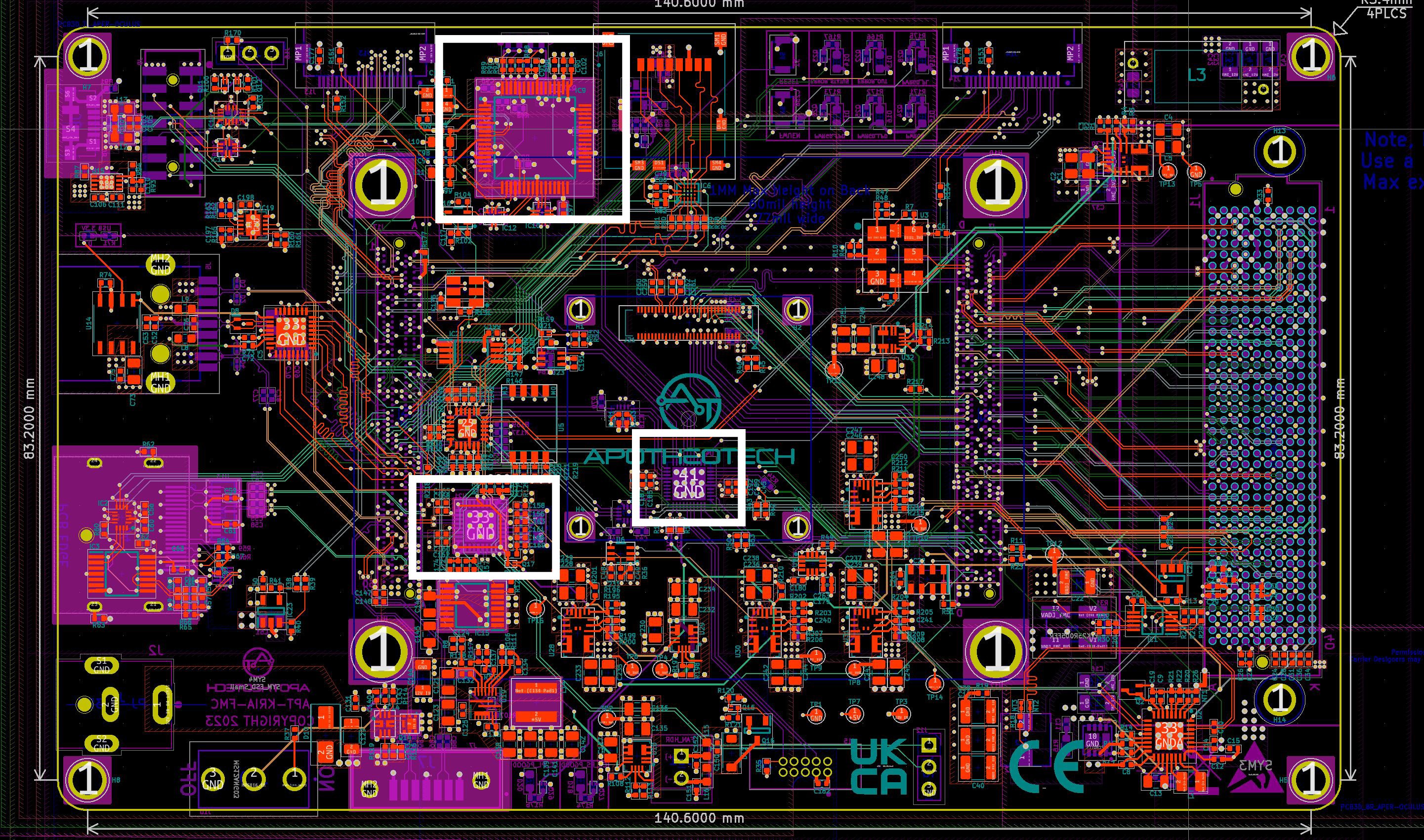

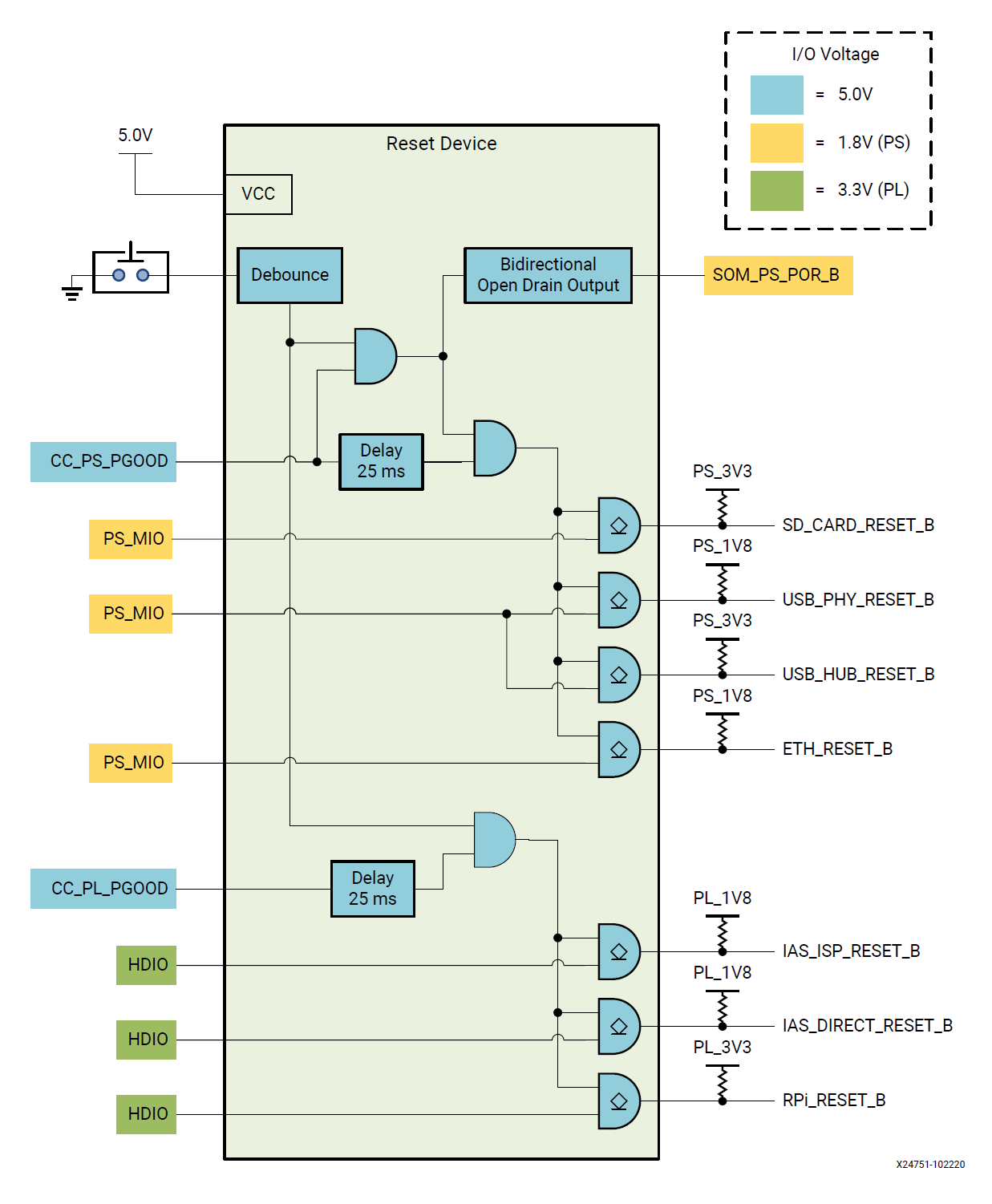

The Aper-Oculus is an open source hardware project supporting the Xilinx Kria SOM architecture. It most notably provides an FMC connector for up to 4 GTH TX, and 2 RX lanes at 12.5Gbps. This enables it to handle multiple prototyping applications with the Kria SOM.

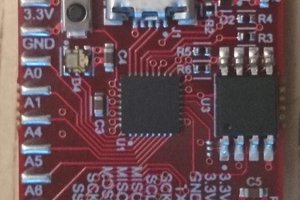

All aspects of the project except for some IP cores (which will be provided encrypted) will be open source. The board can be programmed via the FTDI controller. SI5332 clocks can be programmed via J12 header. To program the PIC18LF47K42 with your own designs, please use the Microchip adapter and program board as described in the github. A naive implementation is currently in progress, which will be VITA 57.1 compatible by launch date of the crowd supply campaign.

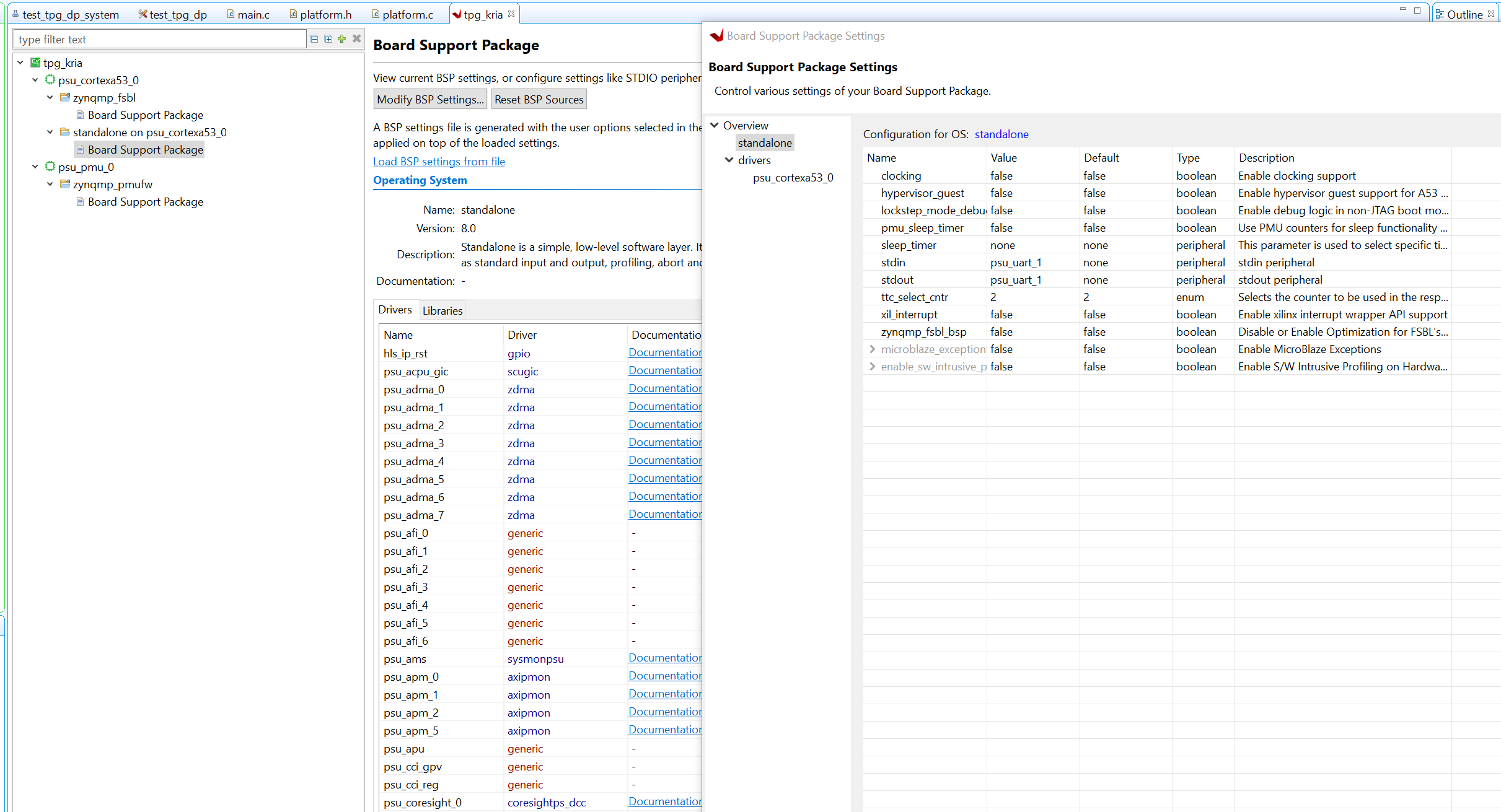

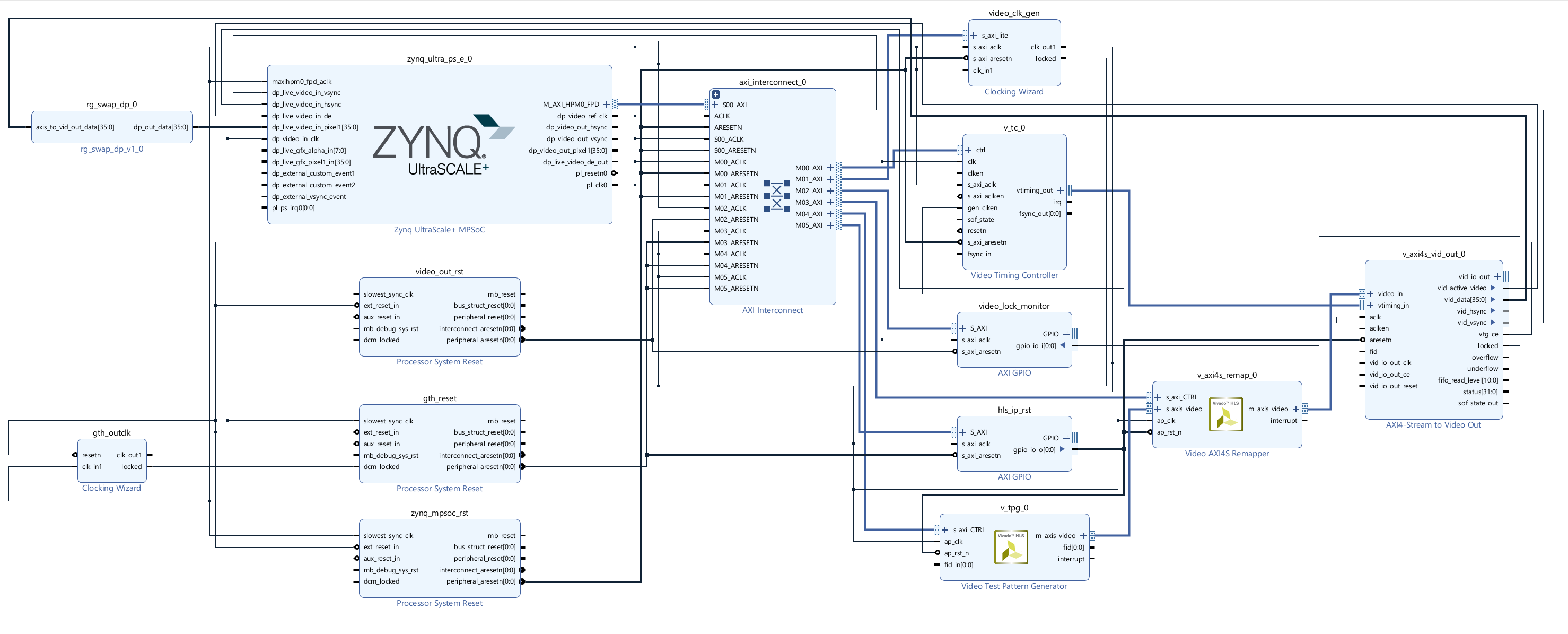

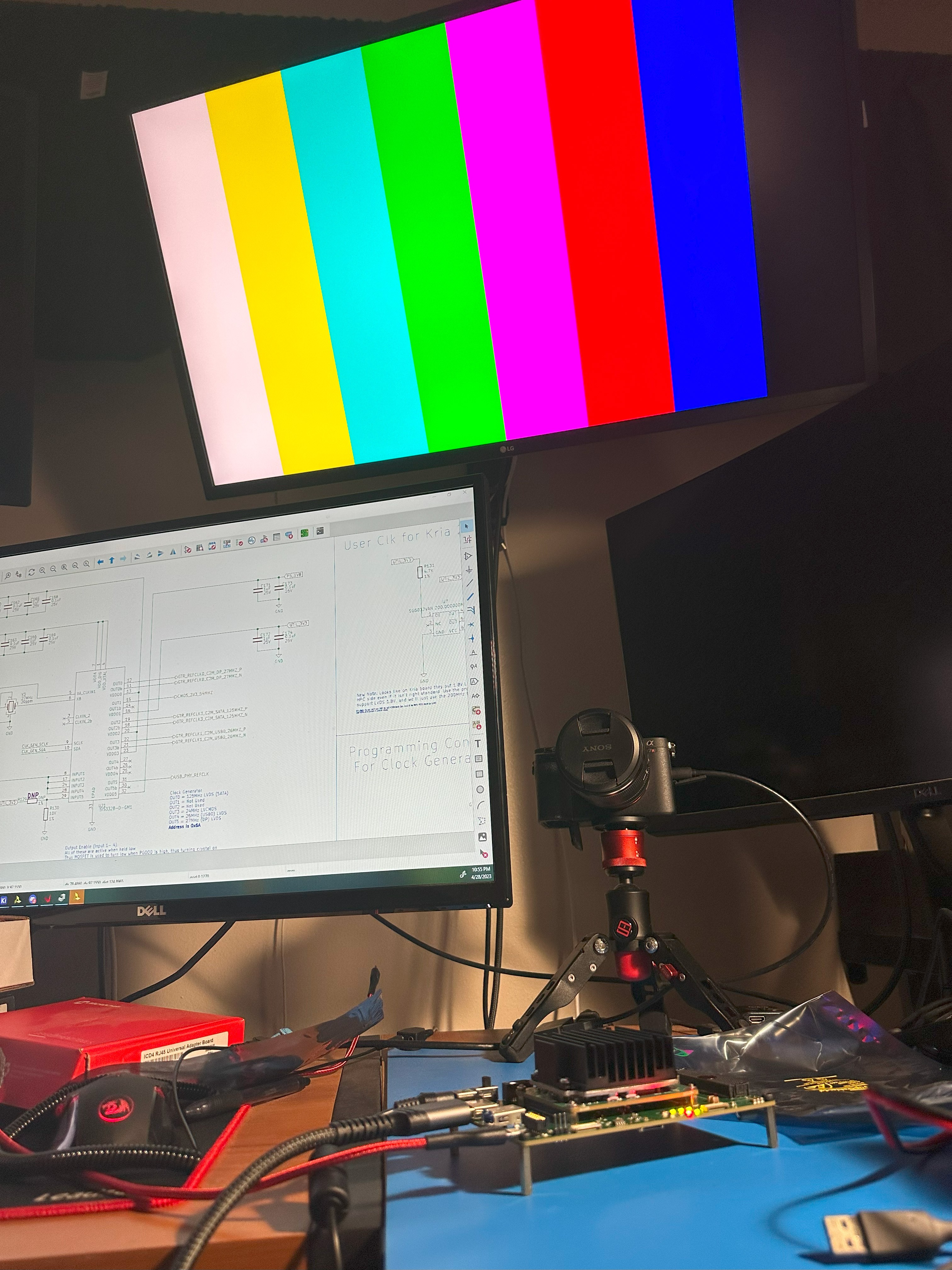

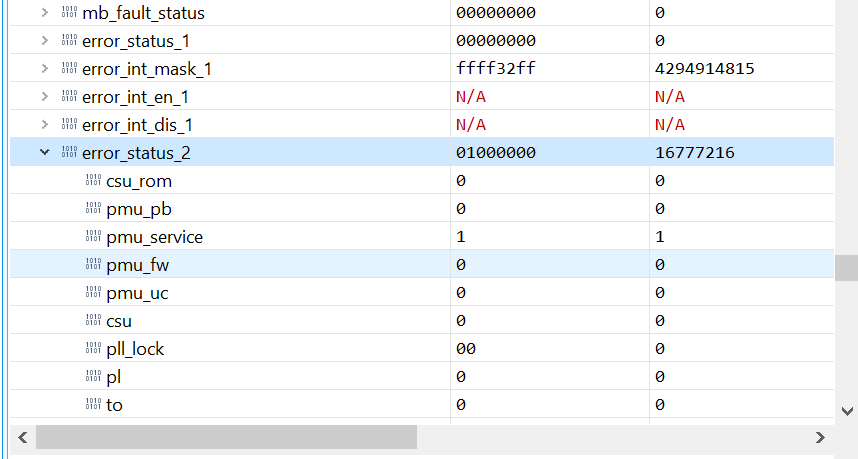

This project handles bare metal for all the below configurations. More to come soon! If there is a specific design you wish to see implemented in the project please reach out.

Currently Supported Aper-Oculus only needed example designs:

- TPG to PS DisplayPort

- MIPI CSI to PS DisplayPort

- TPG to MIPI DSI

- PetaLinux build with USB, DisplayPort, and SD

Currently Supported Example Designs with ApotheoTech's APT-C11-FMC (1 Device, 1 Host CoaXPress board):

- CoaXPress Host 2.0 from Basler Boost Camera to PS DisplayPort

- CoaXPress Device to Host loopback to DisplayPort

- MIPI CSI-2 data from Raspberri Pi camera to CoaXPress Device looback to CoaXPress Host to PS DisplayPort (Milestone Implementation)

Future Example Designs with ApotheoTech's APT-C40-FMC (4 Lane CoaXPress Device board in design)

- TPG to CoaXPress Device x4 lane to CoaXPress Host card (APT-C04-FMC) to suitable FPGA development board (ZCU106)

- MIPI CSI-2 data from Raspberri Pi camera to CoaXPress Device x4 lane to CoaXPress Host card (APT-C04-FMC) to suitable FPGA development board (ZCU106)

Future Supported Example Designs with ApotheoTech's APT-C04-FMC (4 Lane Host CoaXPress board in design)

- CoaXPress Host x2 lane to CoaXPress Camera (Using ZCU106 with APT-C40-FMC)

Future Supported Example Designs with ApotheoTech's APT-PIHAT-FMC (in design)

- Ubuntu build with PetaLinux Wifi enabled. PL for DSI and CSI-2 for expected Pi-Hat interfaces, and GPIO for PiHat. Other GPIO include Xilinx PMODs.

Chance Reimer

Chance Reimer

The next update will be proving the CoaXPress Host to a CXP camera using my FMC board. See you there!

The next update will be proving the CoaXPress Host to a CXP camera using my FMC board. See you there!

I'm actually brand new to PICs, and was unfamiliar with their interface, however, was able to still get the project running in about an hour thanks to ChatGPT, Github Copilot, and MPLab's Code Creator. Check the

I'm actually brand new to PICs, and was unfamiliar with their interface, however, was able to still get the project running in about an hour thanks to ChatGPT, Github Copilot, and MPLab's Code Creator. Check the

Jon Thomasson

Jon Thomasson

Tobias Rathje

Tobias Rathje

Ken Yap

Ken Yap

greg

greg