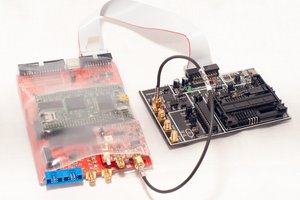

CPLD glue all written in VHDL and includes CPU clock generation, baud clock generation, address decoding, and SPI master. A few "registers" were implemented in the CPLD to allow soft-configuration of the SBC. The address decoder allows the uppermost 16K of EEPROM to be banked over the EEPROM. The Zilog SCC Ch A provides a 115.2kbps interface to the USB host via the FTDI bridge. A Zilog 8536 Complex Input Output (CIO) device provides 20 I/O pins as well as timers and a clever interrupt controller. The USB B connector is the host interface as well as a means to power the board.

HD6309 Singleboard Computer

Hitachi HD63C09 clocked at a blistering 3 MHz with a capacious 64K of RAM! Retroputing bliss...

tomcircuit

tomcircuit

Matthew Pearce

Matthew Pearce

Stuart

Stuart

Colin O'Flynn

Colin O'Flynn

Keith

Keith

I know, according to your logs here you were looking at Flex for the OS, What about NitrOS-9.... written to take advantage of the 6309, flexible memory model iirc.... hardware treated as modules to the kernel... I believe it's open source as well.