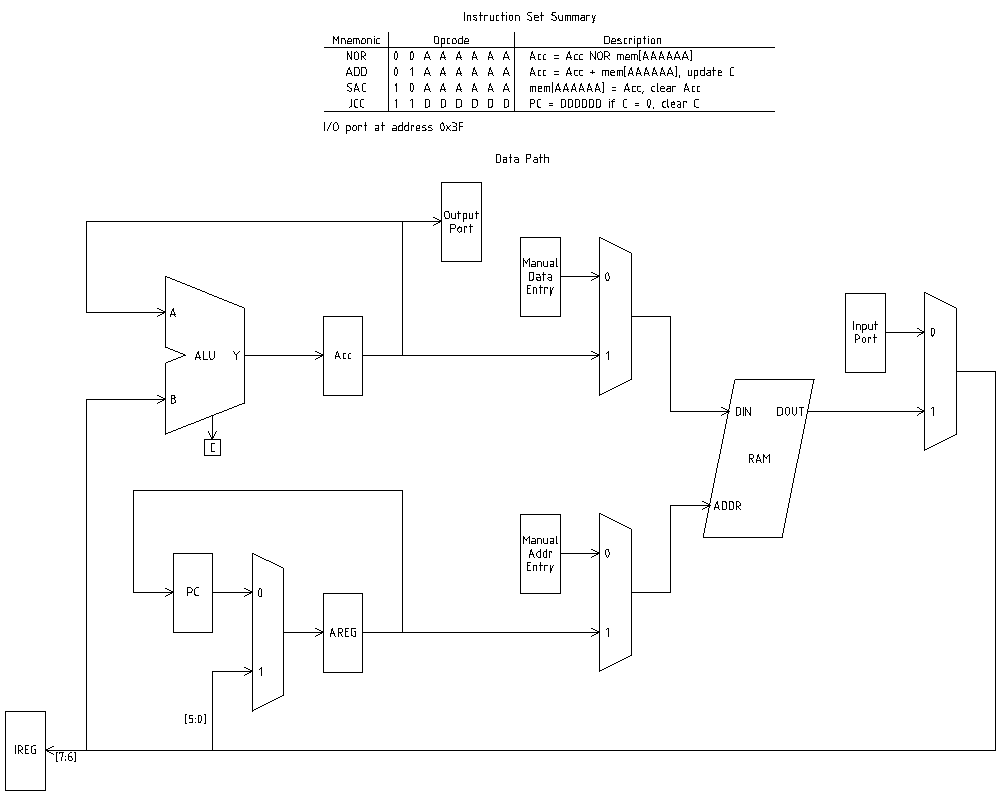

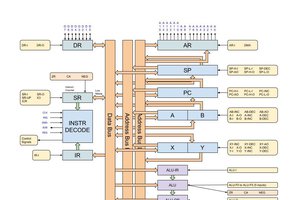

The system architecture is very basic: a single accumulator, 2-function ALU (NOR and ADD), 64-byte address space. It is based on Tim B ̈oscke's MCPU

Emphasis has been on simplicity of hardware and instruction format. All instructions fit within a single 8-bit byte. There are only 4 instructions, from which any required functionality can be synthesised. This will minimise the amount of control logic needed, and is a philosophy I have borrowed from the designers of the venerable PDP-8.

Programs, data and the I/O ports share the same 64-byte address space.

Andrew Starr

Andrew Starr

2-Zons

2-Zons

agp.cooper

agp.cooper

Brandon Reinhart

Brandon Reinhart

spudfishScott

spudfishScott

Amazing!