For practical reasons (it's impossible to list everything on the 'net), the "project" is mostly about gathering people from HaD who built their CPU (or at the very least digital electronic devices). Here are some external links for those who just can't get enough:

- http://www.ttlcpu.com/content/links

- http://members.iinet.net.au/~daveb/simplex/ringhome.html => moved to http://homebrewcpuring.org/

- http://www.bigmessowires.com/nibbler/

- http://www.alles.or.jp/~thisida/mycpu_tk80photo.html

- https://en.wikibooks.org/wiki/Microprocessor_Design/Wire_Wrap

- http://www.megaprocessor.com

- http://www.witch-e.org (https://hackaday.io/project/19955-witch-e )

- http://monster6502.com

Feel free to suggest or add links of the same kind :-)

PS: the project's logo comes from Wikipedia

PPS: let's not forget the two lists https://hackaday.io/list/2402-homebrew-computers and https://hackaday.io/list/25846-homebrew-cpu but note they are subject to curator delay (and taste).

Logs:

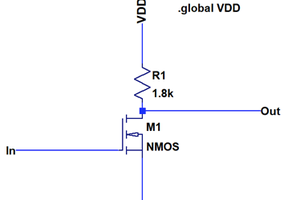

1. Dynamic RAM with single MOSFET per bit ?

2. Bizarre DTL Logic Levels - The Discrete Component PDP-8

3. The Electronics of IBM Standard Modular System Logic

4. ECL or CTL : what's the fastest topology for discrete gates ? [updated]

5. TTL inside

6. Direct Coupled Transistor Logic

7. Interactive Simulations of DEC R-Series Logic

8. Why is ECL faster ?

9. Bipolar XOR gate with only 2 transistors

10. Video Explaining DEC R-Series DTL

11. The rule of 50 (or so)

12. Bipolar transistors are ANDN gates !

13. The return of CTL

14. From XOR to MUX

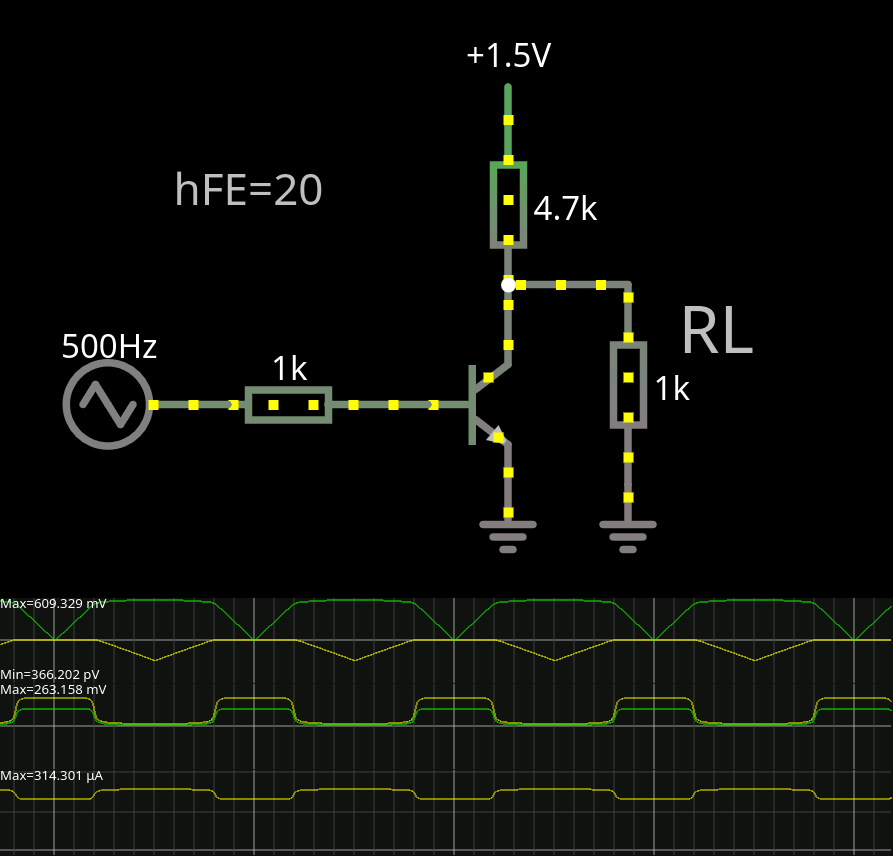

15. From MUX to Latch

16. Project proposal : Ring oscillators zoo !

17. Analog Multiplexer Logic

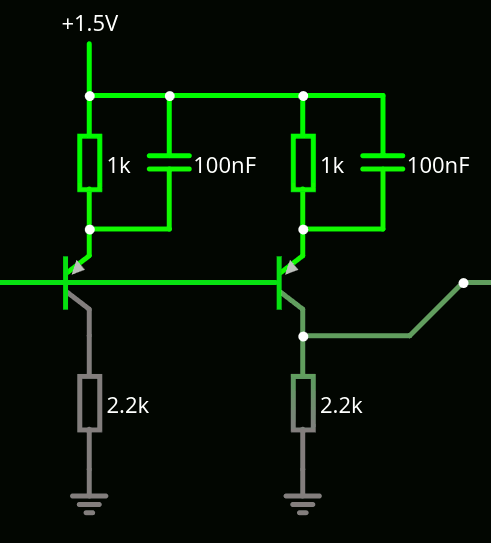

18. Another RTL/DCTL latch

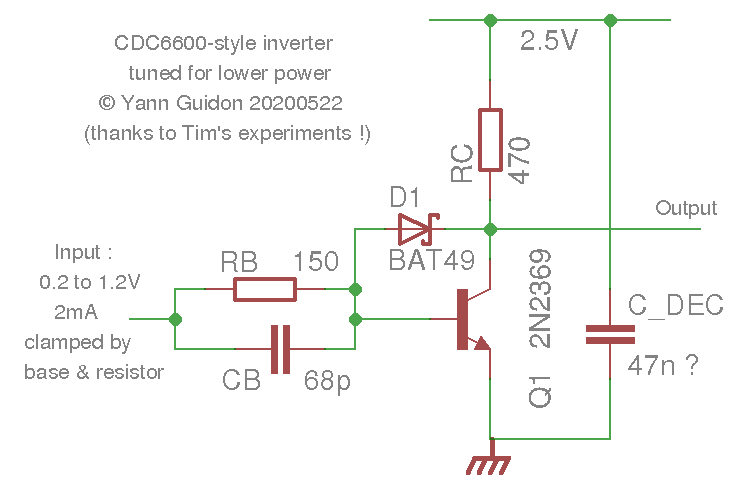

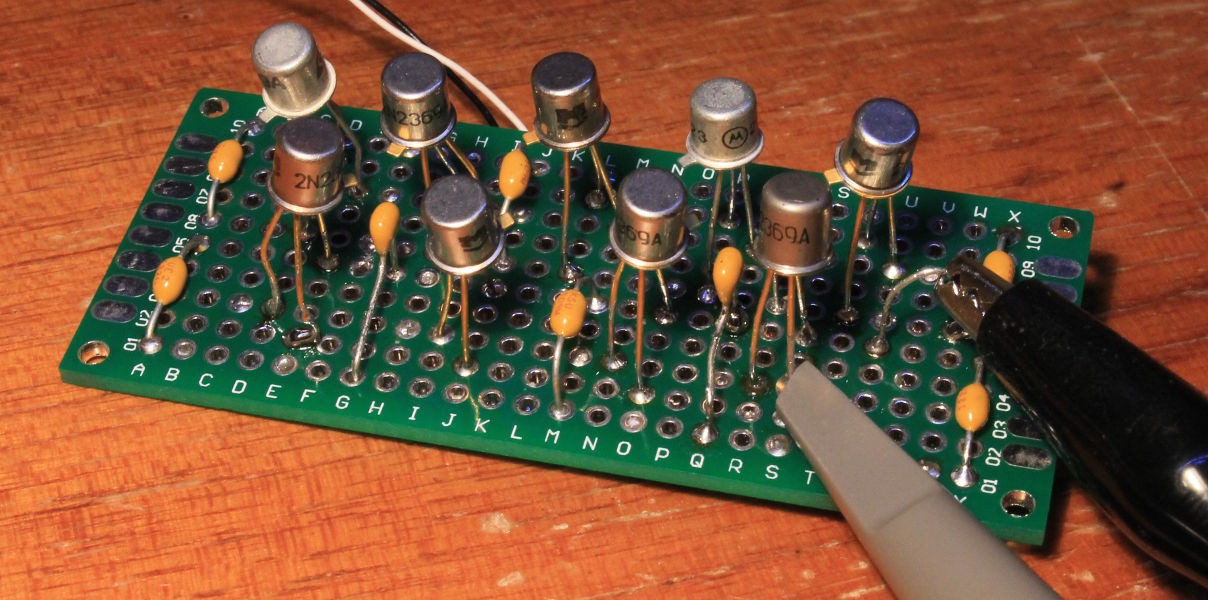

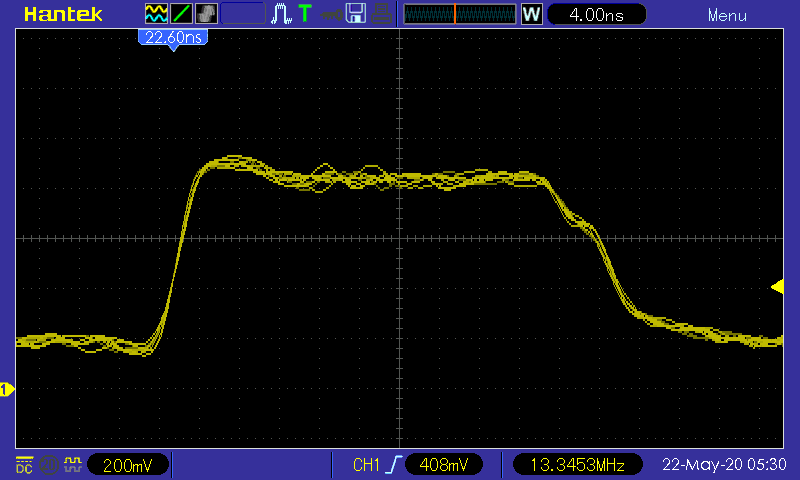

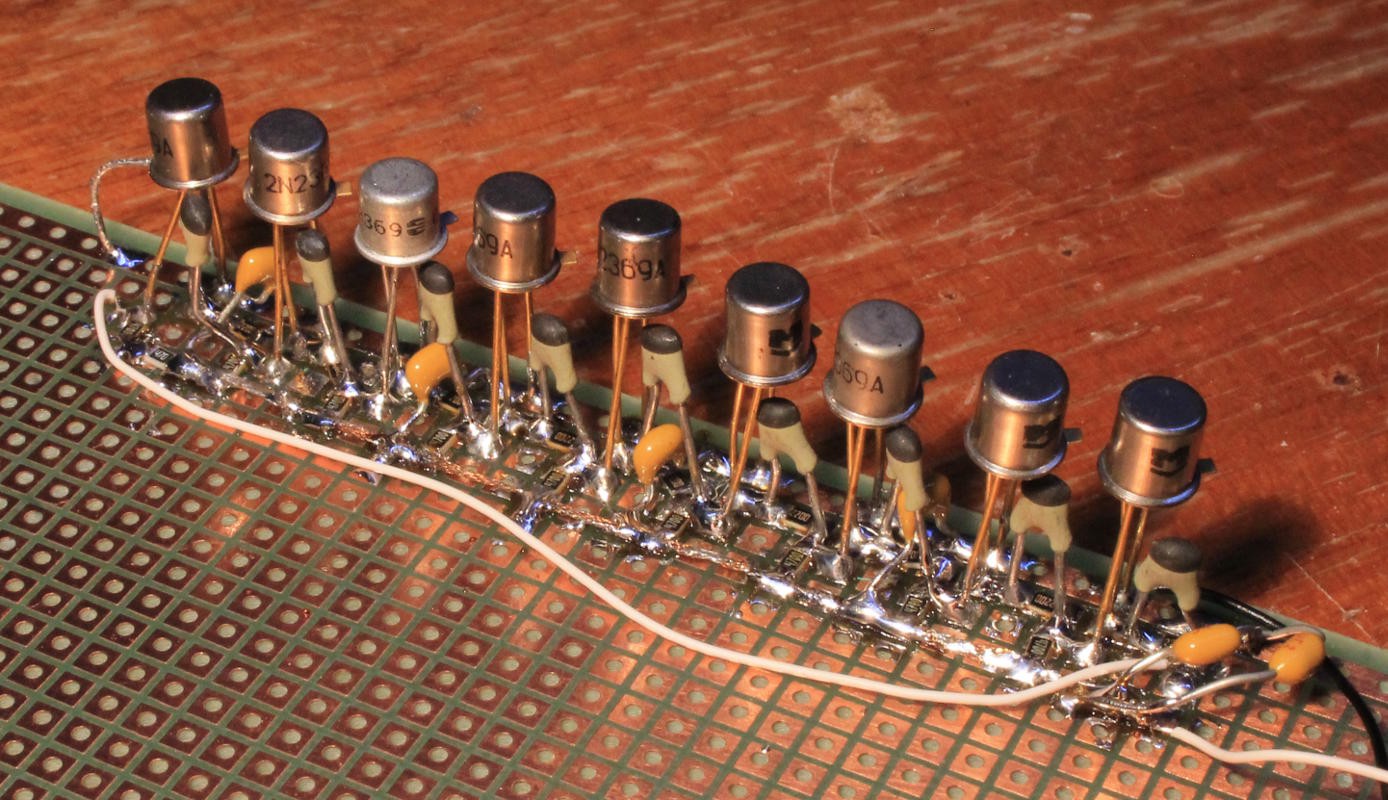

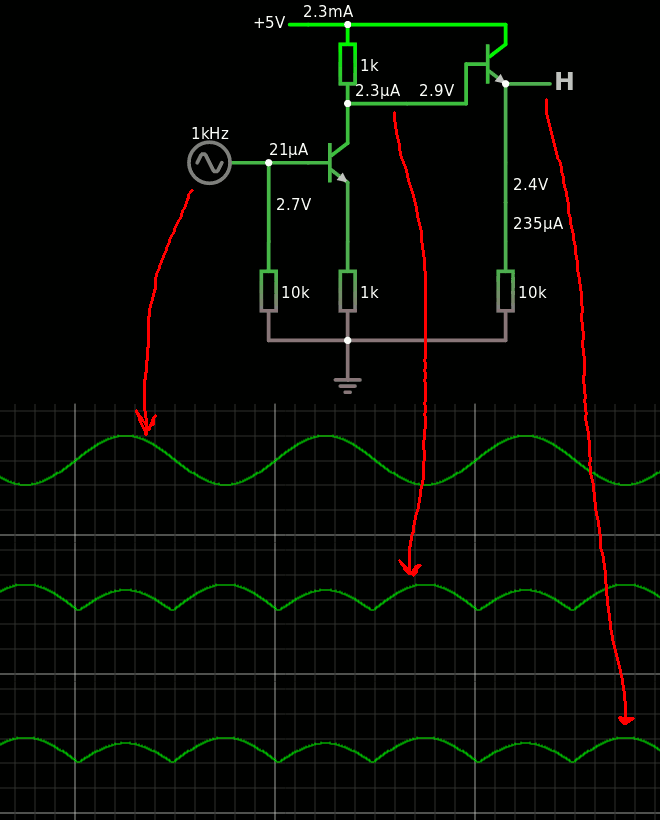

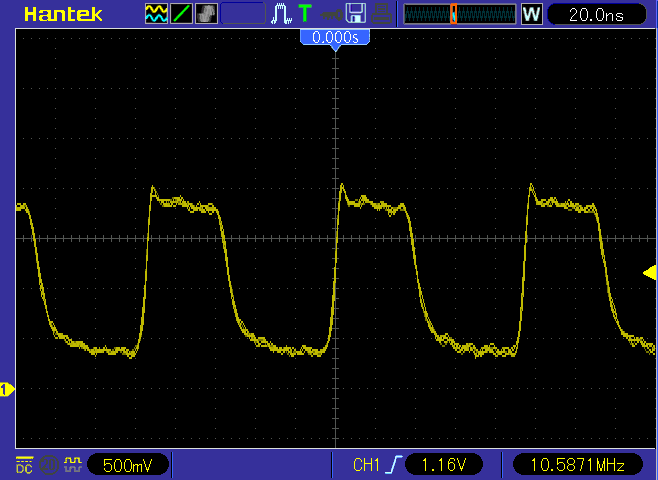

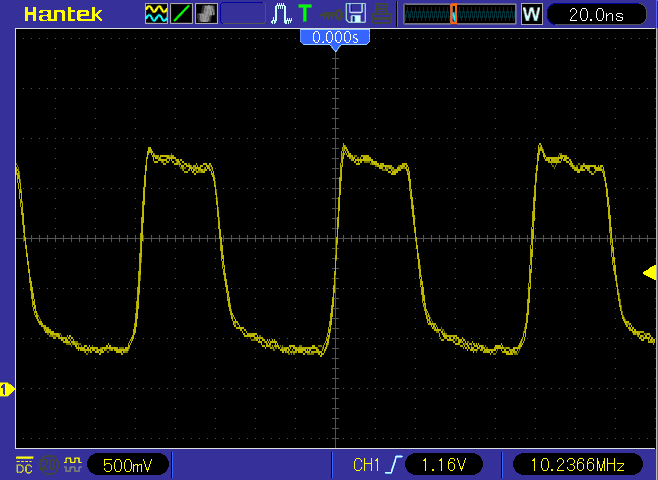

19. My own try at a RingO9 with 2N2369A

20. unexpected frequency doubler or rectifier

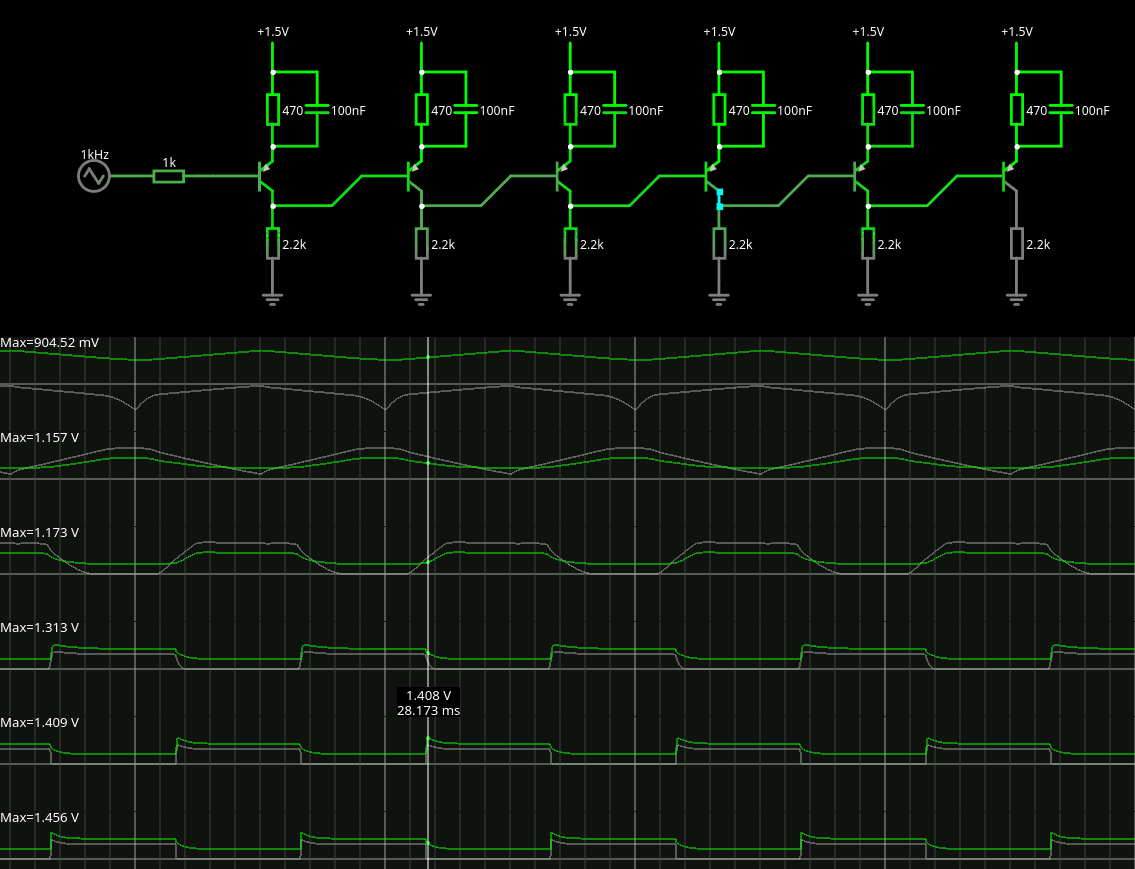

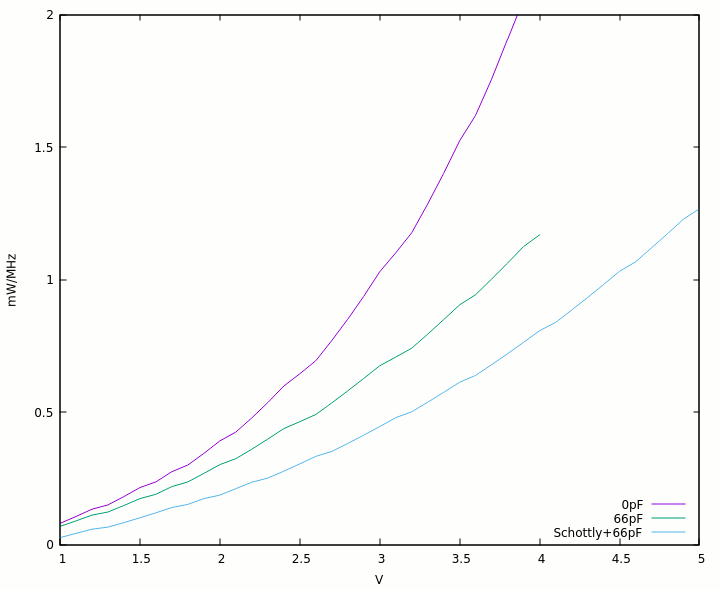

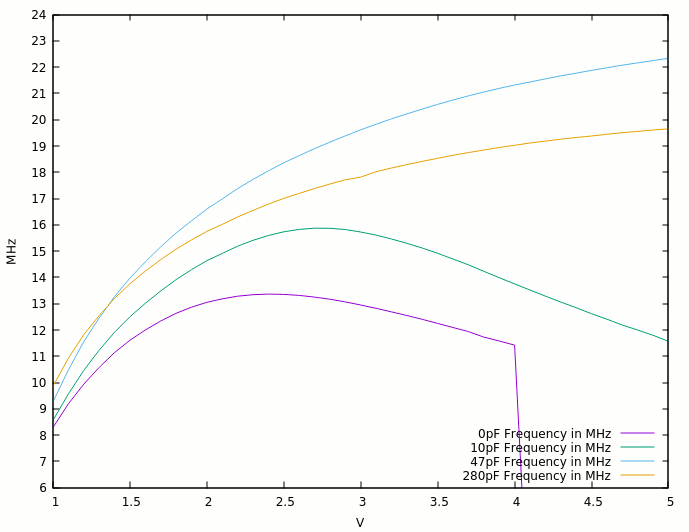

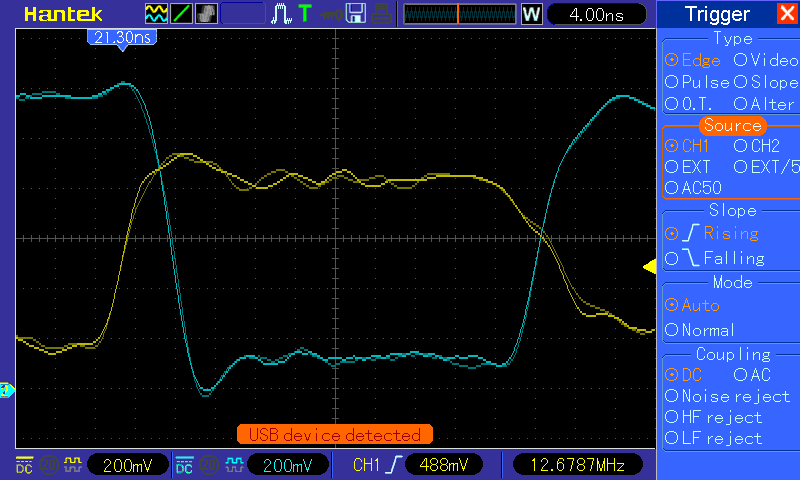

21. More 2369, with more caps !

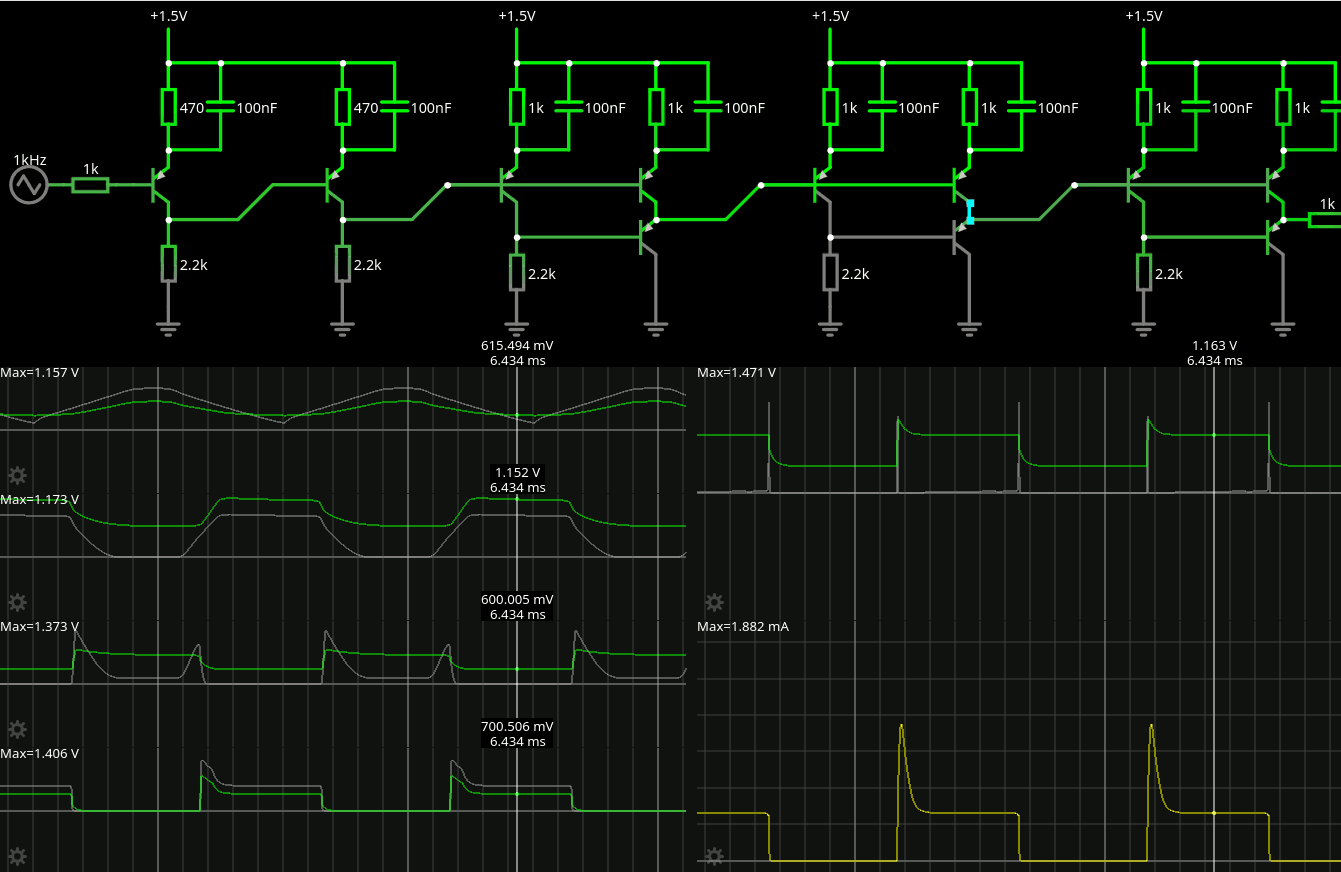

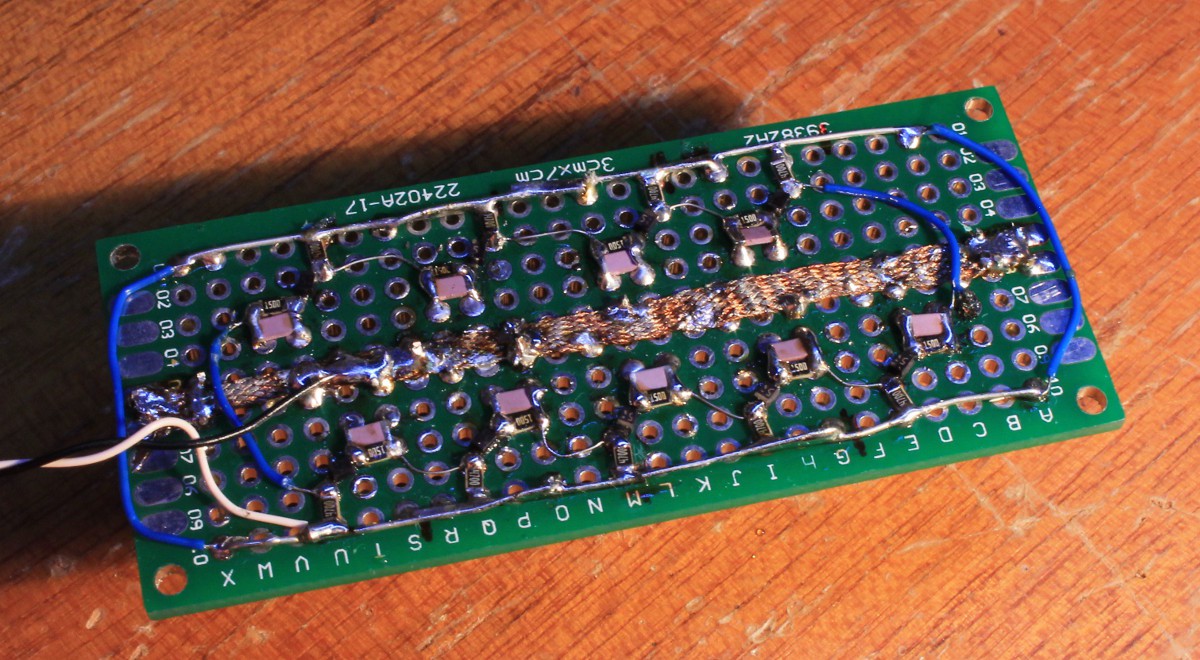

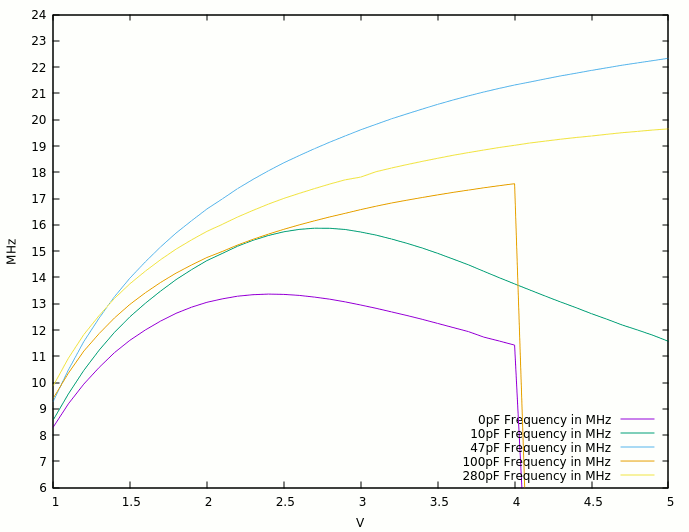

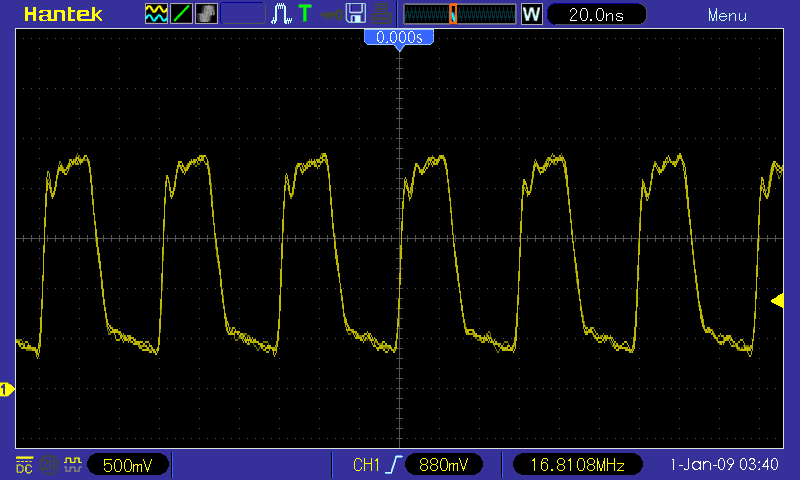

22. RingO9 v2 : closer to CDC specs !

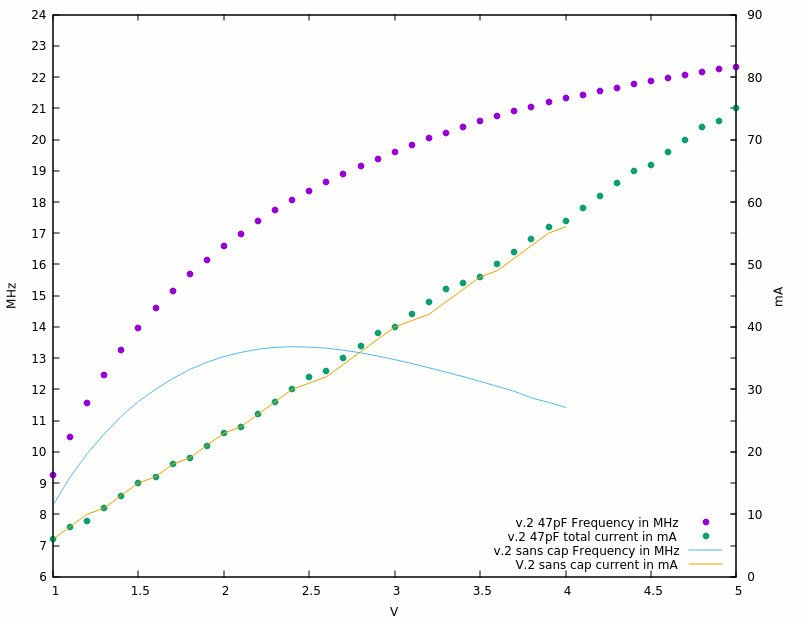

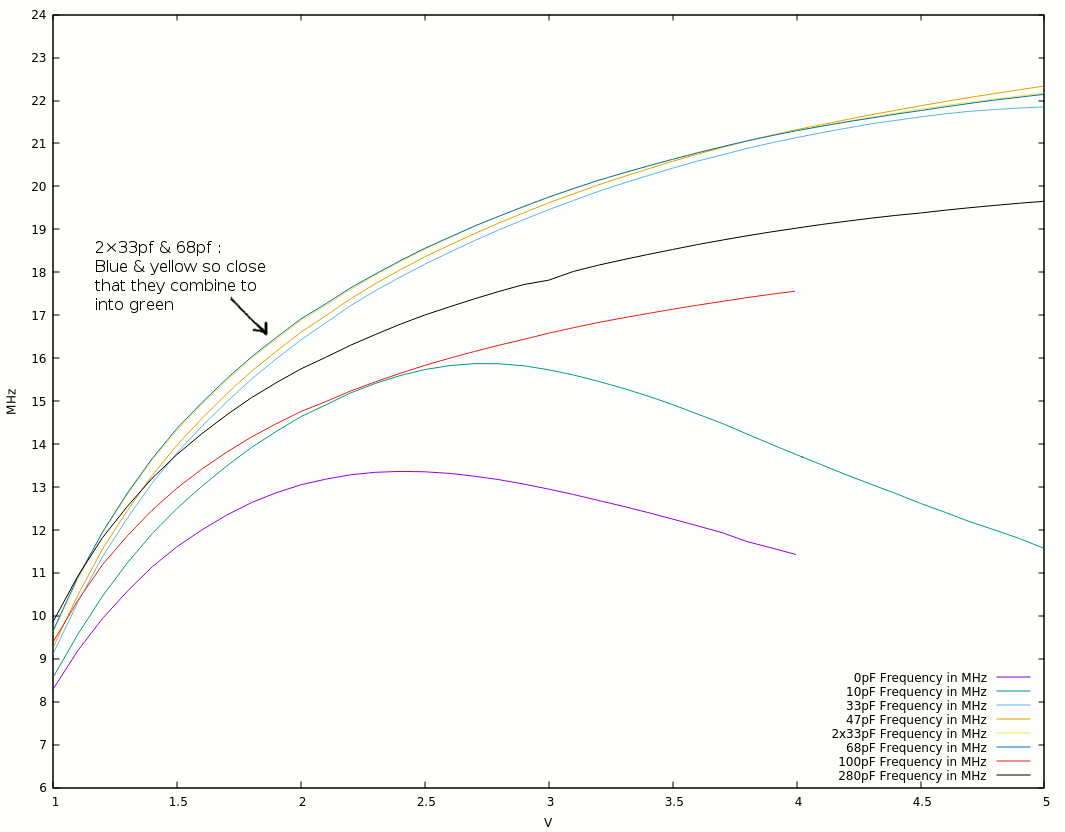

23. RingO9 v2 : with caps !

24. Beyond 2ns with 2N2369A

25. Dear Marcel

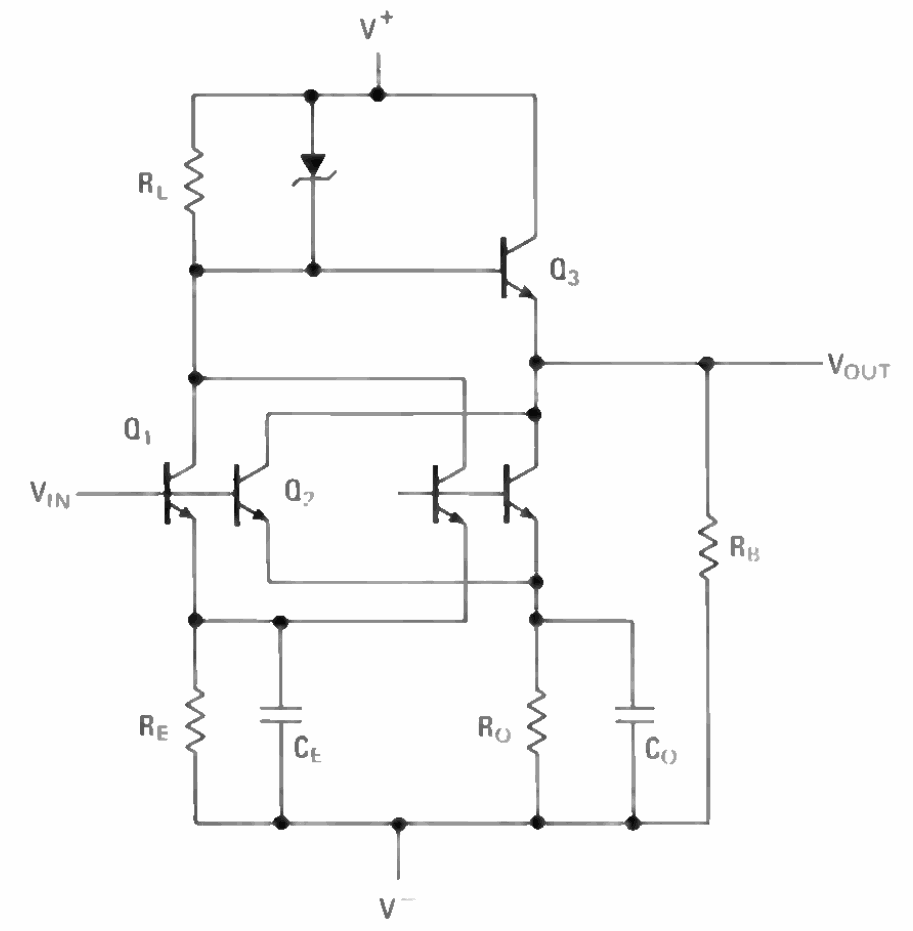

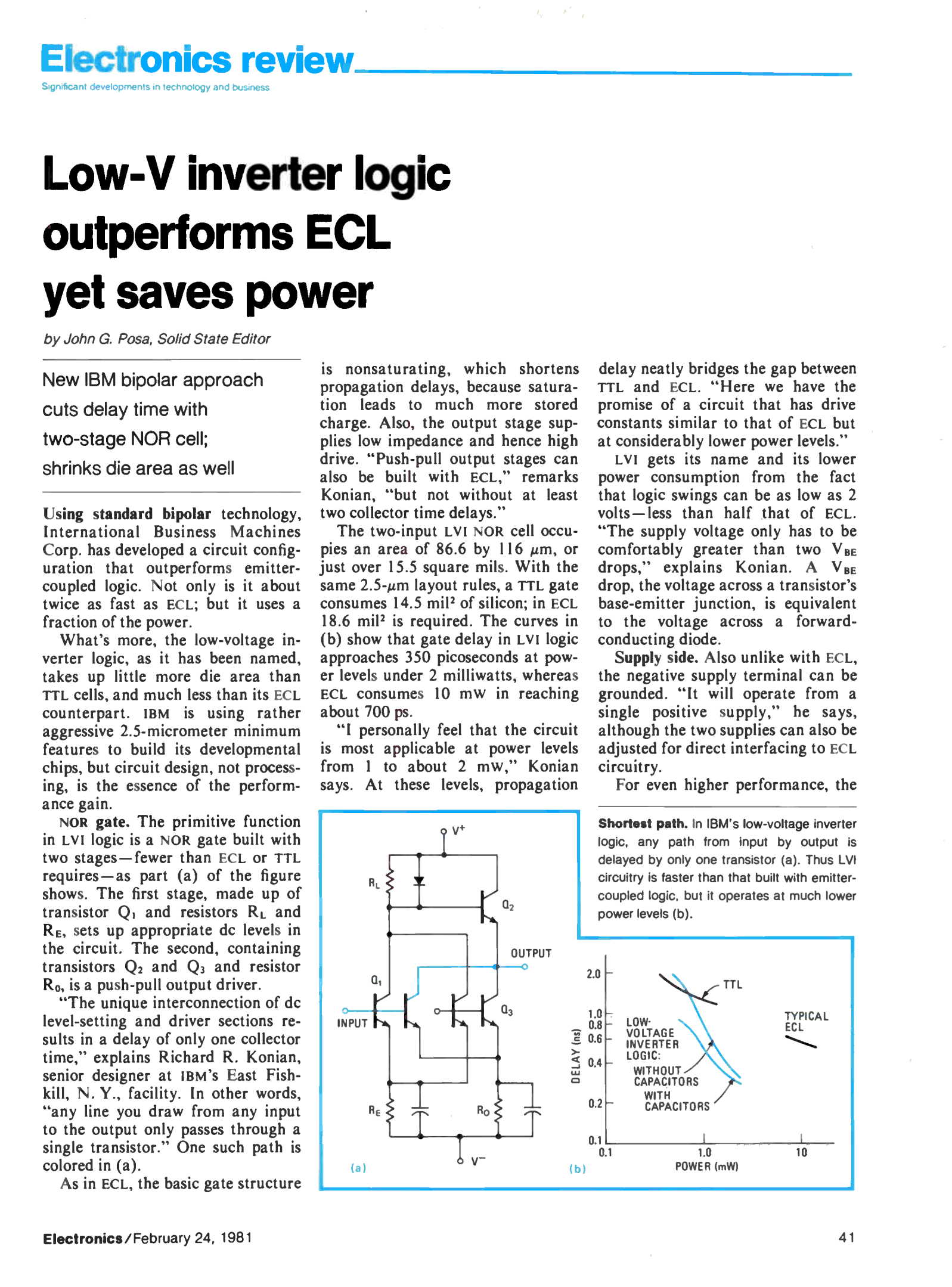

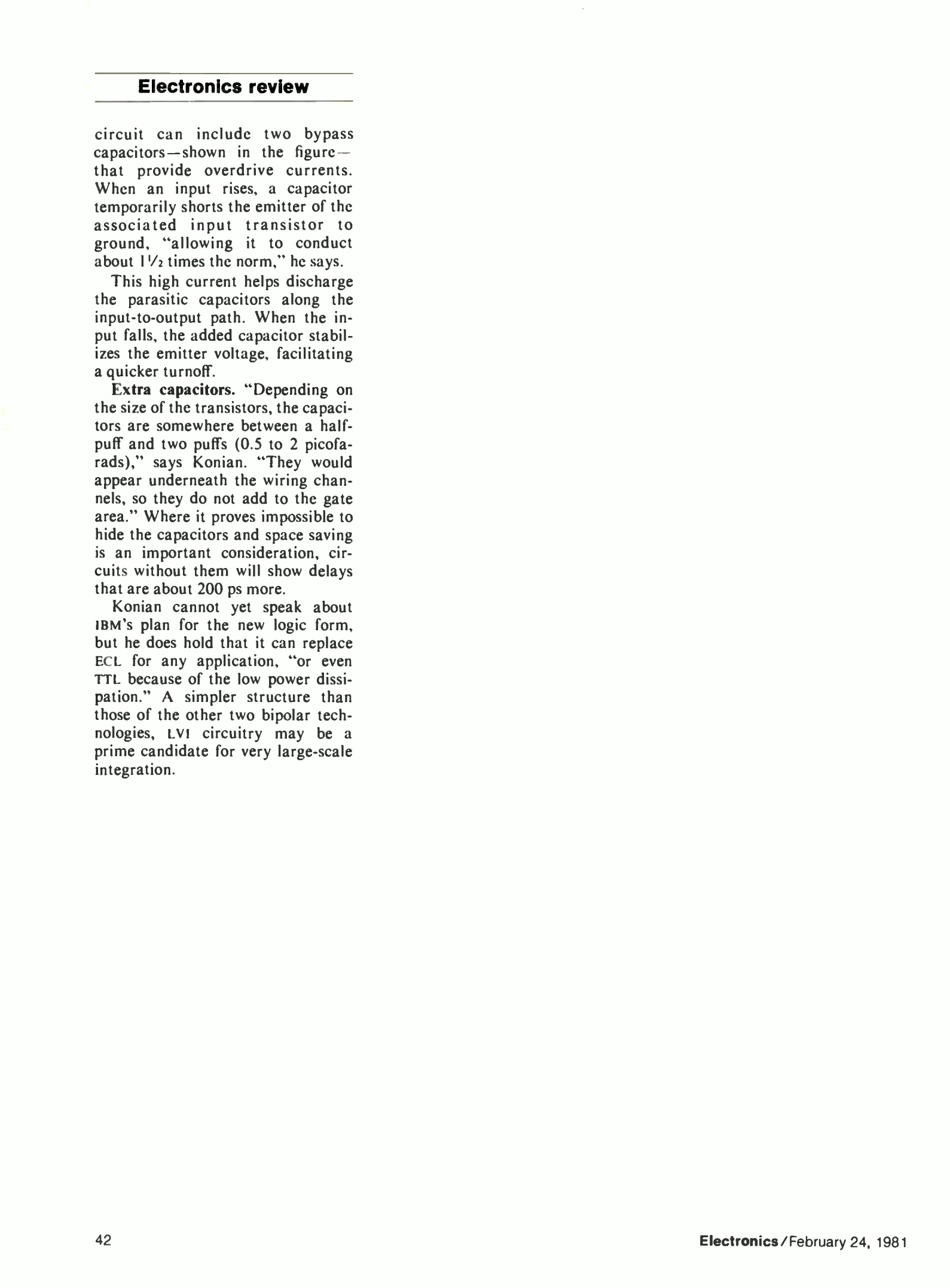

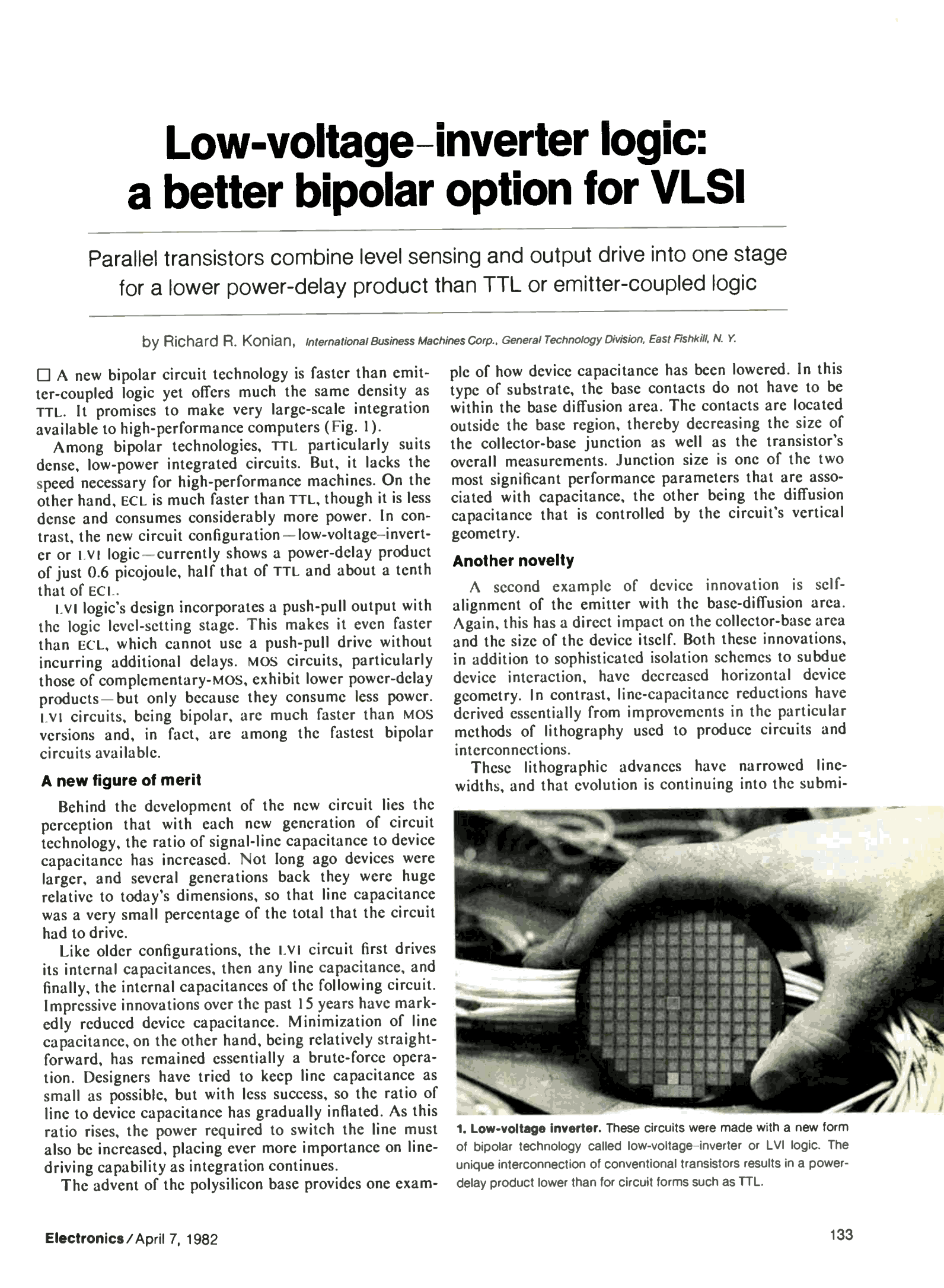

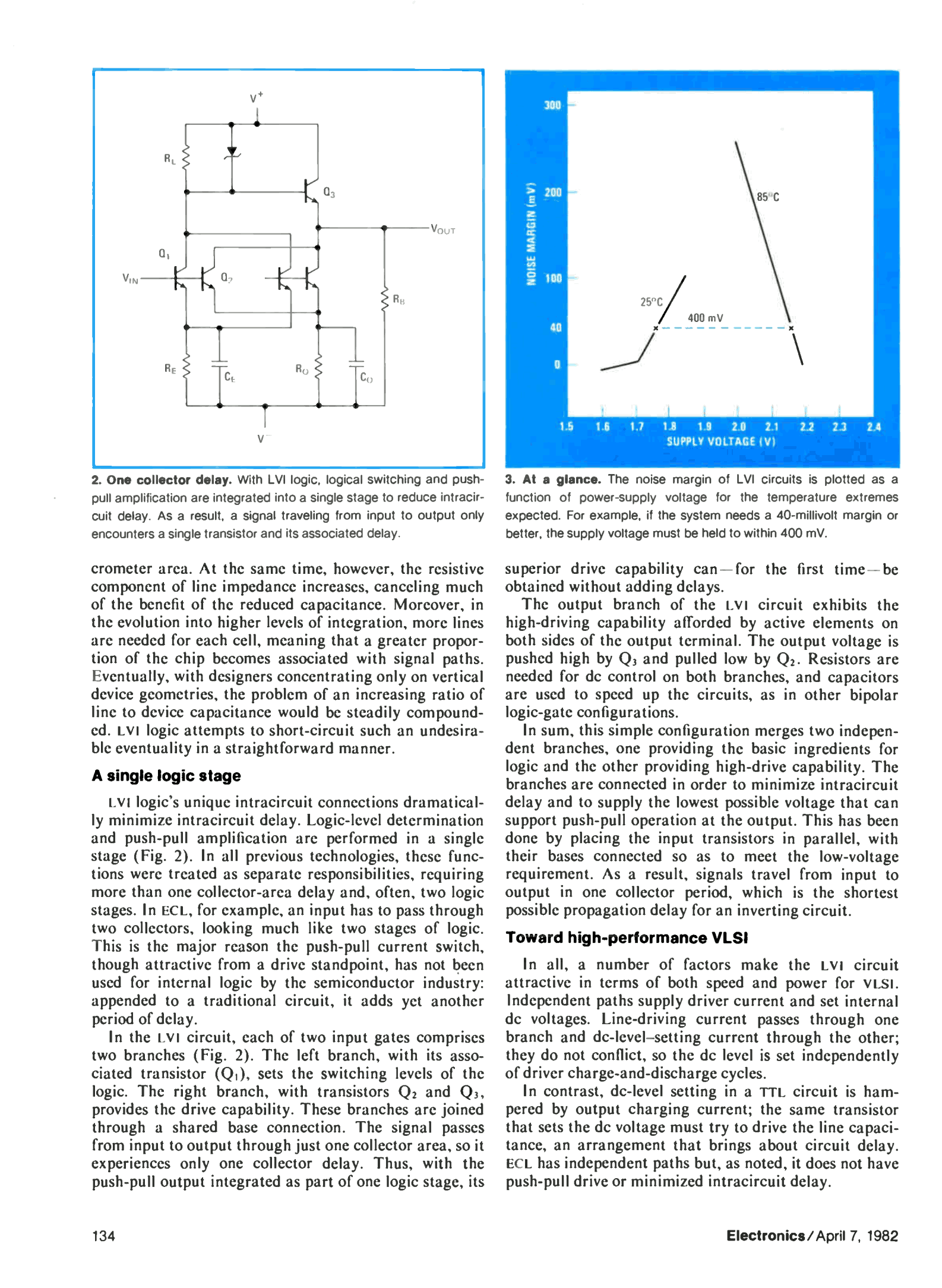

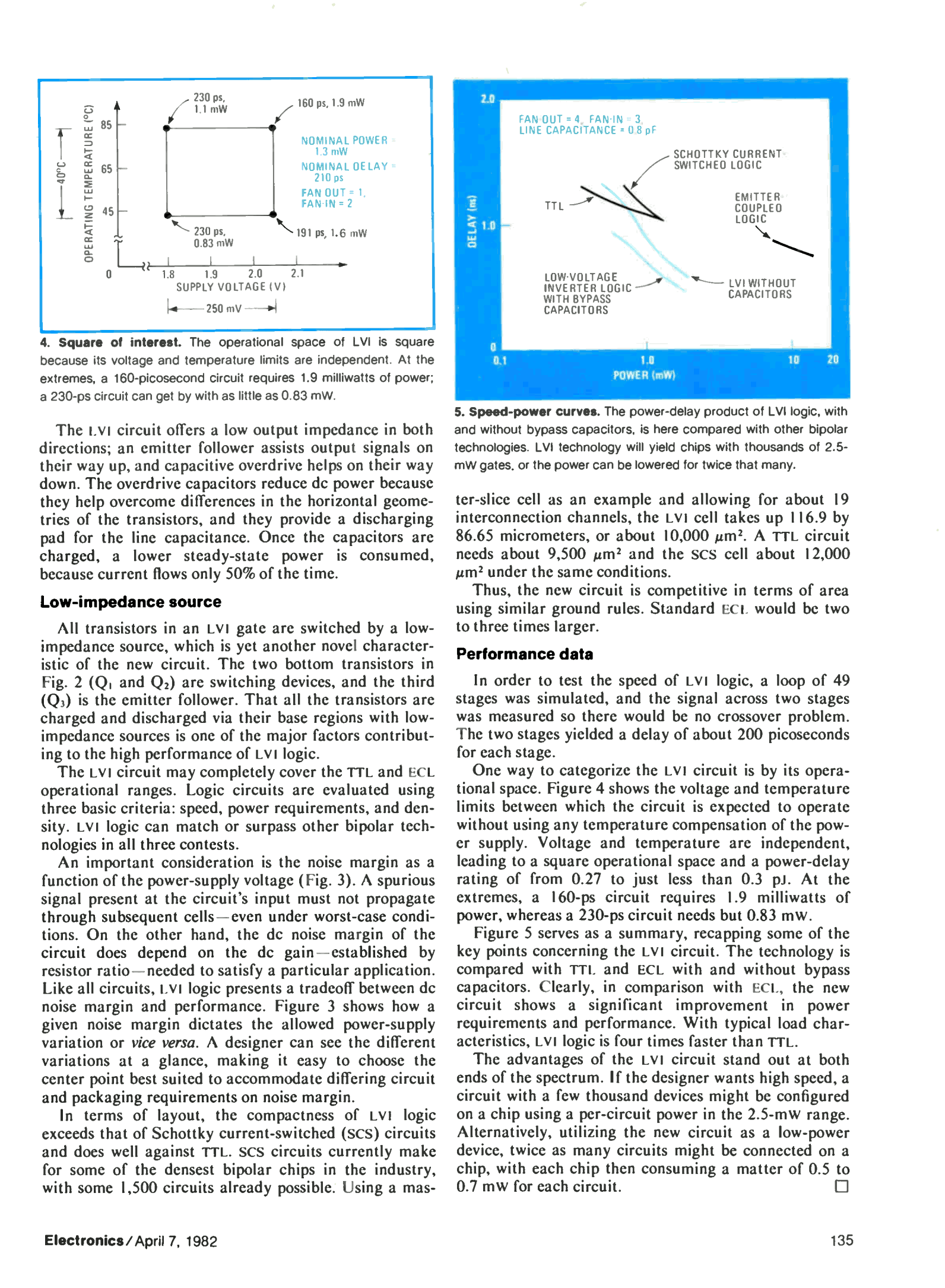

26. IBM's LVI (Low-Voltage Inversion Logic)

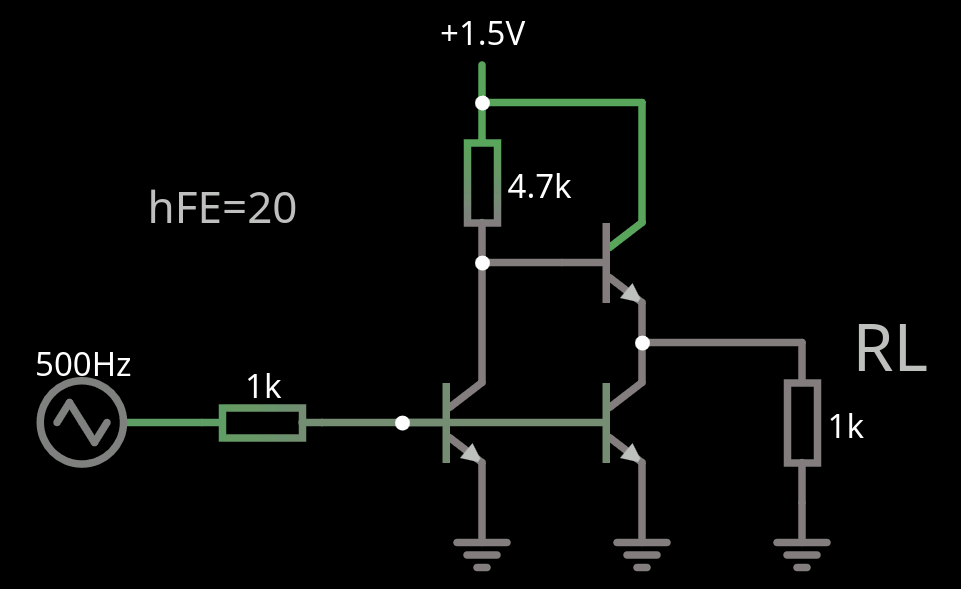

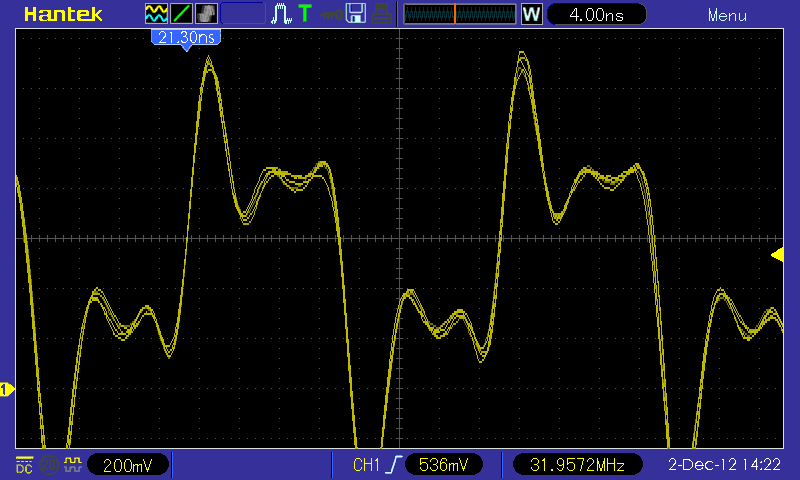

27. Reconstructing IBM's LVI (Low-Voltage Inversion Logic)

28. Attempting to design custom LVI inverters

.

.

Yann Guidon / YGDES

Yann Guidon / YGDES

will.stevens

will.stevens

Tim

Tim

I find logic families hard to use without a set of concise reference cards. Thus https://hackaday.io/project/191205-4000-series-logic-reference-cards - a set of 4x6" 4000-series CMOS logic reference cards. It covers everything you can buy from Texas Instruments today - and that's a lot of 14- and 16-pin parts still made in DIP, IIRC well over 100. I've checked that you can indeed still buy them by, well, actually buying a dozen of everything they sell in DIP. At least a year ago TI still sold every part with a black part# on the ref sheets. Grey part#s are not made anymore.

24-pin parts are only SMD, they dropped the big DIPs. They still make some of the 24-pin parts in high-rel or milspec CERDIP (expensive). I've also included selected legacy parts that aren't sold new anymore, but are still available in plentiful supply on the secondary market.

I have a bit of a vested interest in keeping this family alive, since I use it in projects, and would hate for it to disappear due to lack of demand. TI themselves does a rather poor job of keeping the 4000 family in relevant parametric search results. A few of the parts are only visible by searching for the specific part number and don't appear in tabulated results.

Getting a similar reference sheet for 74-family parts will be a bigger endeavor, since there's way more of them, across several logic families, etc.