Overview

The Original "Baby" was a valve computer built at Manchester University. It was the first computer to have "General Purpose RAM" memory that could be used as Program and Data Storage. Whilst nothing of the original remains there is a replica of the machine at the Museum of Science and Industry in Manchester. There is a Video of this replica on YouTube here:-

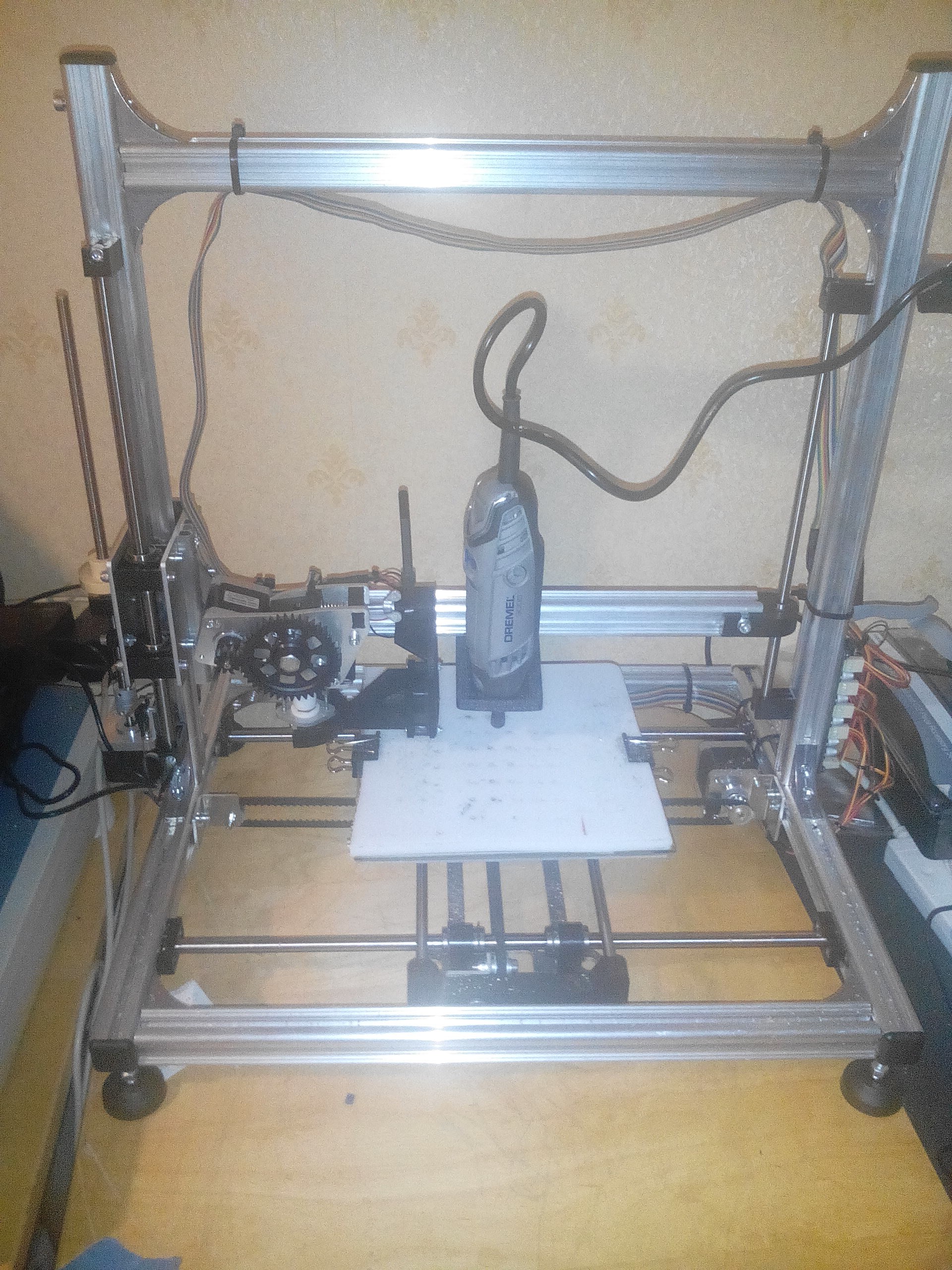

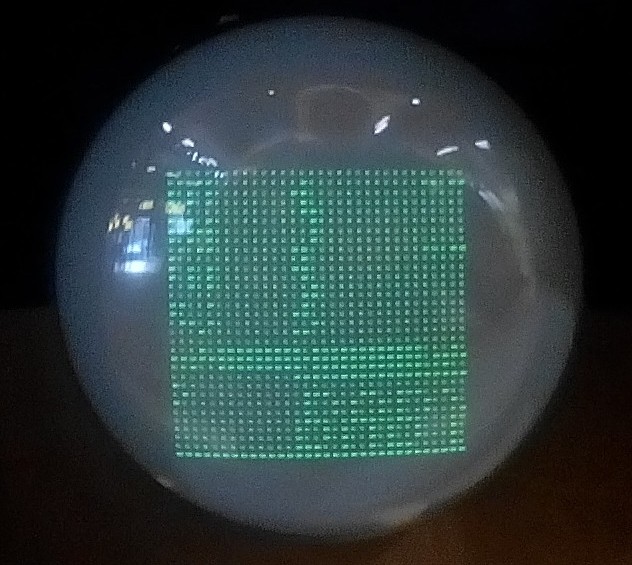

I demonstrate this machine as a volunteer and so wanted ti know more about how the baby works. I thought the best way to do this was to build my own baby. Rather than just write a software emulation I decided that by using an FPGA I could build something that was a more accurate and realistic representation of the full sized machine. Along the way I also used my 3D printer as a CNC machine to drill the holes for the buttons and SPI expander chips to interface the buttons to the FPGA. The result is the "Baby Baby" a small scale replica of the Baby that replicates the spirit of the original but of a size that can fit in a small modern house.

Demonstration Video

The machine is almost complete. Here is a video showing it in operation and demonstrating its key features.

dave

dave

Howard Jones

Howard Jones

Marcel van Kervinck

Marcel van Kervinck

Hi,

I'm in the process of producing some KiCAD schematics for the SSEM really at the logic level rather than hardware specific. I was wondering if you completed this with the images on the Computer Preservation societies pages or had another information? I'm hoping by comparing those with your VHDL I can work out what is going on.

Would be interested to know who you implemented the subtracter it not really what I expected.