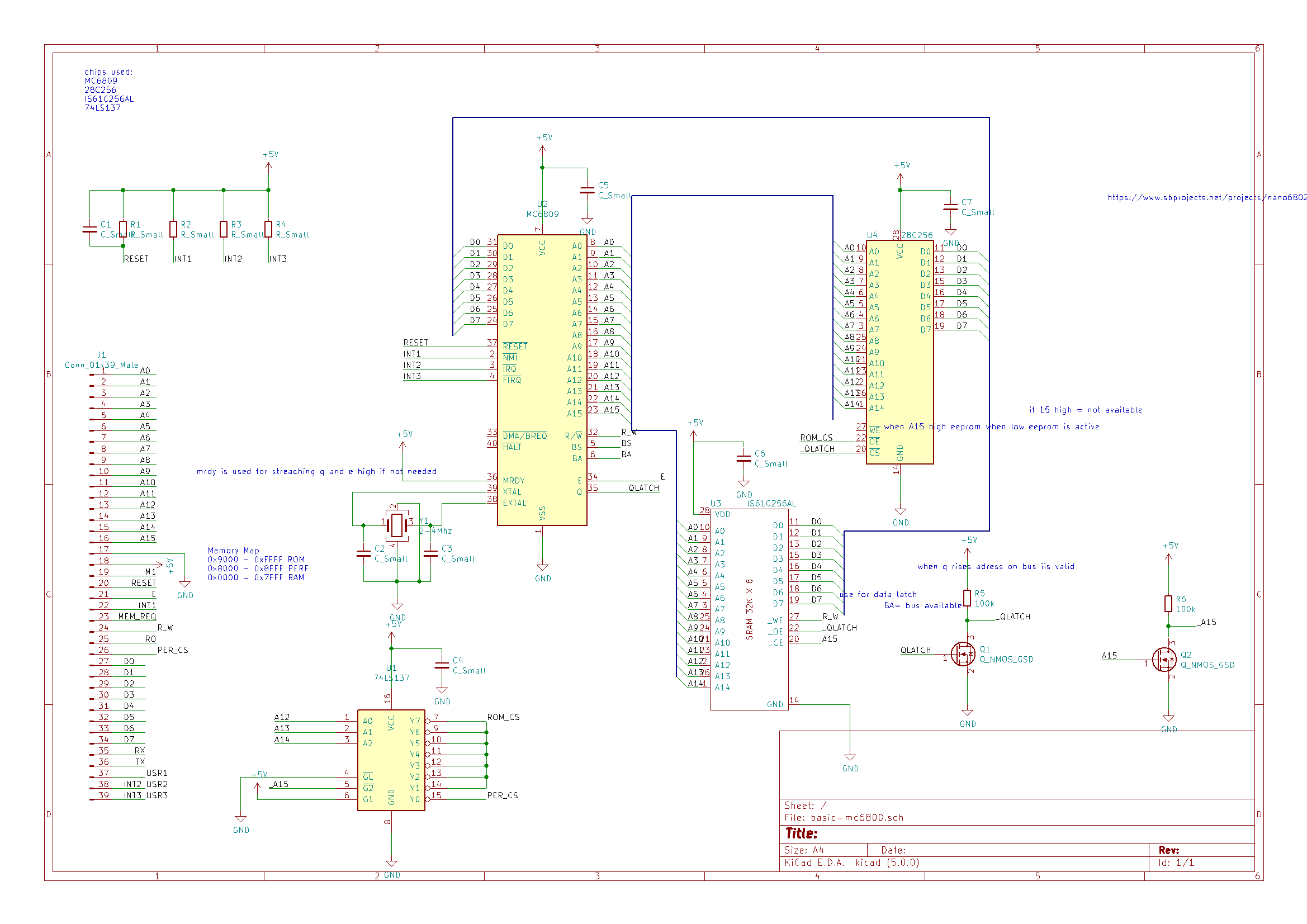

For this system i decided to select the Motorola MC6809 MPU

There where a few reasons for this selection I wanted to use a processor from the MC6800 series they where

- Prolific as the processor of choice in many arcade cabinets.

- The layout was easy to understand.

- |t doesn't require much in the way of supporting hardware.

- I felt it was a bit of an unsung hero as most people focus on the MOS6502 and the Z80 CPUs

The project for me is getting a CPU running and taking to other hardware using system buses and control lines and how this would interpret into FPGA fabric.

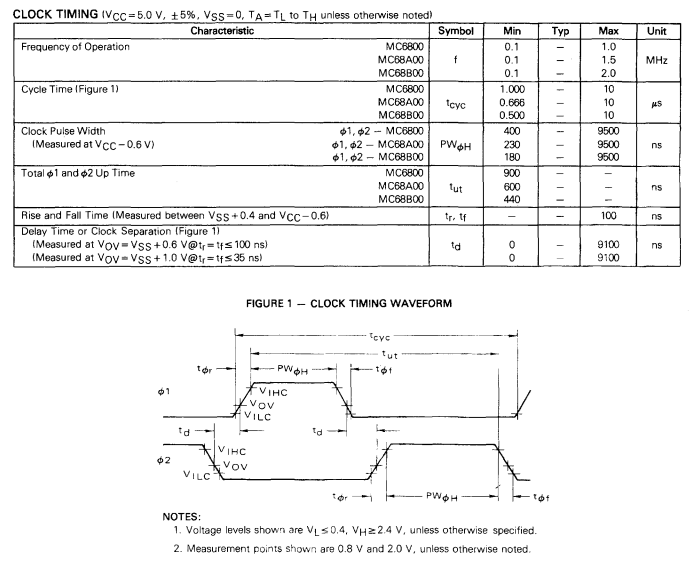

The MC6809 specifically has the ability to run directly for a xtal crystal which made it much simpler the the MC6800 which requires two clock pulses at specific intervals

This is the complicated clock requirements of the MC6800 the is an ic made by Motorola the MC6875 clock generator, but these ICs are rare and expensive.

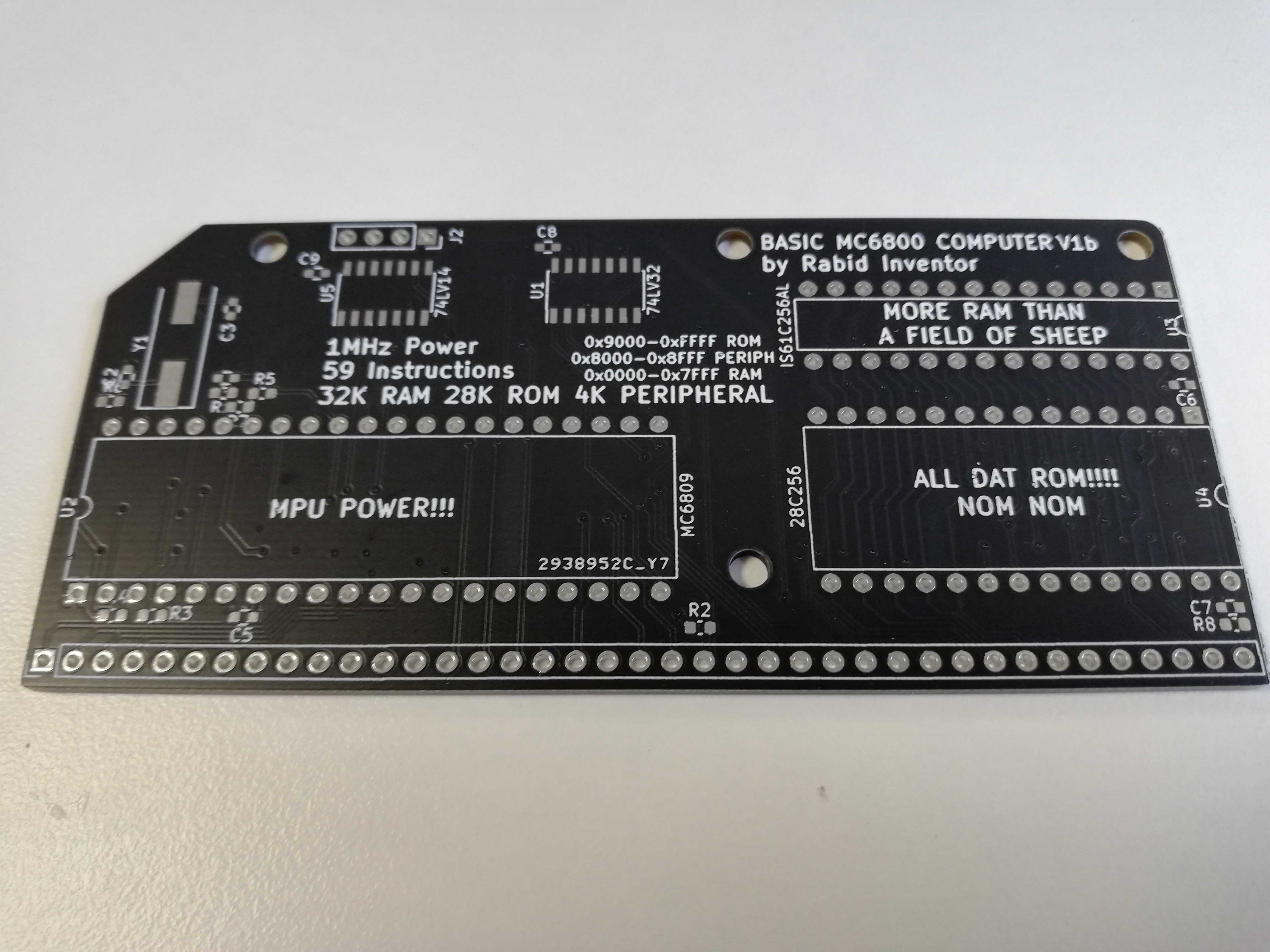

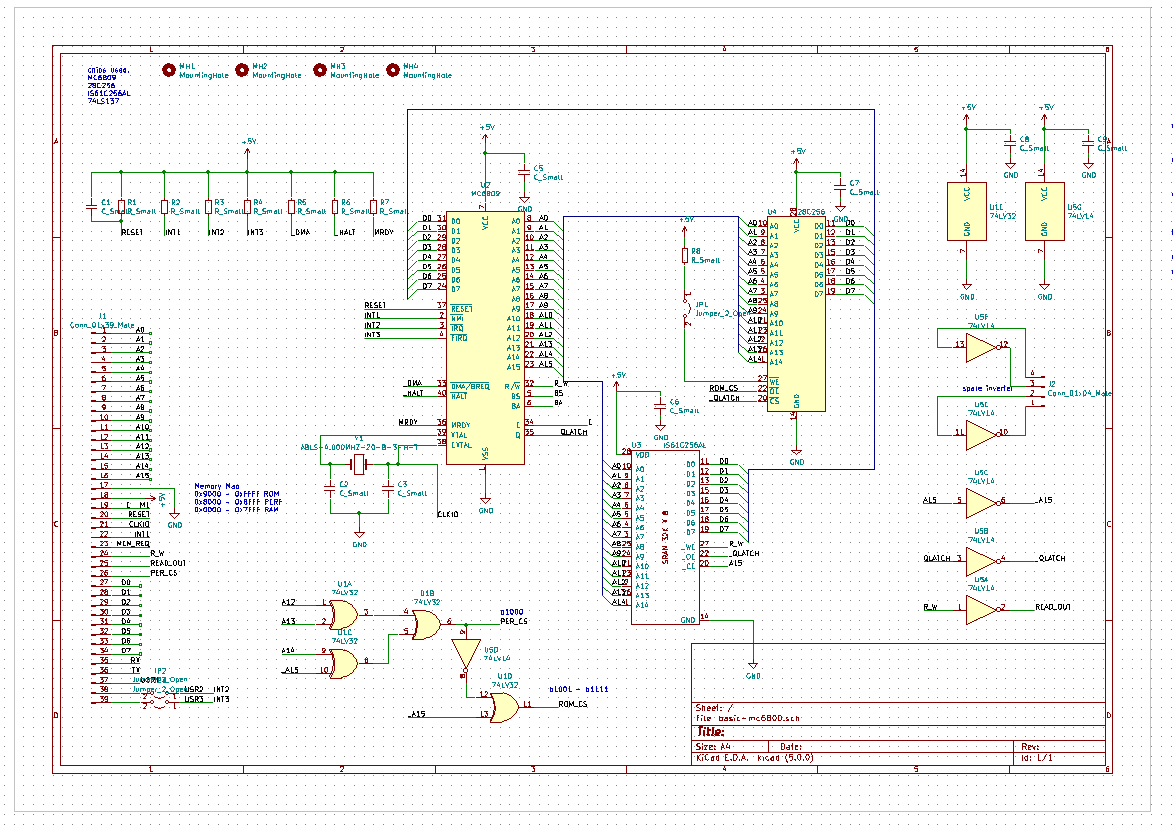

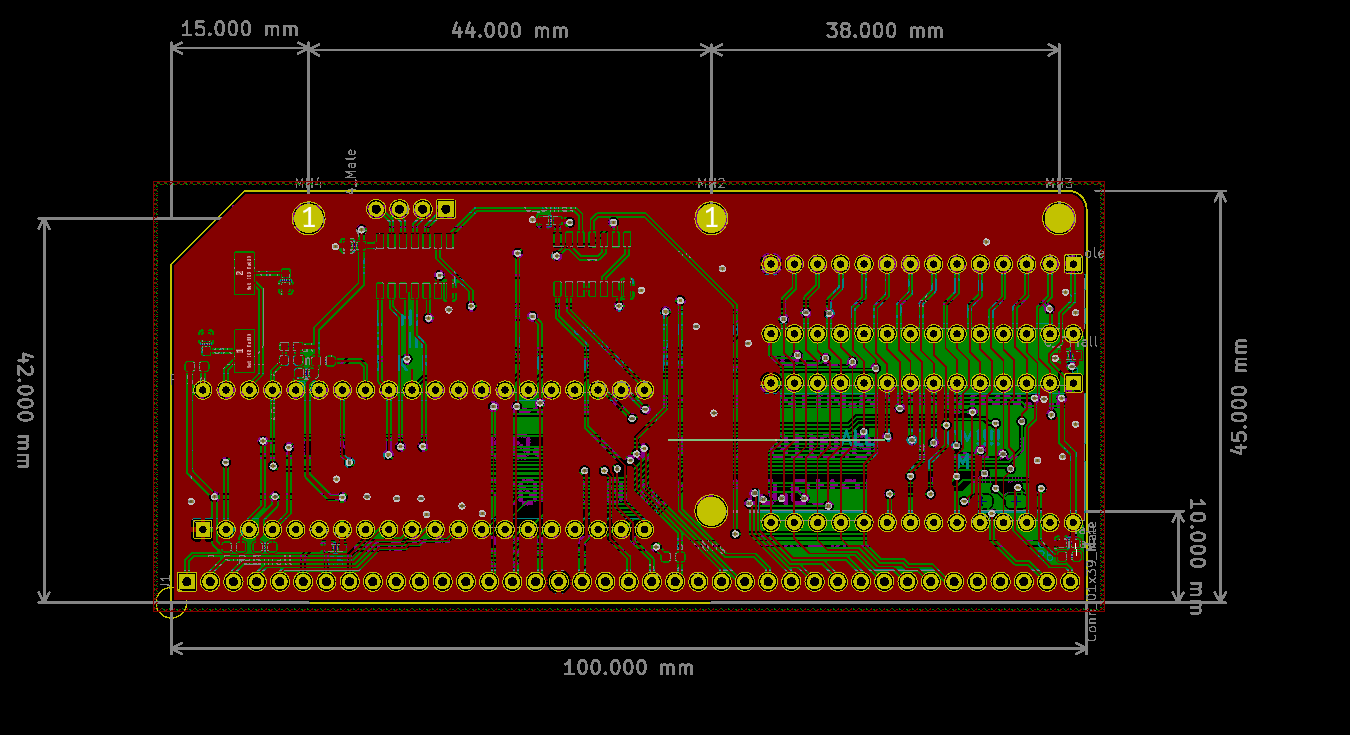

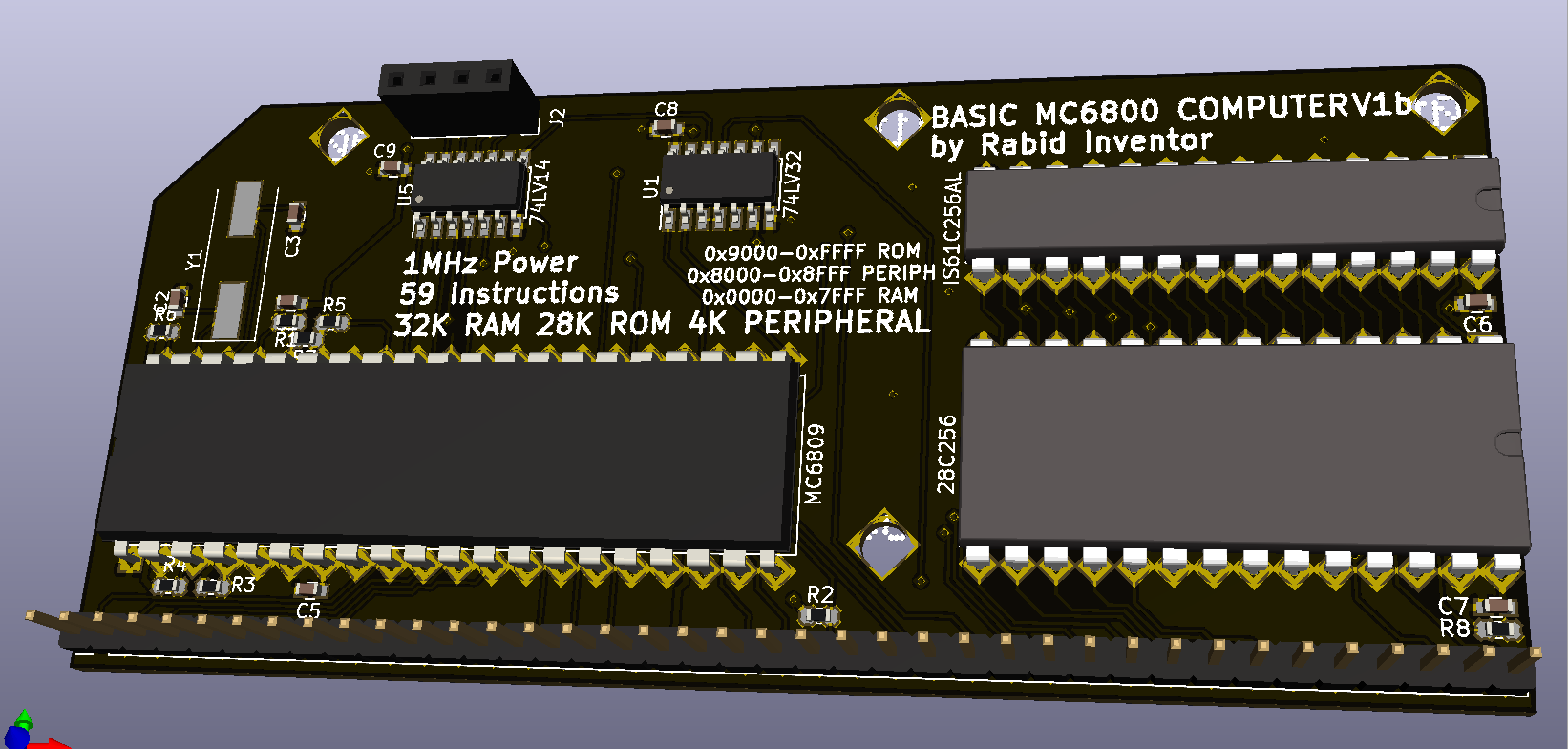

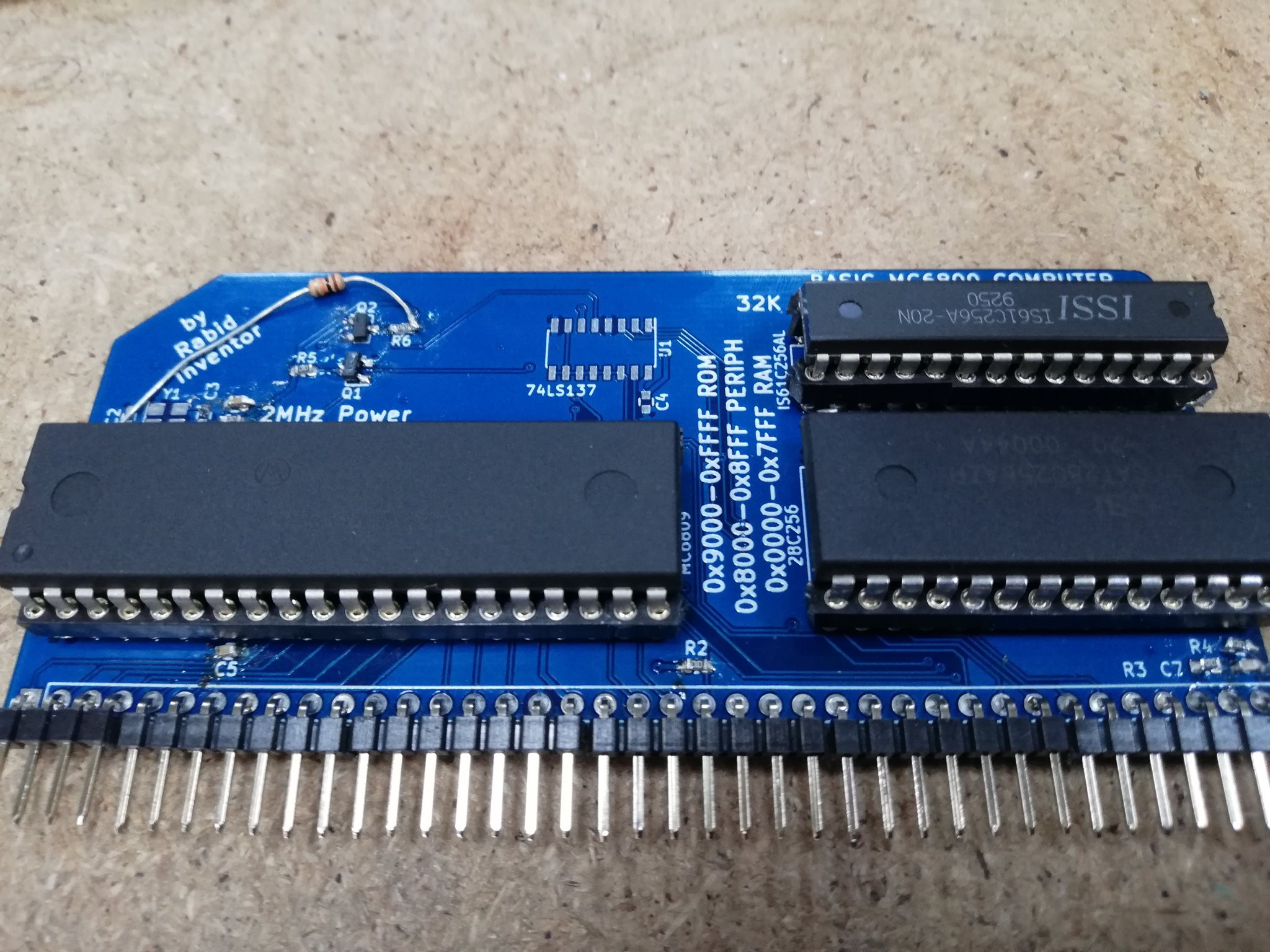

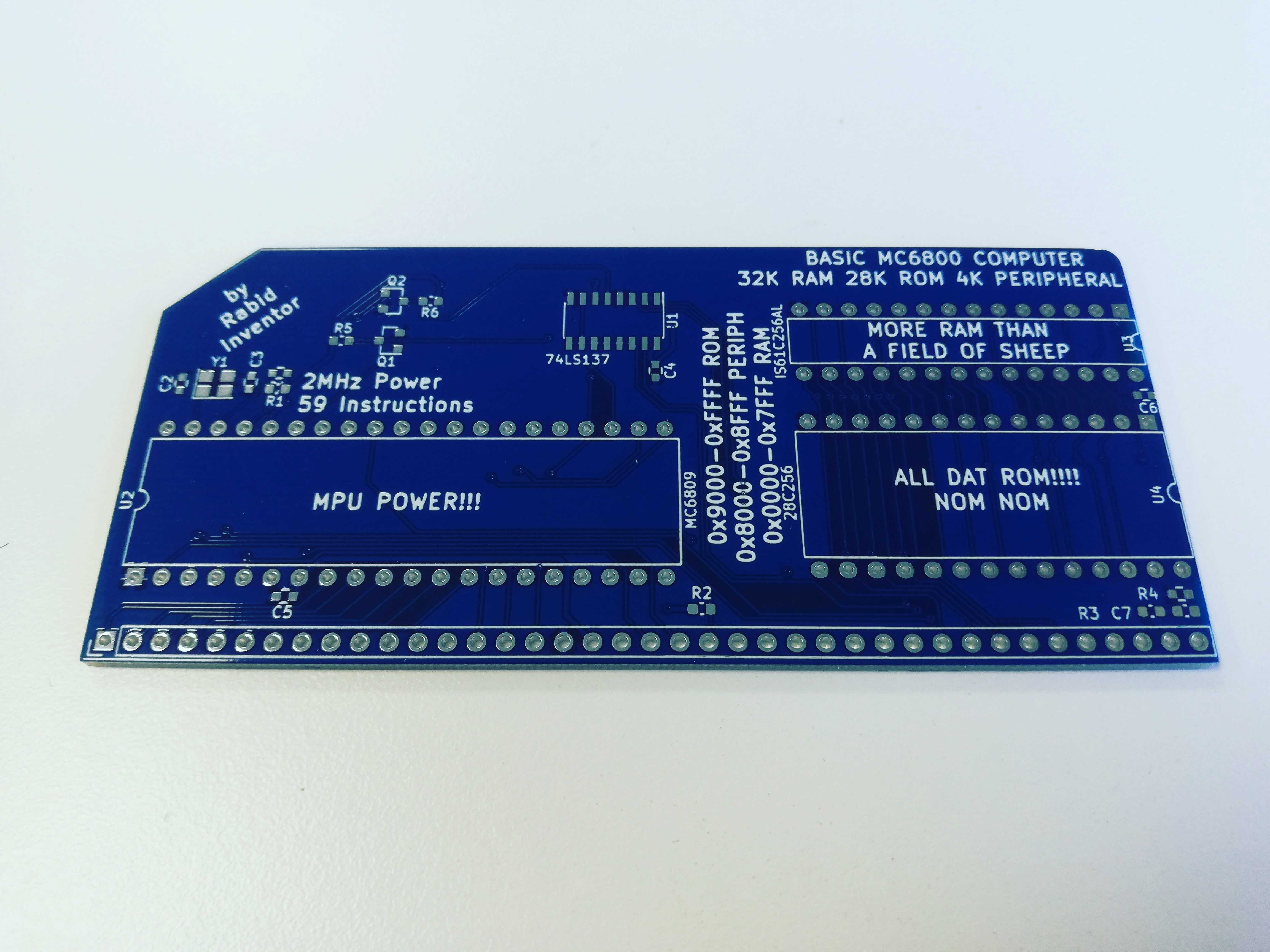

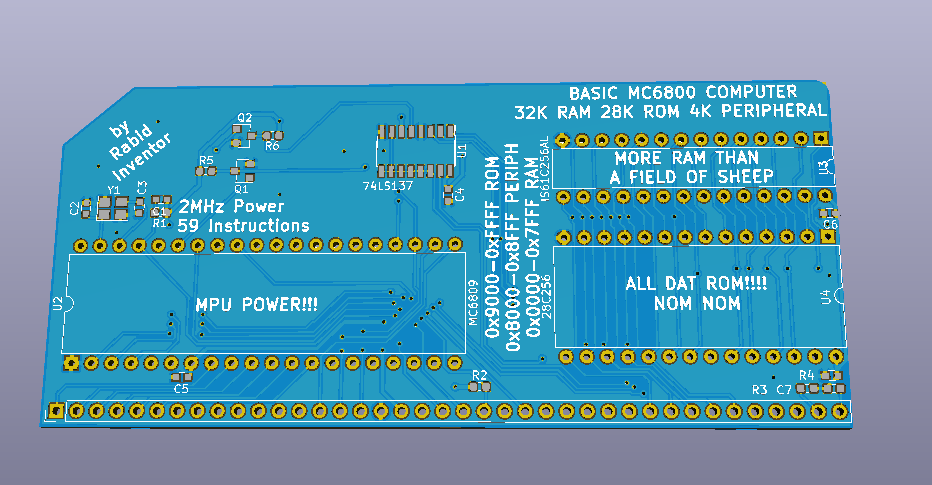

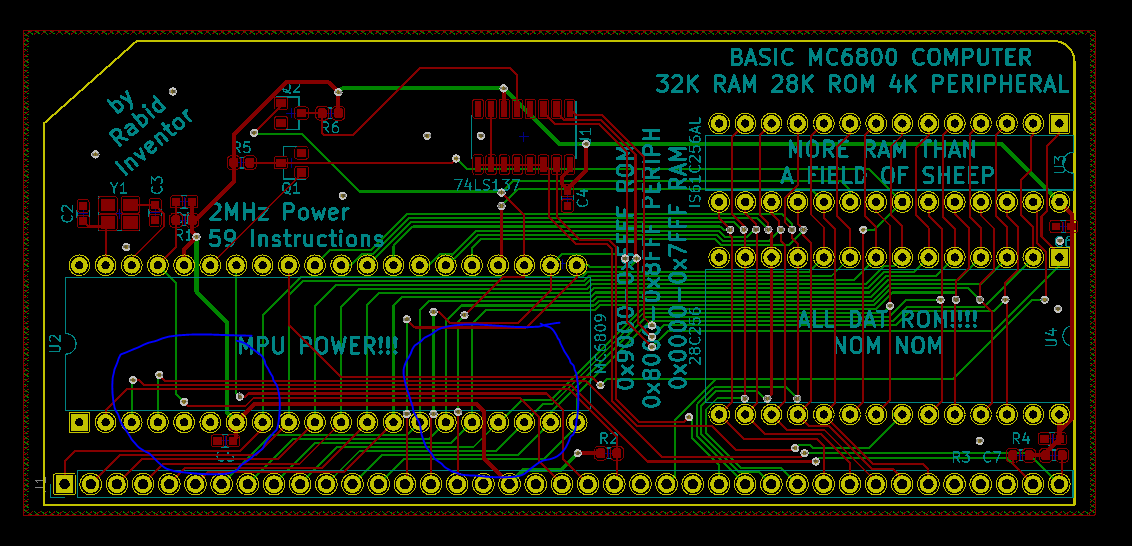

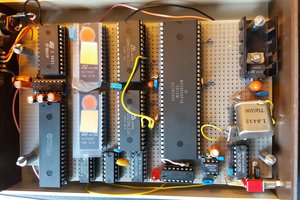

The board is going to be simple just enough to execute code so RAM, ROM and some simple glue logic.

Gee Bartlett

Gee Bartlett

Anders Nielsen

Anders Nielsen

Dave Collins

Dave Collins

Keith

Keith

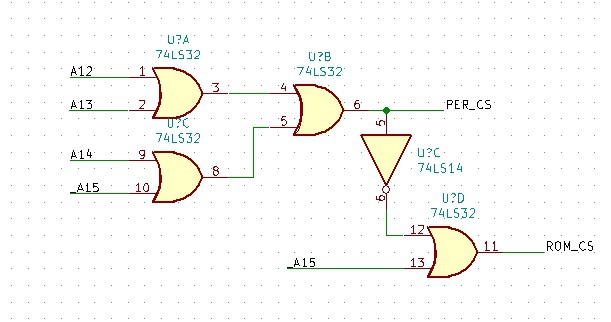

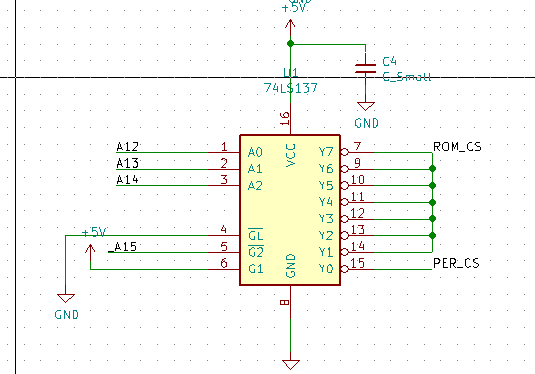

I asked myself the same question after I sent it off my first layout was going to use add gates for the peripheral select line which meant _A15 was used directly to the RAM select (when i had the memory map upside down). The LS137 wiring means i can cut between traces and patch of extra selects if i want them.

I have BSS138's laying about and freely available so just making FET inverters just seemed natural. i'll have another look at the enable logic.

This is really a live and learn project I highly suspect i will have plenty of bodging to do on this version. :)