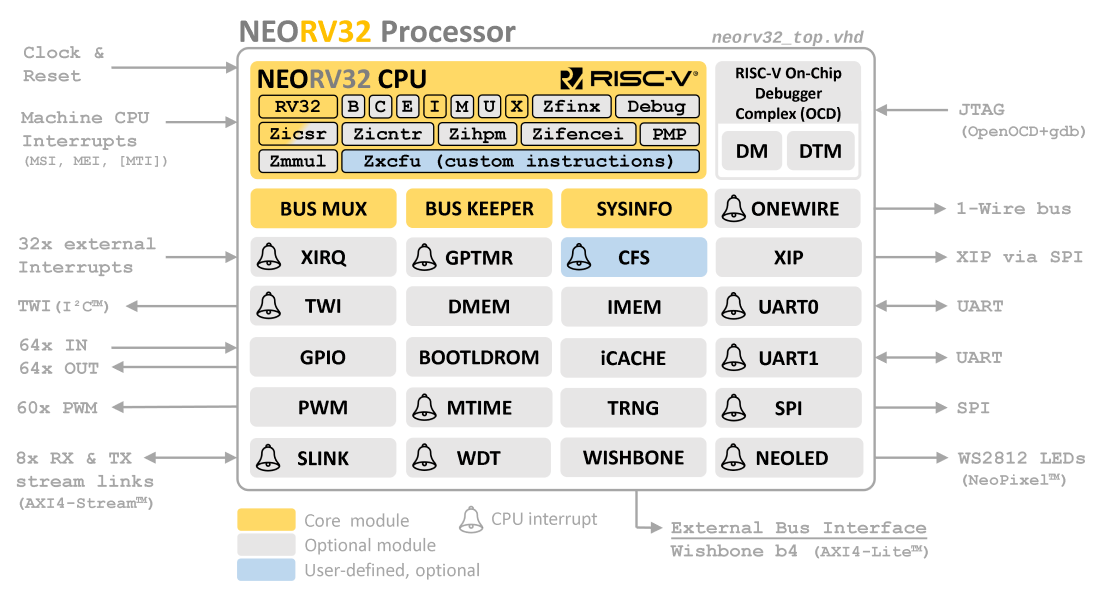

The NEORV32 Processor is a customizable microcontroller-like SoC based on the NEORV32 RISC-V-compatible CPU.

It is intended as auxiliary processor within larger SoC designs or as stand-alone custom microcontroller. The processor provides common peripherals like GPIO, serial interfaces, timers and embedded memories. All features beyond the base CPU are optional and can be configured via VHDL generics.

The project comes with a complete software ecosystem that features core libraries for high-level usage of the provided functions and peripherals, application makefiles , a run-time environment, several example programs and even Zephyr and freeRTOS ports.

The project is intended to work "out of the box " - just synthesize the provided test setup, upload it to the FPGA board of choice and start tinkering. Check out the project's rationale if you want to know more.

The project is hosted on GitHub. The project's change log can be found here. Join our chat on out gitter channel

Key Features

- online data sheet / documentation (based on asciidoc)

- online user guide (also based on asciidoc)

- online software documentation (based on doxgen)

- completely described in behavioral, platform-independent VHDL - no primitives, macros, attributes, etc.

- all-Verilog "version" available

- fully synchronous design, no latches, no gated clocks

- be as small as possible (while being as RISC-V-compliant as possible) – but with a reasonable size-performance trade-off (the processor has to fit in a Lattice iCE40 UltraPlus 5k low-power FPGA running at 22+ MHz)

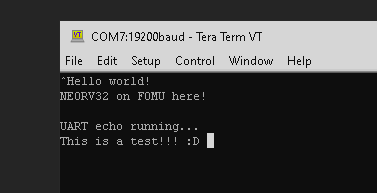

- from zero to printf("hello world!"); - completely open source and documented

- easy to use even for FPGA/RISC-V starters – intended to work out of the box

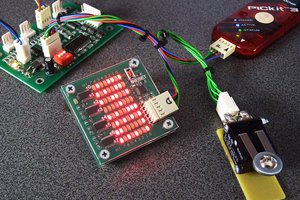

- tested on real hardware (Xilinx, Intel and Lattice FPGAs)

- upstream Zephyr RTOS support

- NEORV32 CPU: RISC-V-compliant rv32i CPU (passes the official RISC-V compliance tests) with optional extensions:

- B - bit-manipulation instructions

- C - compressed instructions (16-bit)

- I - base integer instruction set

- E - embedded register file (reduced register file size)

- M - integer multiplication and division hardware

- U - less-privileged user mode

- X - NEORV32-specific CPU extensions

- debug - CPU debug mode

- Zfinx - single-precision floating-point extension

- Zicsr - control & status registers (allows interrupts and exceptions)

- Zifencei - instruction stream synchronization (e.g. for self-modifying code)

- Zmmul - 32-bit integer multiplier (subset of M extension)

- Zxcfu - add custom RISC-V instructions

- PMP - physical memory protection

- HPM - hardware performance monitors

- Interrupts: RISC-V timer, software & external interrupts + 16 fast interrupts + 1 non-maskable interrupt

- NEORV32 Processor: Full-scale RISC-V microcontroller system / SoC with optional and configurable modules:

- embedded memories (instructions/data/bootloader, RAM/ROM) and caches

- timers (watch dog, RISC-V-compliant machine timer, general purpose timer)

- serial interfaces (SPI, TWI, UARTs, 1-Wire, ...)

- general purpose IO, PWM and IRQs

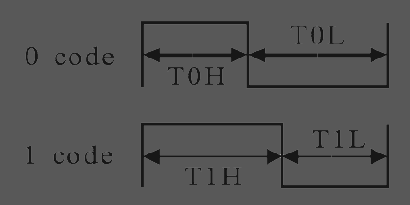

- dedicated NeoPixel(TM) LED interface

- external bus interface (Wishbone / AXI4-Lite)

- stream link interface (AXI4-Stream)

- external interrupt controller

- execute in place (XIP) module

- on-chip debugger with JTAG interface (compatible to OpenOCD and gdb)

- Software framework:

- core libraries for high-level usage of the provided functions and peripherals

- application compilation based on GNU makefiles

- GCC-based toolchain (pre-compiled toolchains available)

- bootloader and runtime environment

- several example programs including CoreMark benchmark

- doxygen-based documentation: available online on GitHub pages

- FreeRTOS port available

- Example setups for various FPGA boards to get you started

- Arty A7 (Xilinx Artix-7)

- UPduino (Lattice ice40 UltraPlus)

- DE0-nano (Intel Cyclone IV)

- open-source synthesis setup for UPduino based on GHDL, Yosys & nextPNR

- ...

Samuel A. Falvo II

Samuel A. Falvo II

Voja Antonic

Voja Antonic

Michael A. Morris

Michael A. Morris

Yann Guidon / YGDES

Yann Guidon / YGDES

Interesting project. From your Github page,

"This project is not affiliated with or endorsed by the Open Source Initiative (https://www.oshwa.org / https://opensource.org)." I notice it uses: BSD 3-Clause

I am curious if it is similar to http://solderpad.org/licenses/SHL-0.51/ from https://pulp-platform.org/