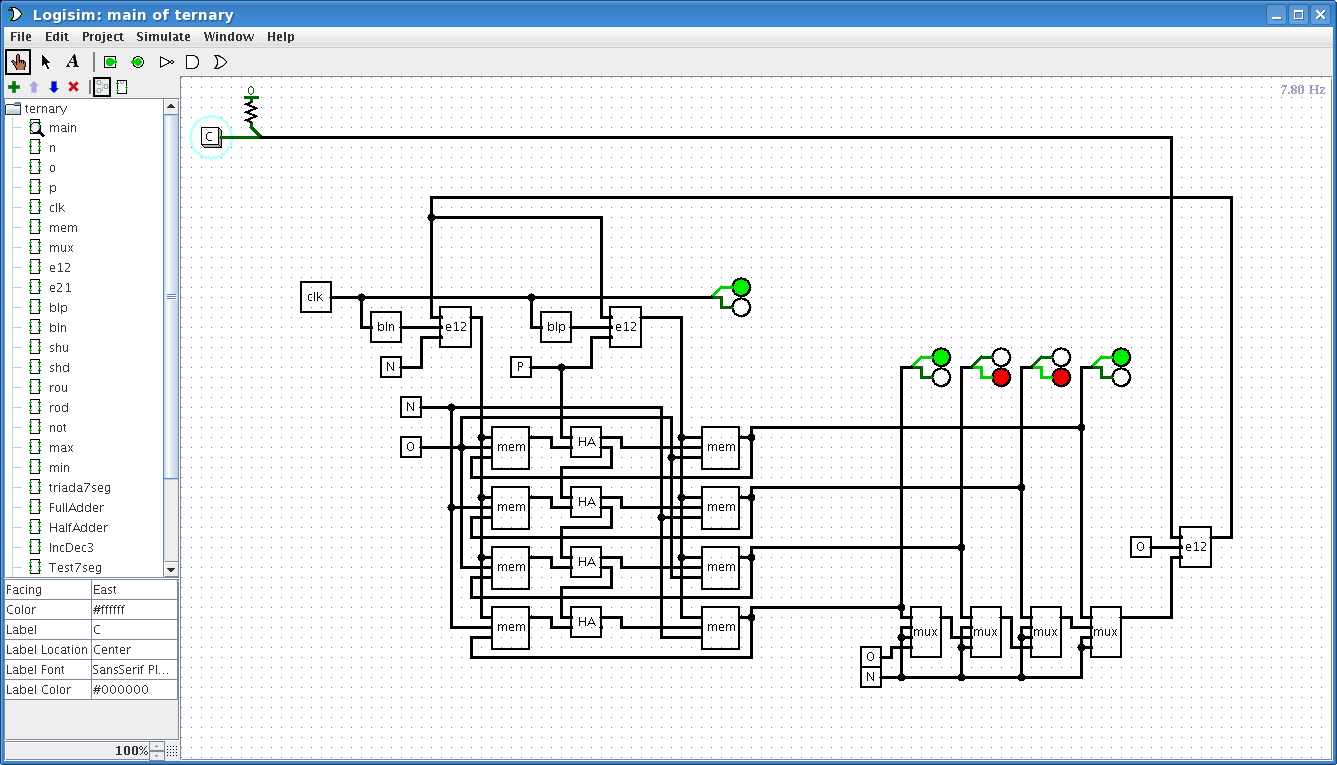

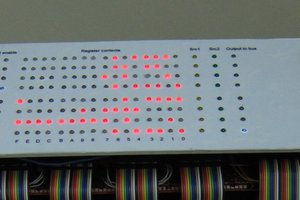

In this project we are trying to build a very simple but functional 3-trit balanced ternary computer. The only building block allowed is a ternary multiplexer based on DG403 analog switches.

══════════════════════════════════════════════════════════

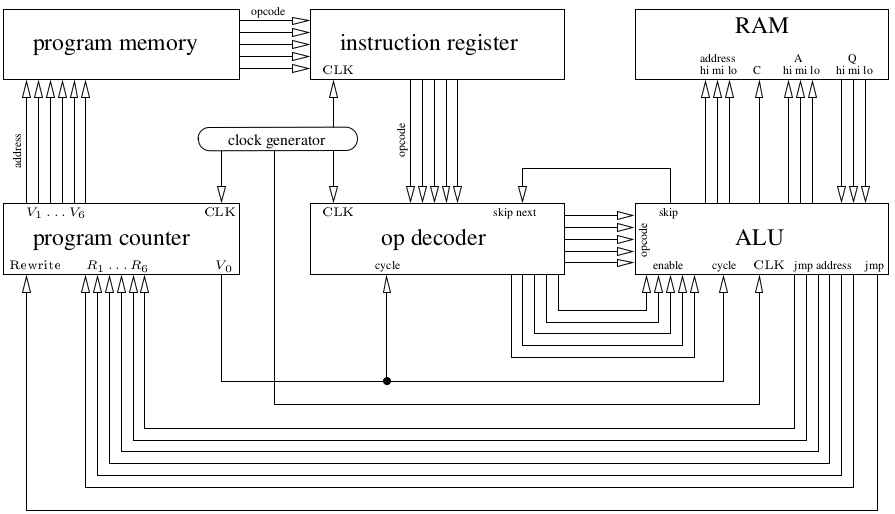

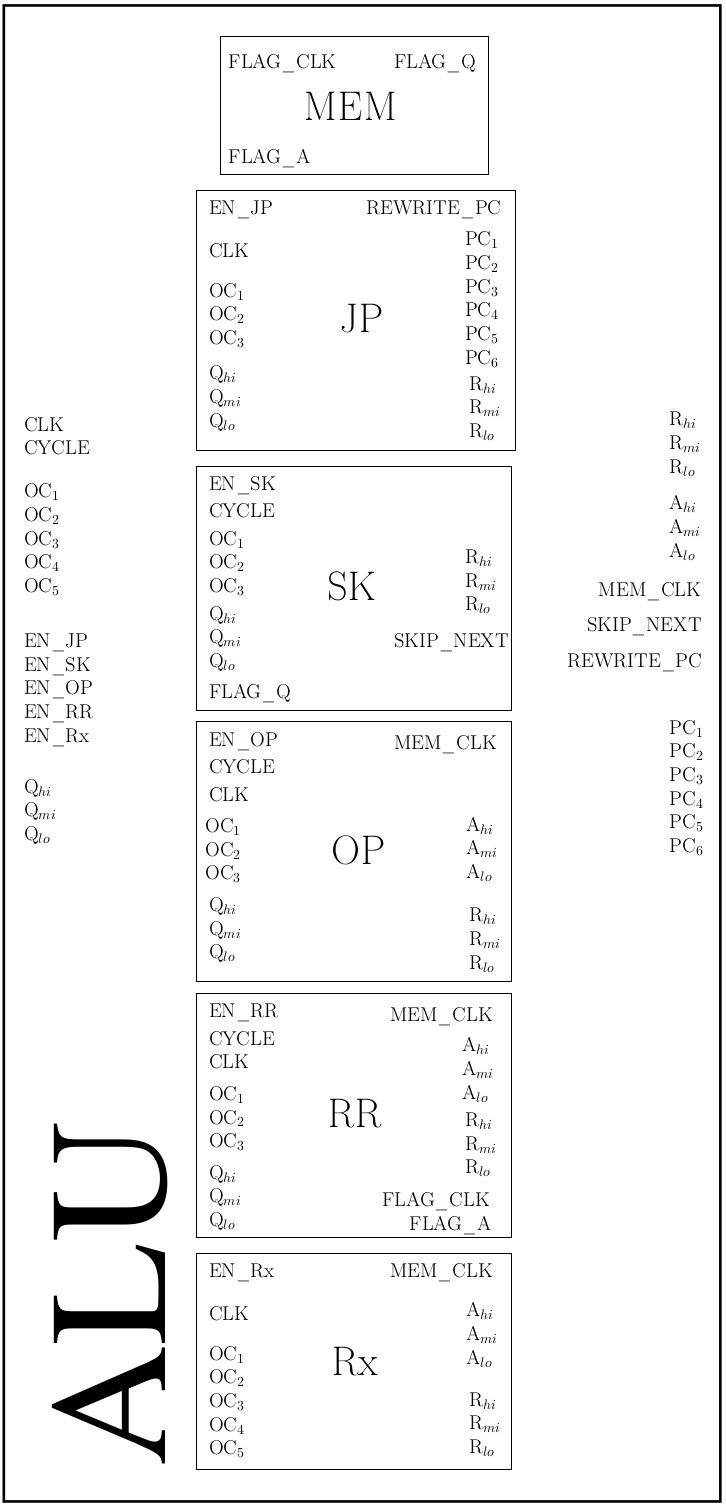

Description of the ternary computer TRIADOR

══════════════════════════════════════════════════════════

General purpose

registers

trits 2 1 0 (a trit can take -1,0,+1 values)

┌─┬─┬─┐

R1│ │ │ │ \

├─┼─┼─┤ | Program memory

R2│ │ │ │ | trits 4 3 2 1 0

├─┼─┼─┤ |-- main set ┌─┬─┬─┬─┬─┐

R3│ │ │ │ | of registers a -364│ │ │ │ │ │

├─┼─┼─┤ | d ├─┼─┼─┼─┼─┤

R4│ │ │ │ / d -363│ │ │ │ │ │

├─┼─┼─┤ r ├─┼─┼─┼─┼─┤

R5│ │ │ │ \ e -362│ │ │ │ │ │

├─┼─┼─┤ | s ├─┼─┼─┼─┼─┤

R6│ │ │ │ | s : : : : : :

├─┼─┼─┤ | ├─┼─┼─┼─┼─┤

R7│ │ │ │ | -1 │ │ │ │ │ │

├─┼─┼─┤ | ├─┼─┼─┼─┼─┤

R8│ │ │ │ | 0 │ │ │ │ │ │

├─┼─┼─┤ |-- extra registers ├─┼─┼─┼─┼─┤

R9│ │ │ │ | +1 │ │ │ │ │ │

├─┼─┼─┤ | ├─┼─┼─┼─┼─┤

R10│ │ │ │ | : : : : : :

├─┼─┼─┤ | ├─┼─┼─┼─┼─┤

R11│ │ │ │ | +363│ │ │ │ │ │

├─┼─┼─┤ | ├─┼─┼─┼─┼─┤

R12│ │ │ │ / +364│ │ │ │ │ │

├─┼─┼─┤ └─┴─┴─┴─┴─┘

R13│ │ │ │ Special register,

└─┴─┴─┘ specifies memory segment for JP ttt

┌─┬─┬─┬─┬─┬─┐

PC │ │ │ │ │ │ │ program counter register (-364..+364)

└─┴─┴─┴─┴─┴─┘

┌─┐

C │ │ borrow/carry flag (+1 borrow, -1 carry)

└─┘

Every 3-trit register can take values from -13 to +13:

t2*9 + t1*3 + t0

where t0,t1,t2 - trits (-1,0,+1)

═══════════════════════════════════════════════════════════

TRIADOR instruction set

═══════════════════════════════════════════════════════════

(for lisibility we use N,O,P instead of -1,0,+1)

┌───────┬────────┬───────────────────────────────────────┐

│op code│mnemonic│ description │

├───────┼────────┼───────────────────────────────────────┤

│ NNttt │ EX ttt │ extension commands (work in progress) │

├───────┼────────┼───────────────────────────────────────┤

│ NOttt │ JP ttt │ unconditional jump to R13*27+ttt │

├───────┼────────┼───────────────────────────────────────┤

│ NPttt │ SK ttt │ conditional skips of the next command │

├───────┼────────┼───────────────────────────────────────┤

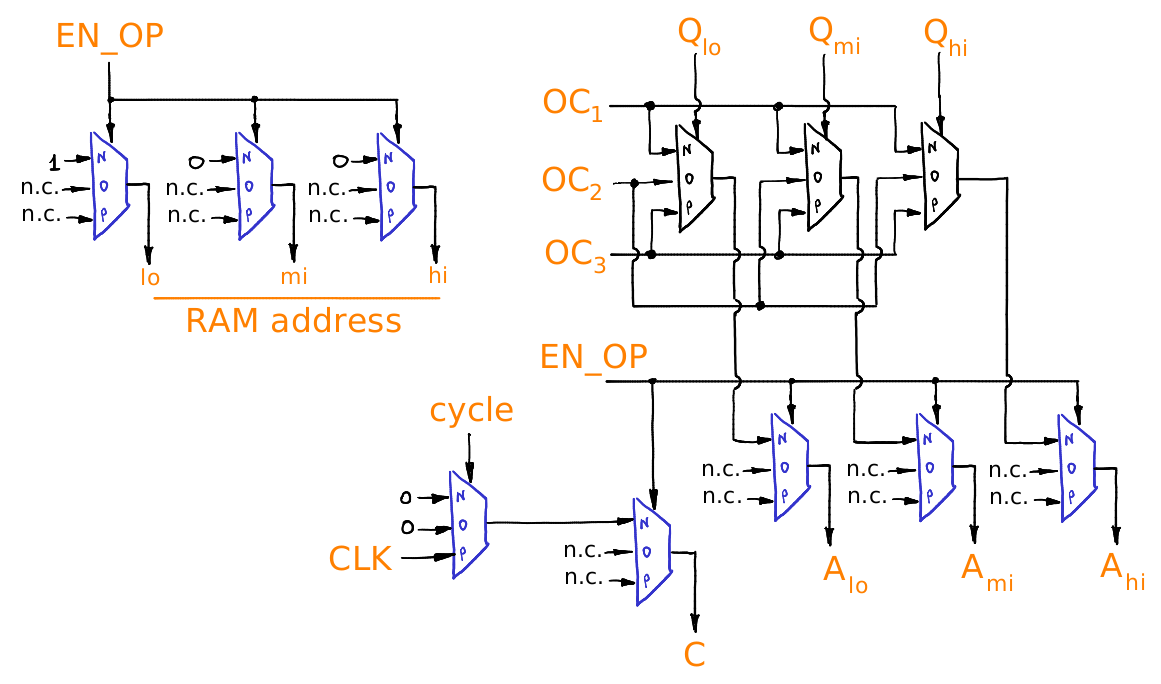

│ ONttt │ OP ttt │ tritwise unary operation over R1 │

├───────┼────────┼───────────────────────────────────────┤

│ OOttt │ RR ttt │ copying between registers │

├───────┼────────┼───────────────────────────────────────┤

│ OPttt │ R1 ttt │ write ttt to the register R1 │

├───────┼────────┼───────────────────────────────────────┤

│ PNttt │ R2 ttt │ write ttt to the register R2 │

├───────┼────────┼───────────────────────────────────────┤

│ POttt │ R3 ttt │ write ttt to the register R3 │

├───────┼────────┼───────────────────────────────────────┤

│ PPttt │ R4 ttt │ write ttt to the register R4 │

└───────┴────────┴───────────────────────────────────────┘

Additional comments:

- ttt means a 3-trit number with values

from NNN (-13) to PPP (+13)

- RR ttt instruction copies a register to/from R1 or performs

an increment/decrement over R1

OONNN — copy R1 to R13

OONNO — copy R1 to R12

OONNP — copy R1 to R11

OONON — copy R1 to R10

OONOO — copy R1 to R9

OONOP...

Read more »

Dmitry V. Sokolov

Dmitry V. Sokolov

So we need to have ONE DG403 per every binary represented TRIT and it doesn't matter if it's input or output, but number of inputs should be multiple by 2 in order to use DG403 chips optimally.

So we need to have ONE DG403 per every binary represented TRIT and it doesn't matter if it's input or output, but number of inputs should be multiple by 2 in order to use DG403 chips optimally.

Artem Kashkanov

Artem Kashkanov

spudfishScott

spudfishScott

Pavel

Pavel

zpekic

zpekic

Hello. Your project seems interesting but dg403 is so expensive and is not easy to find.

I don't know much about Electronics but perhaps they can be replaced with 4016? 300 of them have enough analogue switches and the price will be reduced a LOT.