-

42 Years Experiencing Life, The Universe and Game Development

11/01/2023 at 22:27 • 0 commentsAs of October 2023 I have retired from a long and rewarding 42 year career in game development (mostly engineering and programming).

I count myself as having been very lucky to have had such an interesting and successful career as well as being able to experience first hand the game industry changing and growing through several "eras". I got a phone call at the age of 17 (they called me) asking if I wanted to program video games for a living, and I never looked back (they also offered to drive me to/from work, since I had no car yet). My first full-time game development job (or any job) was on the Atari 2600 in 1981, using MP/M as a development system (and with reverse engineered documentation and a 6502 in-circuit emulator device).

Ever since I discovered electronics and eventually computers, I have been fascinated by them and drawn to learn more about them. There is always more to learn, and game development was really great for new systems and challenges every few years. Computers are the closest thing to "magic" I have found - with the ability to turn time and an idea into something "real" (and get paid to do it).

The game industry has gotten so successful, that games and games teams are now large, complex and specialized (and generally getting even larger and more specialized). While this is exciting and amazing games are being created, I miss the challenge of creating something with a small team and technical limitations which can help to "encourage" creativity (and not be as concerned with "marketability"). Bottom line is I just haven't been able to "creatively hack" on code and technology as much as I would like to doing modern game development (the stakes are too high).

That said, Mass Media/2K is stronger than ever within 2K Games and I believe has a very bright future ahead.

In recent years as a hobby, I have been having a lot of fun with small "retro computer" and "neo-retro" projects (using hardware, software and FPGAs) and now I hope to be able to focus more time on that (stay tuned). I am still somewhat young (at least for someone retiring, since I started young) and in reasonably good health, so I hope I might have some years of quality hacking ahead of me.

-XarkHere is a summary of my 42 year game development career:

1981-1985 McToy/MCT

Mostly contract game development for Sega (Buck Rogers, Mt. Dew Tapper etc.). Also did some work on embedded electronics and pre-release Amiga computer.1985-1989 Datasoft/IntelliCreations (later Software Toolworks)

- Worked on Alternate Reality: The City and co-designed/developed Alternate Reality: The Dungeon (and other games)

1989-1990 Micro-Illusions

- Worked on various (mostly) Amiga games and tools

1990-1991 Cinemaware

- Worked on game engine code for Amiga, PC and others. Started on CD-i development.

1991-1995 Philips Interactive/POV Entertainment Group

- Worked on numerous CD-i titles (Voyeur, Zombie Dinos, Thunder in Paradise etc.) and engine/technology development.

1995-1996 Time Warner Interactive

- PC games (3D Table Sports) and tools

1996-2007 Mass Media Inc.

- Numerous games for a large number of systems (starting with Starcraft conversion for Nintendo 64)

2007-2011 Mass Media/THQ (studio purchased by THQ)

- Worked on numerous THQ titles, including Saints Row 1/2, Darksiders, Space Marine etc.

2011-2018 Mass Media Games (studio went private again after THQ closure)

- Jak and Daxter Collection (PS3...

Read more » -

Upduino 3.0 - Third Time Appears to be the Charm

07/12/2020 at 05:37 • 5 commentsRecently, I have been working with the iCE40UP5K FPGA on my Xosera video project for the rosco_m68k. My main development board for this project has been the iCEBreaker FPGA board from 1BitSquared (which is an excellent board). However, I also wanted to support a lower cost, smaller board that might be more suitable for "embedding" in the video project, so I was also planning to support the Upduino FPGA board that uses the same FPGA (which is fully supported by the open-source FPGA toolchain).

Frustratingly, I found that my design which worked fine on the iCEBreaker wasn't working at all on the Upduino (with appropriate I/O pin changes etc.). After some debugging, I determined that the PLL was having issues (the "PLL lock" signal would not stay on reliably indicating the PLL was "not happy"). A short time after discovering this issue I found this article on the (current) Upduino 2.1 maker's blog which seemed to explain my trouble: Ground trampolines and Phase Locked Loops (basically design flaws in the Upduino 2.x board keep the PLL from operating reliably).

The original Upduino 1.0 board was pretty amazing when it came out for $9.99, however it had some issues with how it was shipped and it was inconvenient to use (with no JTAG or external oscillator) and also poor electrical design. A while later, the design was updated to the Upduino 2.0 which had FTDI JTAG (and 12Mhz oscillator) added and a few other features. This was a nice improvement, but apparently this board also had a very poor electrical design (rumored to be designed by a student).

While hanging out on the rosco_m68k Discord, working on my video project Xosera, I met another 68K and FPGA enthusiast Claude. We had some discussions about FPGA video, and the Upduino FPGA board and it's issues (he was aware of the PLL issues and had improved his board with some "user modifications"). He was also playing around with some FPGA video projects and posted an amazing DVI hack he did on Twitter showing the iCE40UP5K directly outputting DVI video using an Upduino 2.0 FPGA board. This was enough to get the attention of the current Upduno 2.1 maker

Venkat took over the Upduino project from the creator and has been selling the Upduino 2.1 on Tindie (which was however, using the same flawed 2.0 electrical design). When he first took over, he sent an invite to buyers inviting them to fill out a survey to see how Upduino could be improved in an upcoming version. He seems to have done everything possible to accommodate everyones wishes where possible with Upduino 3.0 (as well as addressing the underlying electrical design issues).

Copying from the Upduino 3.0 GitHub wiki and Tindie page, here are some improvements over Upduino 2.x:

- Board:

- Lattice UltraPlus ICE40UP5K FPGA with 5.3K LUTs, 1Mb SPRAM, 120Kb DPRAM, 8 Multipliers

- 4 layer board, solid ground plane, dedicated power layer for 3.3V and 1.2V distribution

- All FPGA pins including LED driver pins are brought to 0.1" headers

- Any optional bridges must be done using special bridge-type footprint instead of resistors to make modification easy

- All passives to be no smaller than 0603 footprint

- Fix silkscreen so its easy to read, add Pb Free, WEEE symbol, "Made in USA"

- Move Micro USB connector inboard a little bit to allow clean depanelization

- Open source schematic and layout using KiCAD design tools

- Power

- Dedicated power and ground planes

- Minimum of 10uF bulk capacitance on all power rails: USB, 3.3V, 1.2V

- Dedicated decoupling capacitance on each FPGA pin placed close the FPGA pin

- Power decoupling per FTDI recommendations (using ferrite beads)

- Change LDO's to be smaller parts, capable of 200mA max output

- Oscillator: ...

- Board:

-

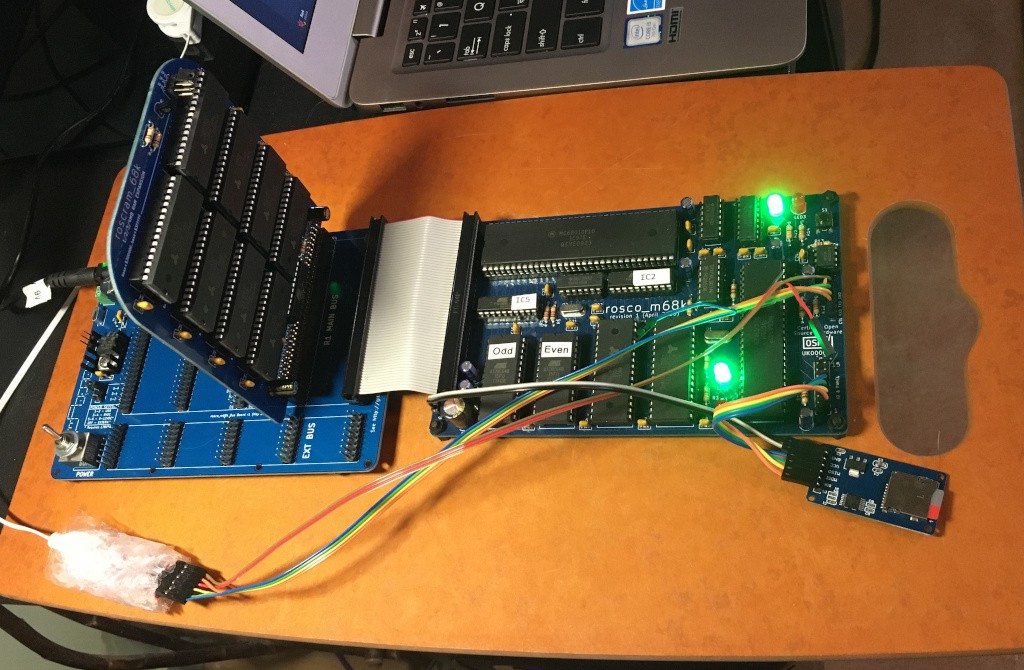

Enjoying Some 68k Retro Fun with Rosco_m68k

07/05/2020 at 22:57 • 0 commentsWith some extra "stay at home" time on my hands, I was looking around for a retro project to work on (and have some fun by learning something). While I enjoy 8-bit CPUs and there are a lot of great 8-bit 6502 and Z-80 (and other) retro system projects on HaD and around the Internet, I haven't seen as many 16-bit ones - especially 68000 family. However, one that did catch my eye was the rosco_m68k project by @Ross Bamford.

I have a lot of affection for the 68000 microprocessor family, going back a long time. I think it started way back when I read this 1980 Kilobaud Microcomputing magazine article about "16-bit Super Processors" (and even as a kid reading this, the 68000 seemed "clearly superior" to me). I also had the good fortune to have a preliminary edition of the "Motorola 68000 16-bit Microprocessor User's Manual" (with the black cover) "fall into my hands" in 1980 - which turned out to be somewhat life-changing (during a car ride from a friends father, who owned an early computer company, he had a copy lying on the back seat next to me - and when I asked about it, he gave it to me). I studied that manual for years and learned a lot about the 68000 and computers in general before I ever got my hands on an actual 68K CPU (the first was a 68008 card for an Apple II, but then later on I was an early Amiga developer etc.).

After following the rosco_m68k project for a while, I decided to jump in and purchased a kit from Tindie and joined the Discord chat server (which has been quite friendly).

So far it has been a fun experience. Within the first week or so of hanging out on the rosco_m68k Discord chat server (while waiting for my kit to arrive) there were several good discussions. In fact, one discussion has led me to start my own little hardware project for use with rosco_m68k ("Xosera" - I'll have more on that with a project post soon).

When my rosco_m68k kit arrived, I found it to be straightforward and enjoyable to assemble. Ross has done a nice job making it easy (and he has been good about "tweaking" things based on feedback, so I found it pretty "smooth"). Since I was a bit too impatient to get started, I didn't even notice the link to his instructions (and it still was no problem - with PCB clearly marked, a "chip map", labelled chips where needed and even labelled resistors - so no need for "color-code" decoding). It booted up for me on the "first-try".

![]()

Since then, I have installed the 68k-toolchain and have been able to build and run the examples on GitHub.

For fun, I ported an old version of the Drystone benchmark to rosco_m68k (and the hard part there was mostly getting GCC to compile the ancient C code, not the rosco_m68k). Rosco looks pretty good when benchmarked next to other classic 68k machines (and I hear rumors of a blazing 10MHz...).

At this point my rosco_m68k system has grown a bit, with SD card storage (and development firmware for it), a backplane and 4MB RAM expansion (so 5MB total). I also have a V9958 VDP video board kit on its way as I write this.

Pretty soon, it looks like I'll be ready to write a little 68k game or "demoscene" demo. 😅

Projects I Contribute To

My Pages

Projects I Like & Follow

Share this profile

ShareBits

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.

Thank you for your interest in my Sol-20 Reproduction project.

Hi Xark, thank you for liking and following the #Kobold K2 - RISC TTL Computer !

Hi! Thanks for the follow of the Kestrel Computer Project. Appreciate it!

Hi Xark, thank for following and liking the One Square Inch TTL CPU, https://hackaday.io/project/161251-1-square-inch-ttl-cpu !

Thanks for following our #OPC-5 - a CPU for FPGA, in one page project!

+1. several Arduino style boards including a GamDuino (FPGA). Then many FPGA / CPLD development boards some of which I have like the Papilio and some of the breakouts.

The Papilio one (Xilinx 3E or 3A) along with the LogicStart MegaWing was my entry into VHDL.

What do you use (Xark) ... VHDL or Verilog ??

Thanks again! This time for the follow and for the skull in my Paddles project.

Thanks for the LiFePO4wered/USB skull and sharing your project using it! Love to see real world uses.

Thanks for following uRADMonitor! One of my other projects was semifinalist in last year's Hackaday prize, check it out here: https://hackaday.io/project/1662-global-radiation-monitoring-network

Thank you. I am a long time MIPS fan, and so I am interested in PIC32. I have a few PIC32 chips, but haven't worked with them much.

Xark

Xark Jasmine Brackett

Jasmine Brackett Ross Bamford

Ross Bamford Luke Valenty

Luke Valenty Valentin Angelovski

Valentin Angelovski

Anders Nielsen

Anders Nielsen Lutetium

Lutetium MagicWolfi

MagicWolfi John

John Michael Gardi

Michael Gardi KJoh

KJoh Ted Fried

Ted Fried zpekic

zpekic TinLethax

TinLethax Tom

Tom cprossu

cprossu Flavio

Flavio SHAOS

SHAOS

Thanks for your continued interest in my work.