-

OSHWA: How We Made the Open Hardware Summit All Virtual in Less Than a Week

03/20/2020 at 13:39 • 0 commentsFrom OSHWA president Michael Weinberg:

![Screen-Shot-2020-03-17-at-3.40.05-PM]()

How We Made the Open Hardware Summit All Virtual in Less Than a Week

First, thank you again to everyone – speakers, participants, and sponsors – for a fantastic 10th anniversary Open Hardware Summit. We knew the 10th anniversary Summit would be one for the ages, although we didn’t quite expect it to be because it became the first virtual Summit.

Thanks to the timing of the Summit, the 10th anniversary Summit ended up being many people’s first virtual summit of the Covid-19 era (that includes the organizers). Unfortunately it looks like it is unlikely to be the last. In the hopes of helping event organizers struggling with the same challenges, this blog post outlines the decisions we made and the steps we took to make it happen.Quick Context

The Open Hardware Summit is an annual gathering of the open source hardware community held by the Open Source Hardware Association (OSHWA). This year OSHWA partnered with the Engelberg Center on Innovation Law & Policy at NYU Law to host the event in New York City. The event usually brings together hundreds of community members and speakers from around the world. It was scheduled for March 13, 2020.

While the situation has been evolving for some time, as recently as March 5th (8 days before the Summit) we thought that holding a reduced in-person version of the event was the right decision. By March 8 (5 days before the Summit) that was no longer tenable and we announced that the Summit was going all virtual. That was the right decision, but what does going all virtual mean?Priorities

We had two major priorities for the virtual Summit:- Online streaming video of all of the speakers and panels.

- A community space for discussions and coming together.

Video

The live stream of the Summit had to be both accessible to our viewers and easy to join for our speakers and panelists. After considering some options and consulting with experts in our community (huge thank you to Phil Torrone at Adafruit for the guidance), we concluded that a combination of YouTube and StreamYard would be the best option.

YouTube worked for our community because it is easily accessible on a wide range of platforms in most of the world. That meant that just about everyone would be able to see the Summit from wherever they were.

StreamYard made it easy to manage the backend. Speakers could join a virtual green room before their talk and our technical testing the day before the Summit made it clear that it was easy for them to share their slide presentations as well. One of the members of the Summit team was able to easily add and remove people (and their screens) to the live feed, along with stills and slides for introductions, sponsors, and everything else.

Read more »Community Space

We also looked at a number of options for online discussions. We decided that a discord server would be the best option for the open source hardware community. Discord allowed us to open the space to anyone who wanted to join, while at the same time giving us moderation control over the discussion (huge thank you for Lenore Edman from Evil Mad Scientist Laboratories for jumping in as a moderator). Many community members were already comfortable with discord, which was also a bonus.

We also decided to use discord for a version of Q&A for the speakers. One option would have been to try and integrate video questions from the audience into the live stream. That would have been technically possible with StreamYard (probably…), but it seemed like an unnecessary logistical complication for the organizers. As an alternative we decided to set up separate discord channels for each of the speakers. That allowed the speakers to end their talk and move to their discord channel for further discussions.

One unexpected and welcome development was that the discord server grew into a larger... -

How to join the virtual Open Hardware Summit

03/12/2020 at 09:21 • 0 comments![]()

Due to the COVID-19 virus, the Open Hardware Summit has been moved from NYC to cyberspace!

2020.oshwa.org

- The livestream link will be updated here on the day of the Summit (13th March 2020). The event will be running in EST (New York) time zone.

- For Q&A/discussions, please join the OHS discord server: https://discord.gg/38C57Uf

- Follow OHSummit on Twitter and use hashtag #ohs2020Virtual

- The link to sign up for OSHWA email updates: http://eepurl.com/gVRYVz

- The link for the open hardware survey: https://nyu.qualtrics.com/jfe/form/SV_cGDMjnMBVtDqHXL

- The link to 2021 tickets: https://www.eventbrite.com/e/open-hardware-summit-2021-tickets-99408361084

-

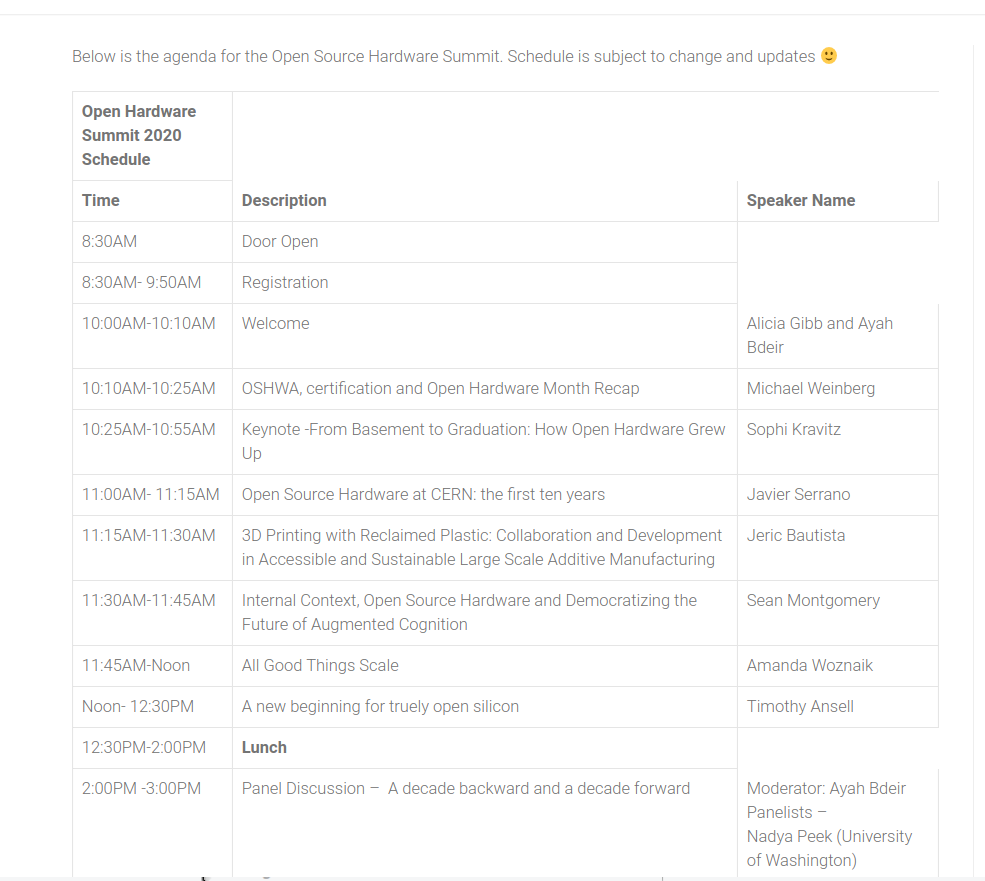

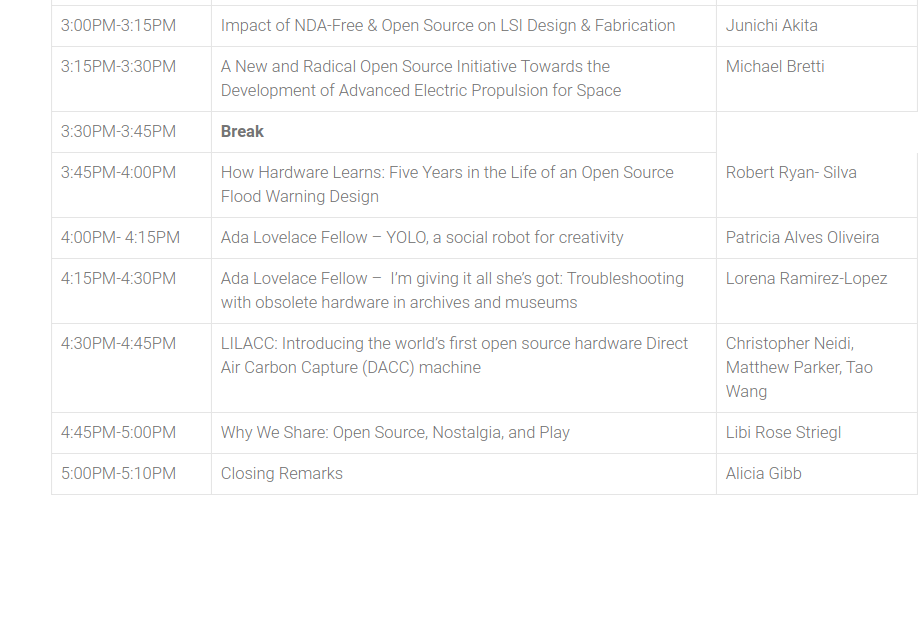

Open Hardware Summit 2020 schedule

02/18/2020 at 12:09 • 0 comments![]()

Here is the exciting schedule for the Open Hardware Summit on March 13th in NYC:

![]()

![]()

Be sure to buy tickets before they are sold out!

![]()

Project Lists

Projects I Contribute To

My Pages

Projects I Like & Follow

Bits

Awesome! Thanks for letting us know about the project. -Drew Fustini

Hi, we fabricated our PCB's from OSHPark for the first time. We are so happy with the service. Do have a look at our Project 'NeuroCuddl' https://hackaday.io/project/106571-neurocuddl

Thanks for helping me getting back into the sports after more than 2 decades of not making PCBs! You guys rock!

Thanks for the like! After all great quality boards result in great projects :)

That is great to hear! We are inspired by the projects our customers build! 😊

Always great to get an OSH Park follow, thanks for liking my MAX32660 Motion Co-Processor project!

Thanks for following Wheeled Walker Hybrid Bot! also I love those purple boards!

Thanks for following. Can’t wait to get a set of my purple project boards in the mail within the next couple of months!

We're always excited to see what new projects you are designing

Sometimes the most interesting ones can't be shared...too bad :<

Thanks for liking and following #Arcus-3D-P1 - PnP for 3D printers

Now, something to populate those Perfect Purple PCBs. :)

Thanks for following the #Muffsy Stereo Relay Input Selector

Hey OSH, thanks for following #CirKit ... Awesome :-D

I'm just fiddling with it at the moment, I have other more pressing concerns but I'm happy to share the love for purple PCBs with everyone.

I'm considering calling the final program GOSH, with your permission? It is rebuilt with your awesome service in mind... ;-)

Awesome, and thanks for the like as well. Much appreciated :-D

Thank you for liking and following my project #Arcus-3D-C1 - Cable 3D printer

I'm sure it will have something perfect and purple in it eventually.

Awesome, please email drew@oshpark.com when you are ready to get a board made.

Thank you for following my project #Green Traffic Light Reminder (anti-honking)

oshpark

oshpark Benchoff

Benchoff Tindie

Tindie Lutetium

Lutetium AVR

AVR Anool Mahidharia

Anool Mahidharia Sophi Kravitz

Sophi Kravitz

Deepak Khatri

Deepak Khatri Riccardo Pittini

Riccardo Pittini SdtElectronics

SdtElectronics Capt. Flatus O'Flaherty ☠

Capt. Flatus O'Flaherty ☠ CaptMcAllister

CaptMcAllister Zapp

Zapp Daren Schwenke

Daren Schwenke Kris Winer

Kris Winer Philip

Philip Martin Held

Martin Held Sam Ettinger

Sam Ettinger greg

greg Alpenglow Industries

Alpenglow Industries Lex Kravitz

Lex Kravitz Angela Sheehan

Angela Sheehan morgan

morgan

Nice, clean wood housing epoch clock, using Oshpark board: https://hackaday.io/project/161257-gpsclock